# OETTLE & REICHLER

Adalbert-Stifter-Str. 40, 8902 Neusaess, Tel.: (0821) 48 18 80

## BYTE - WIDE - KARTE

Anschlusstips fuer

alle Anwender

- 1) Die Interrupt Enable Kette (IEI, IEO) und die Bus Acknowledge Kette (BAI, BAO) wurde durchgeschleift.

- 2) Das Power Fail Signal (23a) muss waehrend des normalen Betriebs auf High Pegel liegen oder unbeschaltet bleiben.

- 3) Anschluss 21a muss auf High Pegel liegen oder unbeschaltet bleiben. Eventuell vom BUS abtrennen.

- 4) DESLCT = Low deaktiviert ausschliesslich den Datentreiber IC 7

- 5) WAITS werden nur ausgegeben, wenn einer der Speicher M00 - M07 angesprochen wird. Bei Fassung M08 wird kein WAIT generiert.

ECB - BUS Anwender

- 1) Anschlussbelegung von A16 - A19 beachten.

- 2) Anschlussbelegung von DESLCT beachten.

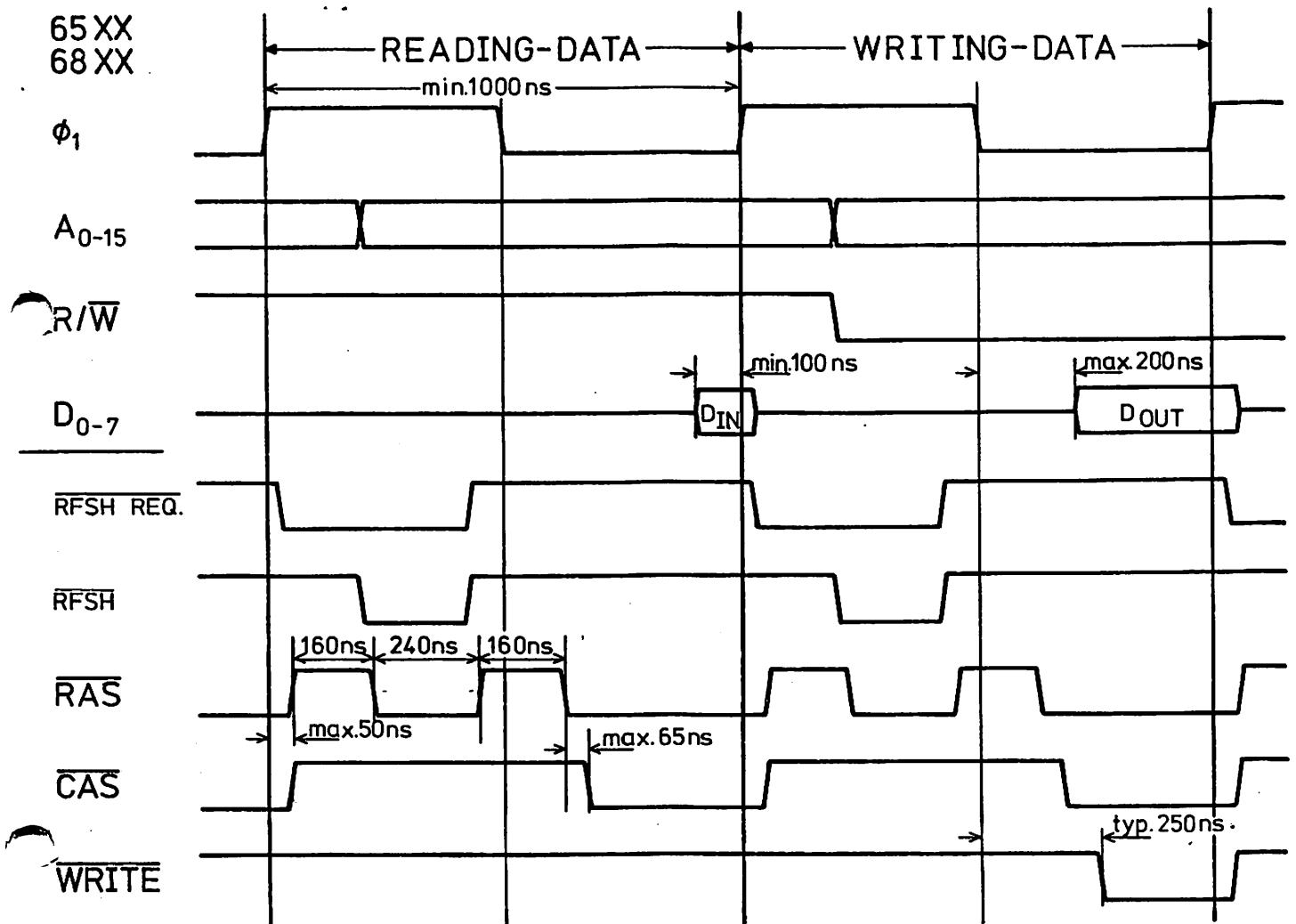

6800, 6809 und 6502 Besitzer

1) Es gibt zwei Beschaltungsmoeglichkeiten:

1, a, Anschluss 30c = Low

b, Anschluss 24c =  $\emptyset$  1 oder  $\emptyset$  2 oder  $\overline{E}$  (6809)

Diese Beschaltung empfiehlt sich insbesondere bei Verwendung von langsamem Speichern. Dadurch wird erreicht, dass das CE Signal der Speicher immer aktiv (Low) ist. Ein Speicherzugriff wird damit bereits mit dem gueltig werden der Adressen eingeleitet und nicht erst mit der fallenden Flanke von  $\emptyset$  1 oder  $\emptyset$  2 oder  $\overline{E}$ .

2, a, Anschluss 30c =  $\emptyset$  1 oder  $\emptyset$  2 oder  $\overline{E}$  (6809)

b, Anschluss 24c = Low

Ist die Zugriffszeit der Speicher fuer die Systemfrequenz ausreichend, empfiehlt sich diese Beschaltung, da eine niedrigere Verlustleistung der Speicher erzielt wird.

2) Anschluss 22c muss mit dem R/W Signal verbunden werden

3) Anschluss 28a ist mit +5V (6502) oder VMA (6800) oder  $\overline{Q}$  (6809) zu beschalten.

4) Macht es die Zugriffszeit der Speicher notwendig Waits (HALT, READY) an die CPU auszugeben, so ist Anschluss 29c mit  $\emptyset$  1 oder  $\emptyset$  2 oder  $\overline{E}$  (6809) zu verbinden. Zudem ist Beschaltungsmoeglichkeit Nr. 1 (siehe oben) zu waehlen. Anschluss 10a (WAIT) ist mit READY (6502) bzw HALT (6800, 6809) zu verbinden.

# OETTLE & REICHLER

Adalbert-Stifter-Str. 40, 8902 Neusaess, Tel.: (0821) 48 18 80

---

## BYTE - WIDE - KARTE

### Keine Akkuschaltung

Hierbei entfallen folgende Bauteile:

NiCd 0-2 Varta 100 DKO-F

IC 03 ICL 7665 CPA

IC 03 ist durch eine Bruecke von Pin 1 nach Pin 4 zu ersetzen.

### Keine 1M-Byte Dekodierung

Sind im System die Adressen A16 - A19 nicht vorhanden und soll nur in einer 64 K-Byte Page gearbeitet werden, Kann IC 04 entfallen. Als Ersatz dient eine Bruecke von Pin 6 nach Pin 16.

### Keine Waitschaltung

Ist es nicht notwendig WAITS an das System auszugeben, Kann IC 00 ersatzlos entfallen.

### PROM

Es existieren derzeit 3 Prom Versionen fuer folgende Prozessoren:

BW1-Z-80 fuer Z-80

BW1-808X fuer 8080 und 8085

BW1-6X0X fuer 6502, 6800 und 6809

Wir bitten beim Erhalt des Bausatzes oder der Fertigplatine zu ueberpruefen ob der Prom fuer Ihren Prozessor ausgelegt ist.

PROMs fuer andere Prozessoren sind auf Anfrage erhaeltlich.

### Technische Daten

Abmessungen : 100 x 160 mm (Europakarte)

Busstecker : 64 polig, a+c belegt

Busnorm : ECB - BUS

Fan in : 1 TTL LS Last

Stromaufnahme : +5V typ. 250 mA

Zugriffszeit : gerechnet von fallender Flanke an Anschluss

30c, oder gueltig werden der Adressen.

typ.: 45 ns + Speicherzugriffszeit typ.

max.: 80 ns + Speicherzugriffszeit max.

Banking : max. 1 M-Byte dekodierbar (A16 - A19)

Deselect : ueber Eingang 26a

Stromaufnahme der Schreibschutz Schaltung bei

Data Retention : typ.: 3 uA

OETTLE & REICHLER

Adalbert-Stifter-Str. 40, 8902 Neusaess, Tel.: (0821) 48 18 86

## ELEKTRONIK - ENTWICKLUNG

F. Oettle, A.-Stifter-Str. 40, 8902 Neusaess, Tel.:(0821) 481880

T. Reichler, Manlichstr. 7a, 8900 Augsburg, Tel.:(0821) 414947

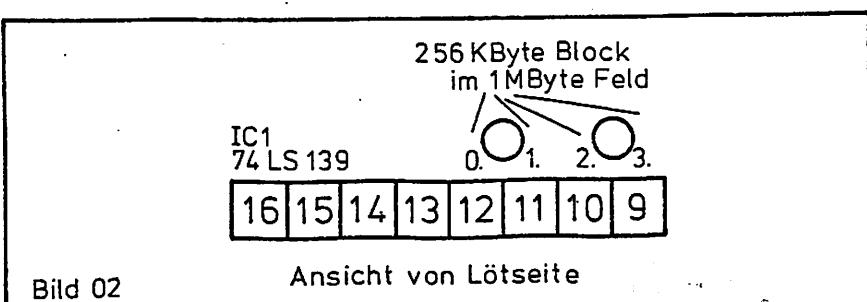

ECB/D - 256

## 256-KByte-RAM-Karte

## für 8080, 8085 und Z-80 Systeme

- + quasi-staticischer Betrieb durch Refresh-Controller auf der Karte

- + dadurch unbegrenzte DMA-, WAIT- und RESET-Zyklen möglich

- + maximale Systemfrequenz 5 MHz, Option 6 MHz

- + RAM-DESELECT von beliebigen 1-KByte Bereichen

- + externe Ausblendung über OUTPUT BUFFER DISABLE

- + ausbaufähig in vier Schritten von 64 KByte bis 256 KByte

- + erweiterbar bis 1-MByte (A 16 - A 19)

- + nur eine +5V Versorgungsspannung

- + ECB-BUS Kompatible Einfach-Europakarte

## Produktübersicht

Dem Trend nach immer leistungsfähigeren Microcomputersystemen und damit in erster Linie immer größeren Speichermedien folgend wurde die ECB/D 256 mit einer maximalen Kapazität von 256 KByte ausgelegt. So läßt sich die Karte z.B. in Verbindung mit einem geeigneten Betriebssystem als extrem schnelles Diskettenlaufwerk ansprechen. Hierbei ergeben sich gegenüber einem mechanischen Laufwerk ca. 50 mal schnellere Datenübertragungsraten. Damit werden vor allem diejenigen Anwender ange- sprochen die bereits über ein Memory Management (z.B.: Banking) verfügen, oder sich die Option eines späteren Ausbaus über 64 KByte offen halten wollen.

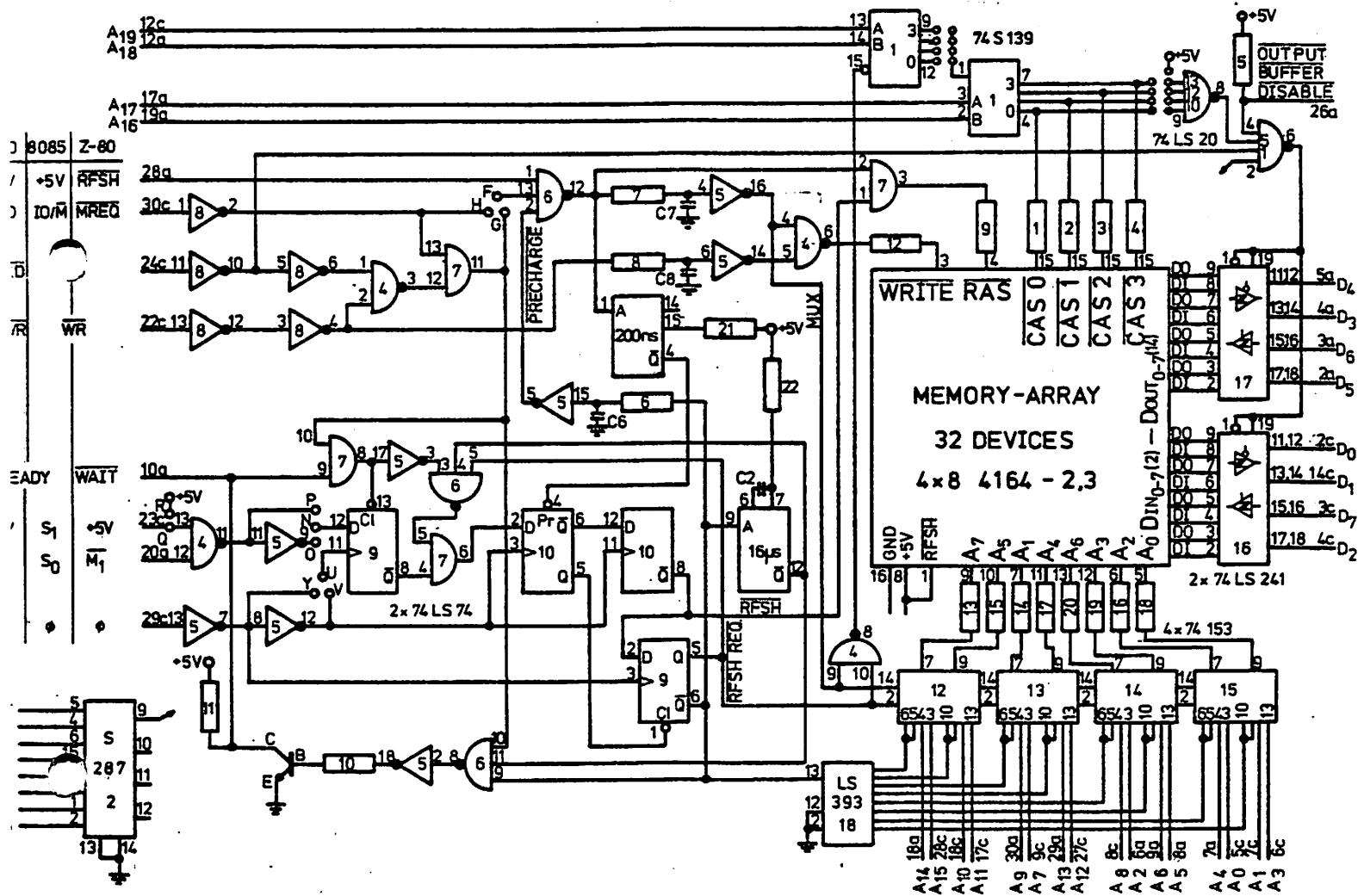

## quasi-statischer Betrieb

Beim dynamischen Speichermedium werden Daten in Form von Ladungen gespeichert, die bedingt durch Leckströme verloren gehen. Es ist daher notwendig die Informationszellen (Kapazitäten) alle 2 ms wiederaufzuladen. Um dies in allen System-Situationen garantieren zu können, wurde auf der Karte ein Refresh-Controller implementiert. Dabei findet eine Mischtechnik aus zwei verschiedenen Refresh-Arten Anwendung:

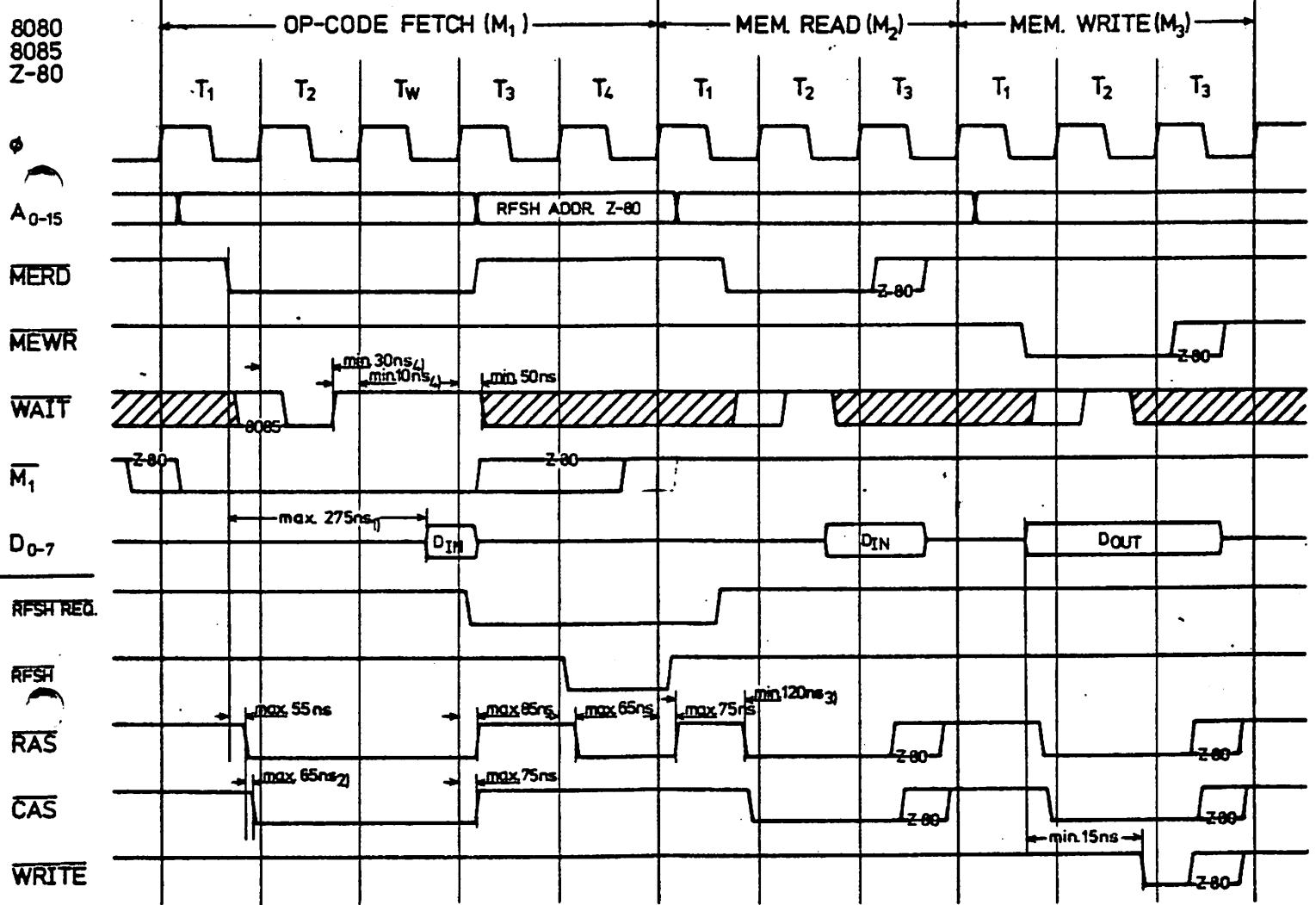

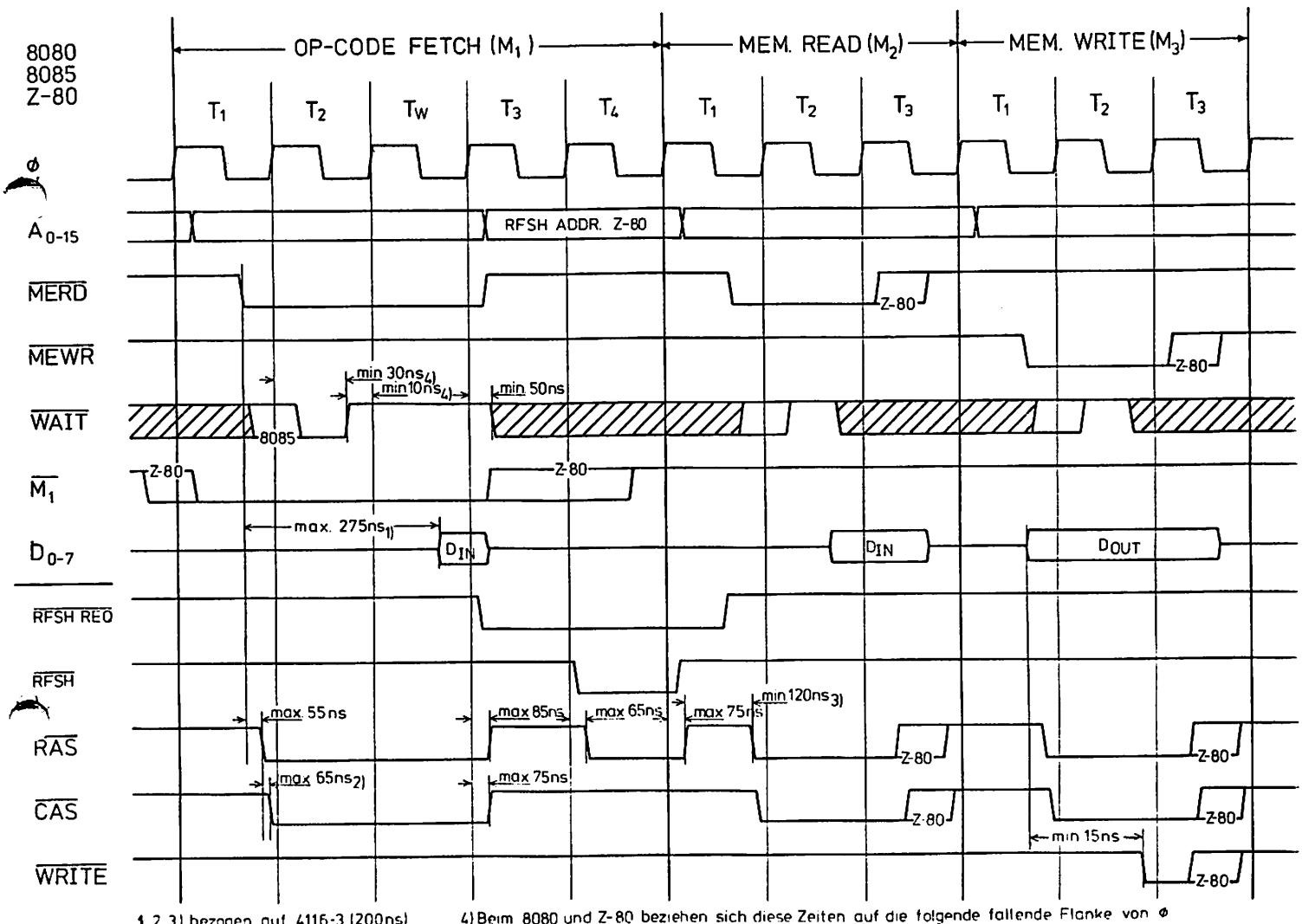

- 1) Hidden Refresh

- 2) Single Burst Refresh

Ersterer wird während T3 und T4 eines jeden M1 Zyklus generiert. Da der Prozessor in dieser Zeit intern mit der Befehlserkennung beschäftigt ist, also nicht auf den Speicher zugreift, erscheint für ihn der Refresh "transparent". Die Speicher-karte muß keine "Wait's" ausgeben um den Prozessor zu synchronisieren, was eine Herabsetzung der Systemfrequenz bedeuten würde.

Voraussetzung für diese Refresh-Art ist jedoch, daß der Prozessor binnen 2 ms mindestens 128 M1 Zyklen durchläuft, um einen Datenverlust zu vermeiden. Bei einem normalen Prozessorbetrieb ist dies gewährleistet. Kritisch wird es jedoch in folgenden Situationen, in denen keine M1 Zyklen generiert werden:

- 1) DMA - Zyklus (Floppy, ...)

- 2) System - Reset

- 3) Hardware - Wait (Not Ready)

- 4) Software - Wait (76H) beim 8080 und 8085

Um auch hier einen Datenverlust zu vermeiden wird der Single Burst Refresh angewandt: Eine Steuerung überwacht, daß binnen 16 us mindestens eine der 128 Speicherreihen (Row) aufgefrischt wird. Ist dies nicht der Fall wird unabhängig vom Prozessor-Status eine Reihe "refresh'd". Versucht die CPU während dieses Vorgangs einen Speicherzugriff auszuführen, wird sie durch einen Wait (Open-Collector Ausgang) der RAM-Karte synchronisiert.

## Systemfrequenz

Durch den auf der Karte befindlichen Refresh-Controller ist es möglich diese auch noch bei höheren Frequenzen zu betreiben. In Verbindung mit 200 ns Speichern ist ein problemloser Betrieb bis 5 MHz möglich ohne dabei den Systemdurchsatz durch Ausgabe von Wait Stait's herabsetzen zu müssen. 150 ns Speicher (Option) ermöglichen Frequenzen bis 6 MHz, was vor allem in Verbindung mit der B Version des Z-80 (6 MHz) und zukünftigen Prozessoren interessant ist.

## 1 M-Byte System

Um einen Ausbau über 256 KByte zu ermöglichen, werden auf der ECB/D 256 zusätzlich die beiden Adressen A 18 und A 19 dekodiert. Ein 1 M-Byte System läßt sich so einfach aus vier 256 KByte Karten zusammenstellen.

## Ausblendung

Mittels eines PROM's ist es möglich jeden einzelnen der insgesamt 256 1 KByte Blöcke auszublenden. Dieser PROM wird nach Kundenwunsch von uns programmiert. Zusätzlich ist eine extern gesteuerte Ausblendung über den OUTPUT BUFFER DISABLE Eingang möglich.

## Technische Daten

|                              |                                                                                                                                     |                                      |

|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| Abmessungen                  | : 100x160 mm (Europakarte)                                                                                                          |                                      |

| Busstecker                   | : 64 polig, a+c belegt                                                                                                              |                                      |

| Busnorm                      | : ECB - BUS                                                                                                                         |                                      |

| Fan in                       | : 1 TTL - Last                                                                                                                      |                                      |

| Stromaufnahme :              | +5V                                                                                                                                 | 700 mA (2,5 MHz)<br>900 mA (4,0 MHz) |

| Speichertyp:                 | 200ns                                                                                                                               | 150 ns                               |

| Zugriffszeit :               | max.                                                                                                                                | 270 ns                               |

|                              | typ.                                                                                                                                | 180 ns                               |

|                              |                                                                                                                                     | 155 ns                               |

| Systemfrequenz:              | max.                                                                                                                                | 5 MHz                                |

|                              |                                                                                                                                     | 6 MHz                                |

| Banking                      | : max. 1 M-Byte dekodierbar (A 16 - A 19)                                                                                           |                                      |

| Ausblendung (RAM Deselect) : | a, 1 KByte große Bereiche über TTL - PROM<br>b, externe Ausblendung über Output Buffer Disable                                      |                                      |

| Refresh Control :            | a, Hidden Refresh während T 3 und T 4 des M 1 Zyklus<br>b, "Single" Burst Refresh, wenn 16us lang kein M 1 Zyklus durchlaufen wurde |                                      |

# OETTLE & REICHLER

## Datentechnik

Adalbert-Stifter-Str. 40, 8902 Neusaess, Tel.: (0821) 48 18 80

### Teilbestueckung

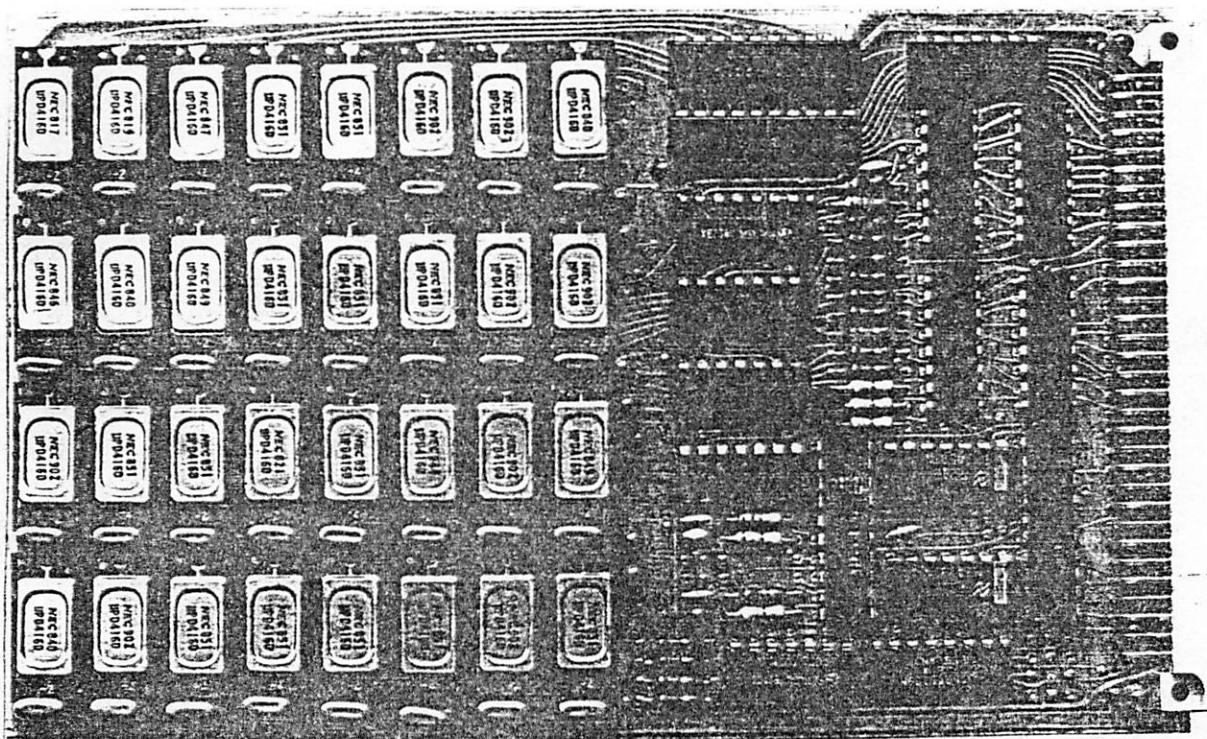

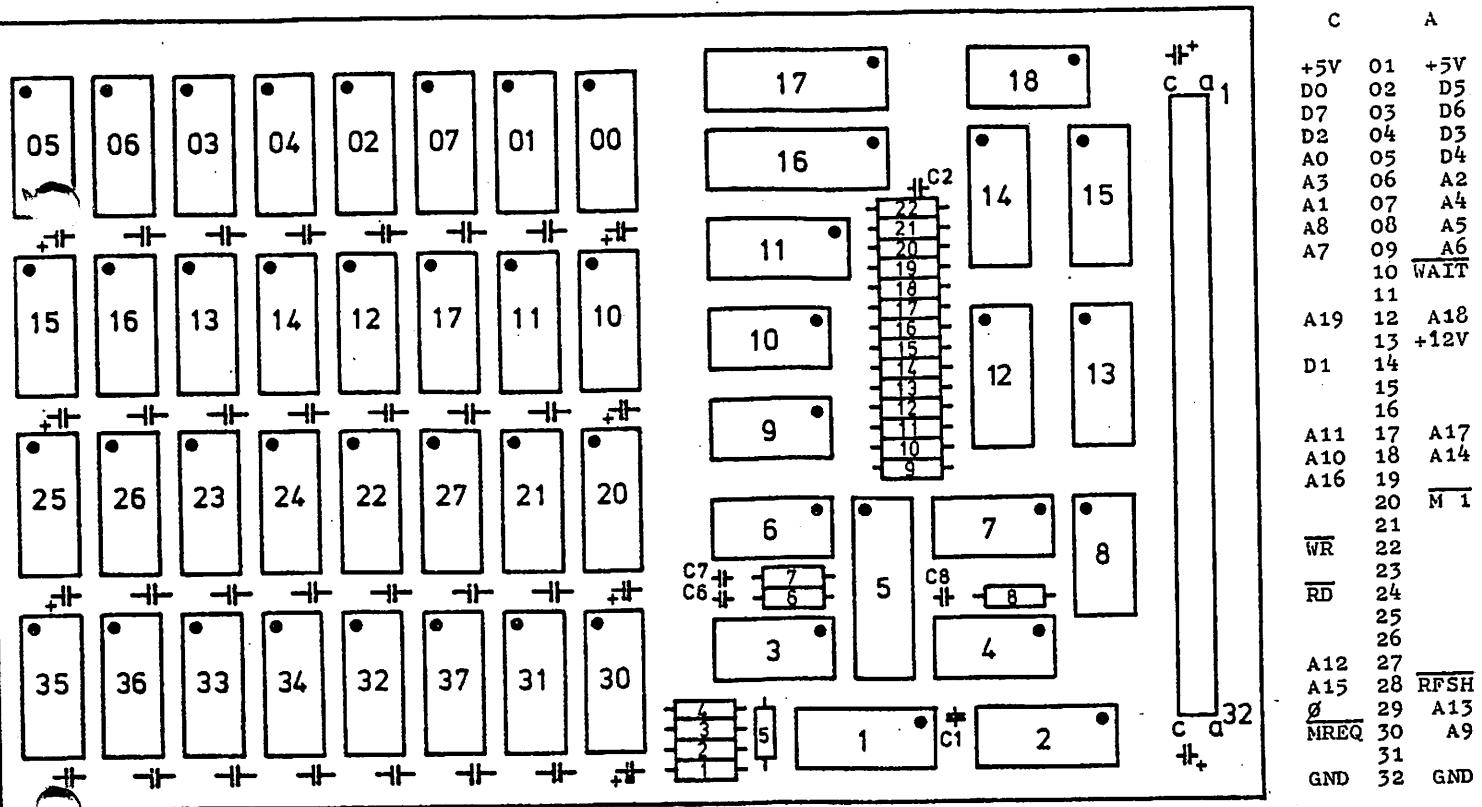

Die Platine kann in vier Schritten von 64 K-Byte bis 256 K-Byte ausgebaut werden. Welche Position ein 64 K Block im 256 K Feld einnimmt haengt davon ab an welcher Stelle die Speicherbausteine auf der Platine bestueckt werden. Die vier Reihen zu je acht Chip's sind hierfuer mit den Ziffern 0-3 gekennzeichnet.

Damit bei einem Lesebefehl der CPU in einem unbestueckten 64 K Block der Daten-Treiber nicht auf den Systembus treibt, ist fuer jeden der 64 K Blöcke eine Verbindung zu ziehen (Bild 1). Wird ein Block nicht bestueckt, muss der zugehoerige Eingang des 74 LS 20 (IC 8) mit +5V verbunden werden; andernfalls mit einem Ausgang des 74 LS 139 (IC 1).

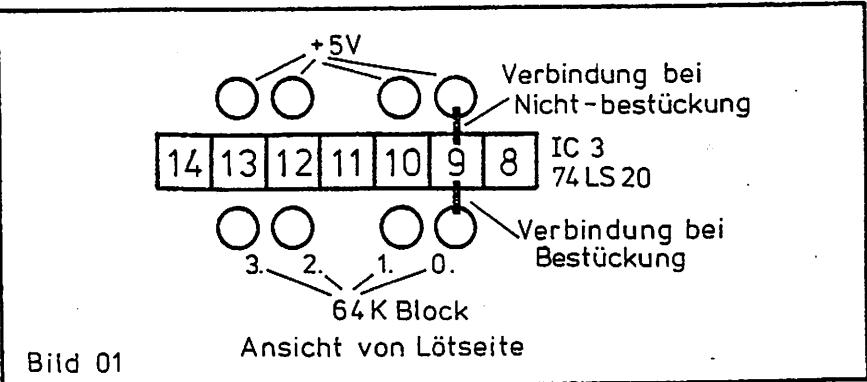

### 1 M-Byte System

Ueber einen Jumper kann die 256 K-Byte Karte auf eine von vier moeglichen Positionen im 1 M Feld gelegt werden. Die Ausgaenge des 4 aus 2 Dekoders (IC 1) sind hierfuer mit den Ziffern 0-3 gekennzeichnet (Bild 2). Es ist zu beachten, dass die Eingaenge A 16 - A 19 beschaltet werden, auch wenn nur 64 K-Byte bestueckt werden.

### Ausblendung

Mittel eines PROM's ist es moeglich jeden der insgesamt 256 1 K Blöcke zu deseletkieren. Dieser PROM wird beim Bausatz nicht mitgeliefert, sondern kann, nach Kundenwunsch von uns programmiert, gesondert bezogen werden. Wird keine Ausblendung benoetigt, empfiehlt es sich IC 2 durch eine Brücke von Pin 9 nach Pin 16 zu ersetzen. Ebenfalls ist eine extern gesteuerte Ausblendung ueber den Output Buffer Disable Eingang moeglich.

### Refresh

Beim dynamischen Speichermedium werden Daten in Form von Ladungen gespeichert, die bedingt durch Leckstroeme verloren gehen. Es ist daher notwendig die Informationszellen (Kapazitaeten) alle 2 ms wieder aufzuladen. Um dies in allen System-Situationen garantieren zu koennen, wurde auf der Karte ein Refresh-Controller implementiert. Dabei findet eine Mischtechnik aus zwei verschiedenen Refresh-Arten Anwendung:

### 1) Hidden Refresh

### 2) Single Burst Refresh

Ersterer wird waehrend T3 und T4 eines jeden M1 Zyklus generiert. Da der Prozessor in dieser Zeit intern mit der Befehlserkennung beschaeftigt ist, also nicht auf den Speicher zugreift, erscheint fuer ihn der Refresh "transparent". Die Speicher-karte muss keine "Waits's" ausgeben um den Prozessor zu synchronisieren, was eine Herabsetzung der Systemfrequenz bedeuten wuerde. Voraussetzung fuer diese Refresh-Art ist jedoch, dass der Prozessor binnen 2 ms mindestens 128 M1 Zyklus durchlaeuft, um einen Datenverlust zu vermeiden. Bei einem normalen Prozessorbe-trieb ist dies gewaehrleistet. Kritisch wird es jedoch in folgenden Situationen, in denen keine M1 Zyklus generiert werden:

### 1) DMA - Zyklus (Floppy,...)

### 2) System - Reset

### 3) Hardware - Wait (Not Ready)

### 4) Software - Wait (76 H) beim 8080 und 8085

Um auch hier einen Datenverlust zu vermeiden wird der Single Burst Refresh angewandt: Eine Steuerung ueberwacht, dass binnen 16 us mindestens eine der 128 Speicherreihen (Row) aufgefrischt wird. Ist dies nicht der Fall wird unabhaengig vom Prozessor Status eine Reihe "refresh'd". Versucht die CPU waehrend dieses Vorgangs einen Speicherzugriff auszufuehren, wird sie durch einen Wait (Open Collector Ausgang) der RAM-Karte synchronisiert. Wird der Single Burst Refresh nicht benoetigt, da keine Wait- oder DMA-Zyklen ueber 2 ms auftreten, koennen folgende Bauteile entfallen:

IC 11, R 10, 21, 22 C 02, T 01

Dafuer sind zwei Bruecken einzusetzen:

IC 11 Pin 04 nach Pin 16

IC 11 Pin 08 nach Pin 12

### Systemfrequenz

Durch den auf der Karte befindlichen Refresh-Controller ist es moeglich diese auch noch bei hoeheren Frequenzen zu betreiben. In Verbindung mit 200 ns Speichern ist ein problemloser Betrieb bis 5 MHz moeglich ohne dabei den Systemdurchsatz durch Ausgabe von Wait State's herabsetzen zu muessen. 150 ns Speicher ermoeglichen Frequenzen bis 6 MHz, was vor allem in Verbindung mit der B Version des Z-80 (6MHz) und zukuenftigen Prozes-soren interessant ist.

1,2,3) bezogen auf 4116-3 (200ns)

4) Beim 8080 und Z-80 beziehen sich diese Zeiten auf die folgende fallende Flanke von φ

8080      8085      Z-80

#### Bus - Signale:

|      |       |                       |      |

|------|-------|-----------------------|------|

| 10 a | READY | READY                 | WAIT |

| 20 a | M 1   | S 0                   | M 1  |

| 26 a | -     | OUTPUT BUFFER DISABLE |      |

| 28 a | + 5V  | + 5V                  | RFSH |

| 22 c | MEWR  | WR                    | WR   |

| 25 c | + 5V  | S 1                   | + 5V |

| 24 c | MERD  | RD                    | RD   |

| 29 c | Ø 2   | Ø                     | Ø    |

| 30 c | GND   | IO/M                  | MERQ |

#### Bauelemente:

| R       | Erl          | Elko      | 4x2+2 x 4,7 uF |

|---------|--------------|-----------|----------------|

| R 01-04 | 33 Ohm       | IC 00-57  | 4x8 4164/2,3   |

| R 05    | 4,7 K Ohm    | IC 01     | 74 LS 139      |

| R 06    | 100 Ohm      | IC 02     | 74 S 287       |

| R 07    | 240 Ohm      | IC 03     | 74 LS 20       |

| R 09    | 33 Ohm       | IC 04     | 74 132         |

| R 10    | 470 Ohm      | IC 05     | 74 LS 240      |

| R 11    | 4,7 K Ohm    | IC 06     | 74 LS 10       |

| R 12-20 | 33 Ohm       | IC 07     | 74 S 08        |

| R 21    | 27 K Ohm     | IC 08     | 74 LS 14       |

| R 22    | 20 K Ohm     | IC 09, 10 | 74 LS 74       |

| C 01    | (120 pF)     | IC 11-14  | 74 153         |

| C 02    | 2,2 nF       | IC 16, 17 | 74 LS 241      |

| C 06    | 120 pF       | IC 18     | 74 LS 393      |

| C 07    | 120 pF       |           |                |

| C 00-37 | 4x6 x 0,1 uF | T 01      | BC 237         |

#### Verbindungen:

|     |    |    |    |

|-----|----|----|----|

| FHG | FG | FG | FH |

| NOP | NP | NO | NP |

| QR  | QR |    | QR |

| UVY | UY | UV | UY |

#### Bauteile:

|     |        |        |        |

|-----|--------|--------|--------|

| R 8 | 390    | 270    | Brücke |

| C 8 | 330 pF | 330 pF |        |

Brücke 1 : IC 17 PIN 10 -

- Speicher 00 PIN 16 -

- IC 16 PIN 10

Brücke 2 : IC 2 PIN 8 - GND

Bild 01

Bild 02

# Dynamische Speicher

## 64 KByte auf einer Europaplatine

### Teilbestückung ist möglich

Die Platine kann in beliebigen Schritten von 16 KByte bis 64 KByte bestückt werden. Welche Position die 16-KByte-Blöcke im System einnehmen sollen, hängt davon ab, an welcher Stelle die Speicherbausteine eingesetzt werden. Die insgesamt vier Reihen zu je acht 4116 sind mit den Ziffern 0-3 gekennzeichnet. Für den „Data Buffer Control“ ist es wichtig, ob ein 16-KByte-block bestückt wurde oder nicht. Dadurch ist für jeden 16-KByte-Block am IC 1 (7420), Pin 1, 2, 4, 5 eine Verbindung nötig. Wird eine Reihe bestückt, muß der zugehörige Pin mit dem danebenliegenden Lötpunkt verbunden werden, andernfalls mit der gegenüberliegenden +5-V-Leitung (Bild 2).

### Die Ausblendung von Bereichen in der Karte

Über IC 2 (74 S 139), einem vier aus zwei Decoder, kann entweder ein Banking mehrerer 64-KByte-Karten oder eine Ausblendung eines bestimmten Speicherbereiches aus dem 64-KByte-Feld realisiert werden.

Da der Prozessor unbedingt einen Festwertspeicher benötigt, in dem die Anroutinen des Systems abgelegt sind – bei einer vollständig bestückten Karte dafür jedoch kein Freiraum mehr wäre – muß in den 64-KByte-Block sozusagen ein „Loch“ hineingeschnitten werden, in das das ROM gesetzt werden kann. Dieses „Herausschneiden“ vollzieht sich folgendermaßen: Liegt eine für den Festwertspeicher gültige Adresse am Systembus vor, wird der Daten-Puffer der Karte in den Tri-State-Zustand versetzt. Bei einem Lesebefehl der CPU in diesem Adressbereich wird also nur noch der Festwertspeicher angesprochen, womit ein Datentransport zwischen ROM und CPU ungestört ablaufen kann. Größe und Stellung im 64-KByte-Feld können dabei beliebig gewählt werden. Eine extern gesteuerte Ausblendung über den Output Buffer Disable-Eingang ist ebenfalls möglich. Sämtliche dazu notwendigen Verdrahtungen sind unter dem IC 2 und dem daneben angeordneten Verdrahtungsfeld durchzuführen, Bild 1.

Grundsätzlich ist Lötpunkt A mit GND zu verbinden. Je nachdem, in welchem Block die Ausblendung liegen soll, muß Pin 15 (IC 2) mit 0, 1, 2 oder 3 (Pin 4-7) verbunden werden. 0 repräsentiert dabei den untersten, 3 den obersten 16-KByte-Block. Je nach Größe der Ausblendung (4 K oder 8 K) werden Pin 13 und 14 mit A12 und A13 (4 K) oder A13 und A14 (8 K) verbunden. Durch eine Brücke von den Pins 9...12 nach Lötpunkt B wird die Stellung der Ausblendung in dem 16-KByte-Block bestimmt.

### Bank-Select zur Speichererweiterung

Diese Schaltung ermöglicht es, mehrere 64-KByte-Karten aneinanderzureihen. Welche Position die einzelne Karte einnehmen soll, kann mit wenigen Brücken festgelegt werden. Grundsätzlich müssen folgende Verbindungen gezogen werden: B an +5 V, A16 an Pin 13 (IC 2), A17 an Pin 14 und Pin 15 mit A18 oder A19. Die Position der Karte in der Bankumschaltung wird durch die Verbindung von A mit einem der Pins 9 bis 12 bestimmt.

Wird kein Bank - Select, als auch keine Ausblendung benötigt, muß Lötpunkt A mit GND und B mit +5V verbunden werden.

### 8080, 8085 und Z-80 Refresh

Bei dieser Prozessor Familie werden je nach System-Status zwei verschiedene Refresh-Techniken angewandt:

1, Hidden Refresh

2, Single Burst Refresh

Ersterer wird während T3 und T4 eines jeden M1 Zyklus generiert. Da der Prozessor in dieser Zeit intern mit der Befehlserkennung beschäftigt ist, also nicht auf den Speicher zugreift, erscheint für ihn der Refresh "transparent". Die Speicherkarte muß also keine "Wait's" ausgeben um den Prozessor zu synchronisieren, was eine Herabsetzung des Systemdurchsatzes bedeuten würde.

Voraussetzung ist jedoch, daß der Prozessor binnen 2 ms mindestens 128 M1 Zyklen durchläuft, da sonst ein Datenverlust eintreten könnte. Bei einem normalen Prozessorbetrieb ist dies gewährleistet. Kritisch wird es jedoch bei Wait- oder DMA-Zyklen, die einen Zeitraum von 2 ms überschreiten. Um auch hier einen Datenverlust zu vermeiden, wird der Single Burst Refresh angewandt: Ein Monoflop überwacht, daß alle 16 us mindestens eine der 128 Reihen aufgefrischt wird. Ist dies nicht der Fall, wird unabhängig vom Prozessor eine Reihe refresh'd. Versucht der Prozessor während dieses Vorgangs einen Speicherzugriff auszuführen, wird er durch ein Wait (Open Collector Ausgang) der RAM - Karte synchronisiert.

Wird der Single Burst Refresh nicht benötigt, da keine Wait- oder DMA-Zyklen über 2 ms auftreten, können folgende Bauteile entfallen:

IC 10 , R 12,23,24 , C 01 ,

T 01

Dafür sind zwei Brücken zu setzen:

IC 10 Pin 04 nach Pin 16

IC 10 Pin 08 nach Pin 12

### Systemfrequenz

Durch den auf der Karte befindlichen Refresh-Controller ist es möglich diese auch noch bei größeren Systemfrequenzen zu betreiben. Dies wirkt sich insbesondere in Verbindung mit den 8080, 8085 und Z-80 Prozessoren aus. Bei einer Bestückung mit 200 ns Speichern ist ein Betrieb bis 5 MHz gewährleistet, ohne dabei die CPU anhalten zu müssen. 150 ns Speicher ermöglichen Frequenzen bis 6 MHz, was vor allem in Verbindung mit der B Version des Z-80 (6 MHz) interessant werden dürfte.

Bei 65XX und 68XX Prozessoren ist die Grundversion (200 ns) bei 1 MHz, die schnellere (150 ns) bei 1,5 MHz lauffähig.

1, 2, 3) bezogen auf 4116-3 (200ns)      4) Beim 8080 und Z-80 beziehen sich diese Zeiten auf die folgende fallende Flanke von  $\phi$

### **Standard-Adressebelegung:**

**Standardmäßig belegt das FDC-Modul folgende 8 I/O-Adressen:**

|                  |                          |

|------------------|--------------------------|

| <b>20h - 23h</b> | <b>Z-80 PIO</b>          |

|                  | 20h Port A Data          |

|                  | 21h Port B Data          |

|                  | 22h Port A Control       |

|                  | 23h Port B Control       |

| <b>24h - 25h</b> | <b>uPD 765 FDC</b>       |

|                  | 24h FDC Command Port     |

|                  | 25h FDC Data Port        |

| <b>26h</b>       | <b>Z-80 DMA</b>          |

| <b>27h</b>       | <b>Motor on I und II</b> |

**Standardmäßig belegt das RGB-Modul folgende 16 I/O-Adressen:**

|            |                                                     |

|------------|-----------------------------------------------------|

| <b>30H</b> | <b>GDP Status Read, Parameter into FIFO</b>         |

| <b>31H</b> | <b>GDP FIFO Read, Command into FIFO</b>             |

| <b>32H</b> | <b>GDP , entspricht 30H</b>                         |

| <b>33H</b> | <b>GDP , entspricht 31H</b>                         |

| <b>34H</b> | <b>PIO Port A: Output, adresiert EPROM A3 - A10</b> |

| <b>35H</b> | <b>PIO Port B: Input, Bit 0 liest DRQ von GDP</b>   |

| <b>36H</b> | <b>PIO Port C: Output, select Zoom-Colour, DACK</b> |

| <b>37H</b> | <b>PIO Control: Bestimmt Betriebsart der PIO</b>    |

**38H-3FH EPROM 2716: Lesen einer Charakter-Row**

**Standardmäßig belegt das CPU-Modul folgende 27 I/O-Addressen:**

|                  |                                                   |

|------------------|---------------------------------------------------|

| <b>50h - 5Fh</b> | <b>STI Serial Timer Interrupt Controller</b>      |

|                  | 50h Indirect Data Register                        |

|                  | ...                                               |

|                  | 5Fh Usart Data Register                           |

| <b>60h - 63h</b> | <b>DART Dual Asynchronous Receive/Transmitter</b> |

|                  | 60h Channel A Data                                |

|                  | 61h Channel A Ctr                                 |

|                  | 62h Channel B Data                                |

|                  | 63h Channel B Ctr                                 |

| <b>64h - 67h</b> | <b>PIO 8255 Peripheral I/O Controller</b>         |

|                  | 64h Port A                                        |

|                  | 65h Port B                                        |

|                  | 66h Port C                                        |

|                  | 67h Control Port                                  |

| <b>68h - 69h</b> | <b>APU 9511/12 Arithmetik Processor</b>           |

|                  | 68h Data-Port                                     |

|                  | 69h Command/Control Port                          |

| <b>6Ah</b>       | <b>MMU Memory Management Unit</b>                 |