**oettle & reichler

datentechnik GmbH**

**Völkstraße 27

8900 Augsburg 1**

**Tel.: (0821) 15 46 32**

---

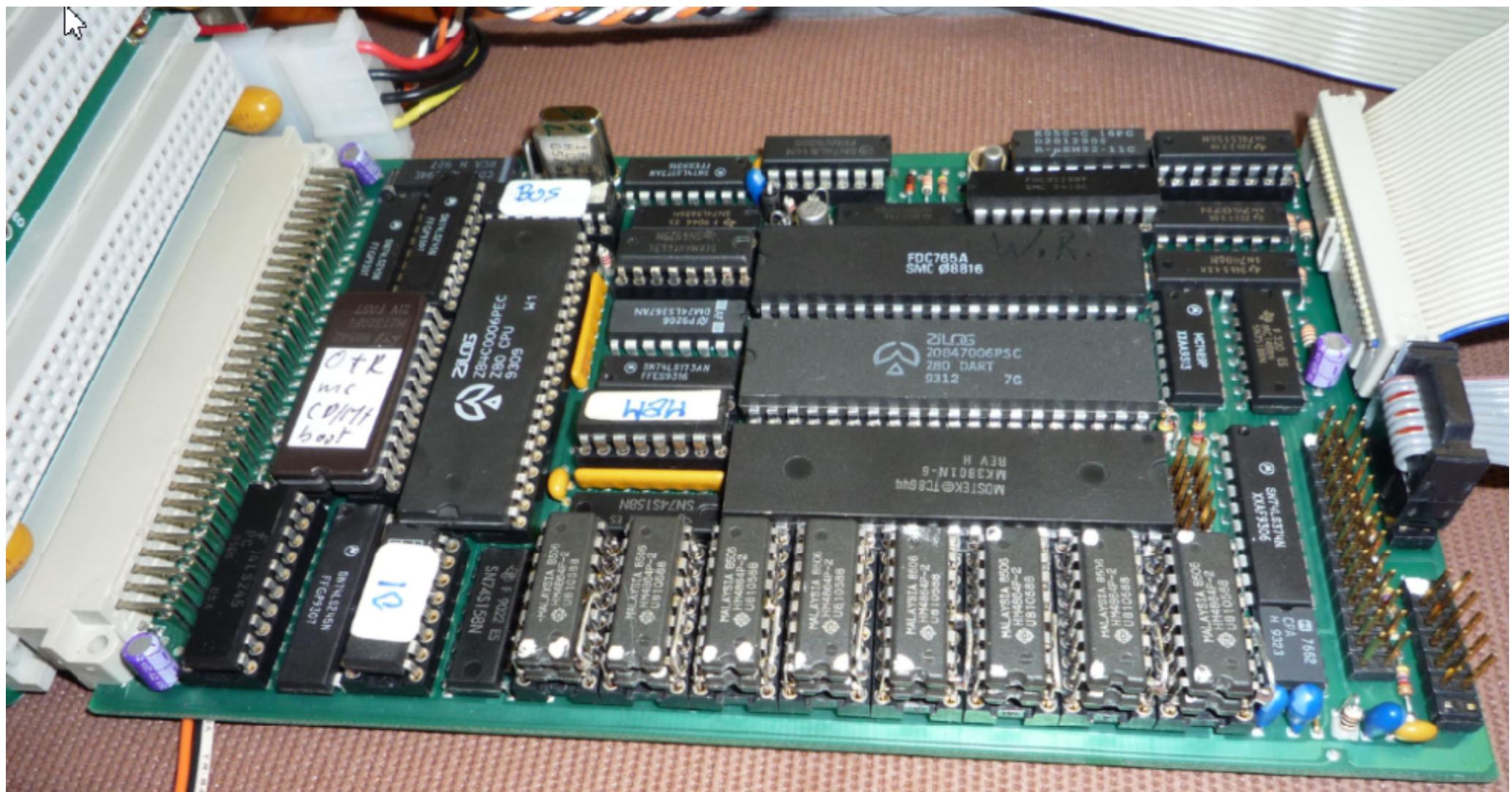

**E P C**

**Einplatinencomputer**

**H A N D B U C H**

**Copyright (C) by DATENTECHNIK OETTLE + REICHLER, Augsburg

Dezember 1983**

## EPC ist ein EinPlatinenComputer

## **Inhaltsverzeichnis**

|                                                    |    |

|----------------------------------------------------|----|

| <b>Schaltungsbeschreibung</b> .....                | 4  |

| <b>Einsatzmöglichkeiten</b> .....                  | 4  |

| <b>Schaltungsübersicht</b> .....                   | 5  |

| <br><b>Hardwarebeschreibung</b> .....              | 7  |

| <b>Stromversorgung</b> .....                       | 7  |

| <b>Takt</b> .....                                  | 7  |

| <b>Reset</b> .....                                 | 7  |

| <b>Wait</b> .....                                  | 7  |

| <b>Banking Speicherverwaltung</b> .....            | 8  |

| <b>Memory Select</b> .....                         | 8  |

| <b>Der dynamische Speicher</b> .....               | 9  |

| <b>Ansteuerung</b> .....                           | 9  |

| <b>Precharge Schaltung</b> .....                   | 9  |

| <b>Festwertspeicher</b> .....                      | 10 |

| <b>Floppy Steuerung</b> .....                      | 10 |

| <b>I/O Select</b> .....                            | 11 |

| <b>Schnittstellen</b> .....                        | 12 |

| <b>Centronics</b> .....                            | 12 |

| <b>RS-232</b> .....                                | 13 |

| <b>seriell TTL</b> .....                           | 14 |

| <b>Echtzeituhr</b> .....                           | 14 |

| <b>STI Serial Timer Interrupt Controller</b> ..... | 15 |

| <b>Bussteuerung</b> .....                          | 16 |

| <br><b>Einsatzmöglichkeiten</b> .....              | 17 |

| <b>Einsatz als I/O und RAM/ROM Baugruppe</b> ..... | 17 |

| <b>Einsatz als Slave Prozessor</b> .....           | 17 |

| <b>Einstellung</b> .....                           | 17 |

| <b>Funktionsweise</b> .....                        | 18 |

| <br><b>Inbetriebnahme</b> .....                    | 19 |

| <b>Terminalanschluß</b> .....                      | 19 |

| <b>Tastaturanschluß</b> .....                      | 19 |

| <b>Laufwerksanschluß</b> .....                     | 19 |

|                                                   |           |

|---------------------------------------------------|-----------|

| <b>Datenblätter .....</b>                         | <b>20</b> |

| Z-80 DART Asynchronous Receiver/Transmitter ..... | 20        |

| Pin Description .....                             | 20        |

| Functional Description .....                      | 21        |

| Internal Architecture .....                       | 23        |

| Programming .....                                 | 24        |

| Read and Write Registers .....                    | 25        |

| Z-80 STI Serial Timer Interrupt Controller .....  | 26        |

| Pin Description .....                             | 26        |

| Internal Registers .....                          | 26        |

| Register Accesses .....                           | 28        |

| Interrupts .....                                  | 29        |

| Timers .....                                      | 31        |

| Usart .....                                       | 32        |

| 765 Floppy Disk Controller .....                  | 34        |

| Instruction Set .....                             | 34        |

| Prozessor Interface .....                         | 35        |

| Functional Description .....                      | 36        |

| Status Register .....                             | 38        |

| Echtzeituhr MEM E050-16 .....                     | 40        |

| Description, Features .....                       | 40        |

| Operation .....                                   | 41        |

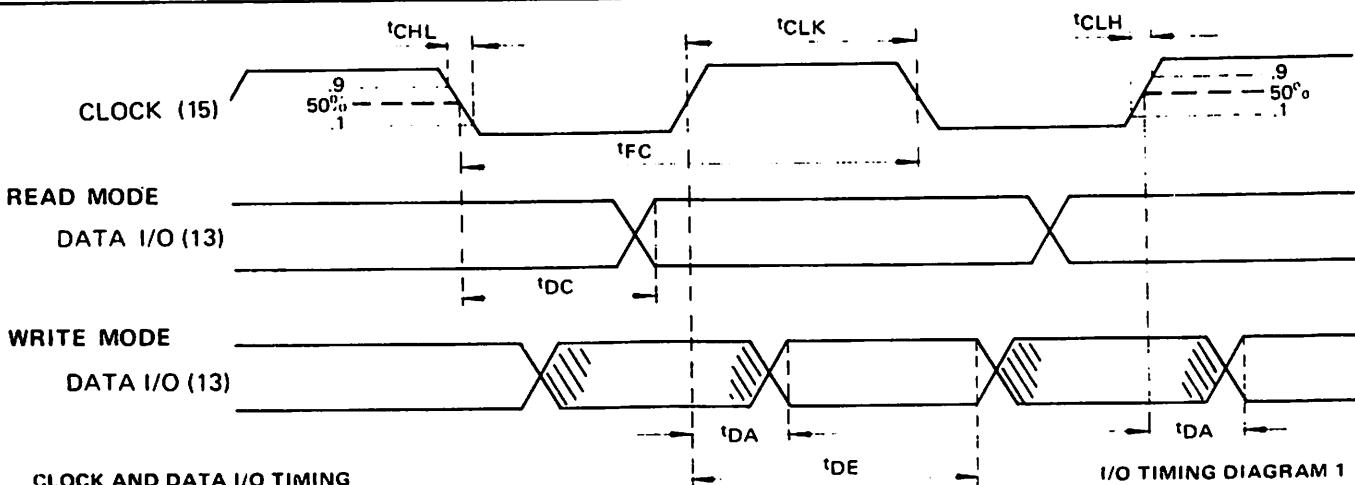

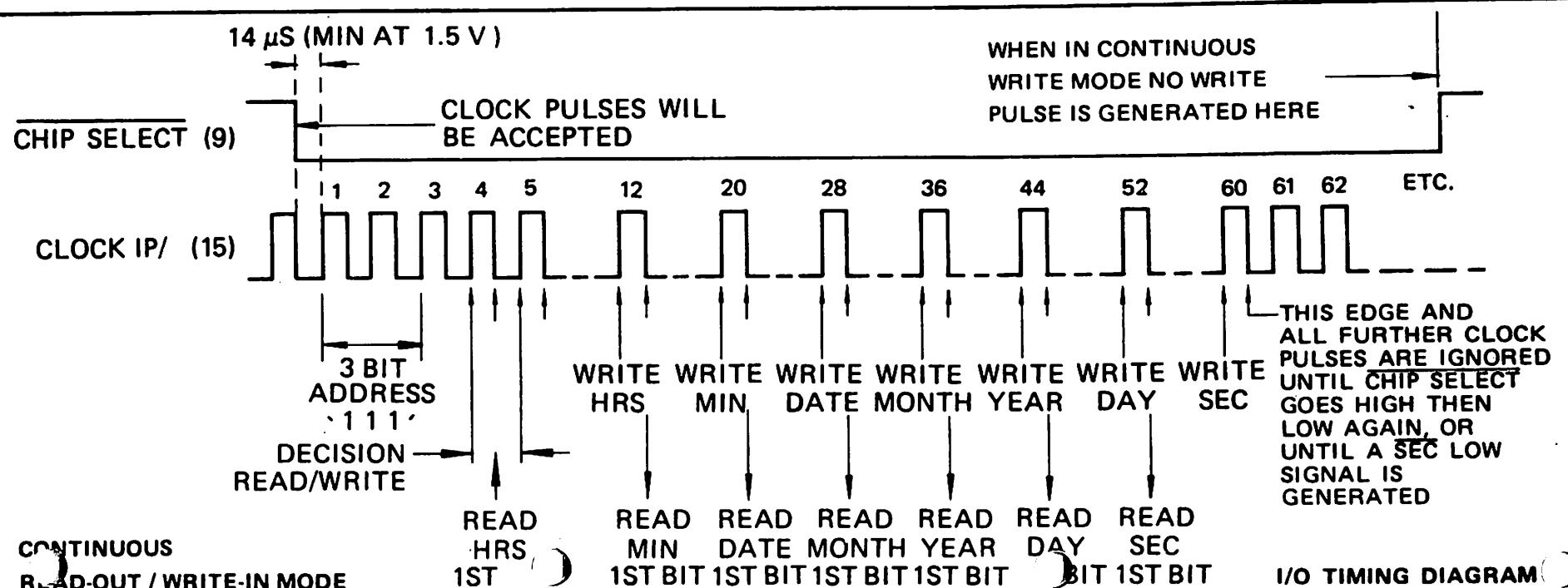

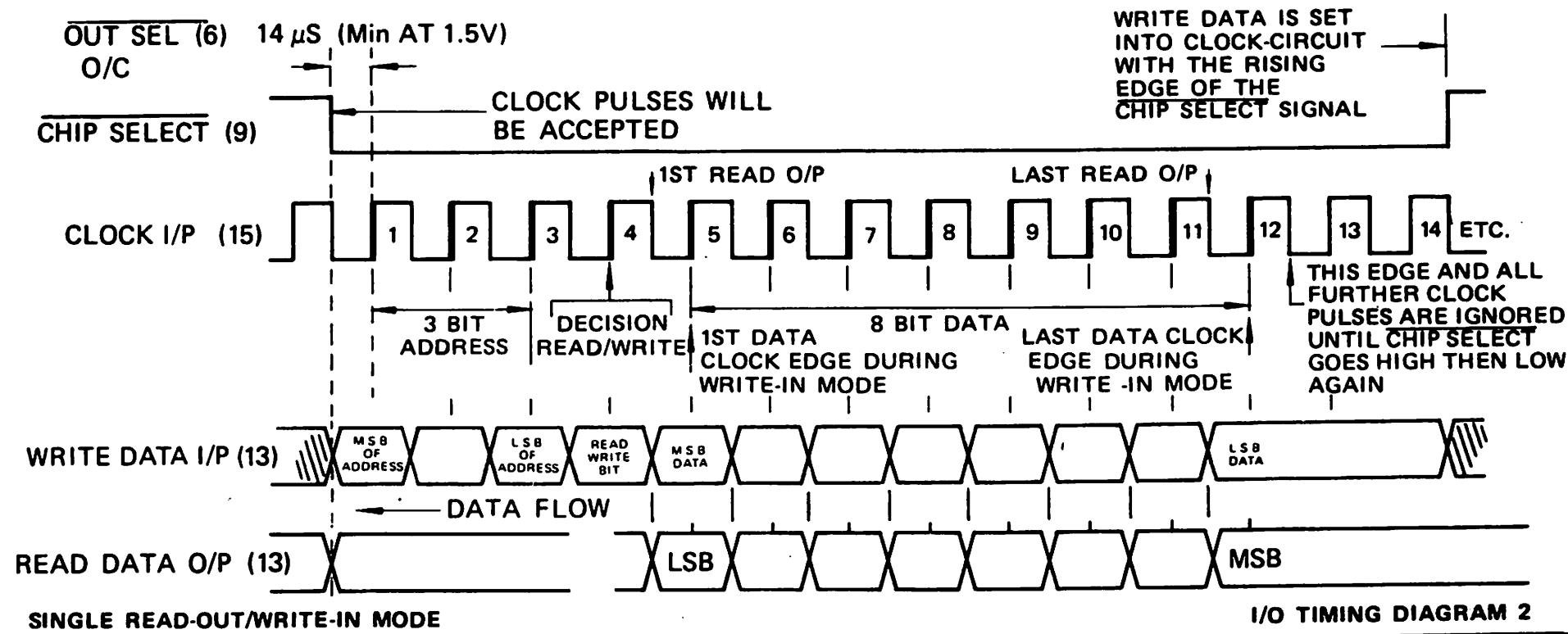

| Timing Diagramm .....                             | 43        |

| <b>Programm Beispiele .....</b>                   | <b>44</b> |

| <b>Anhang .....</b>                               | <b>56</b> |

| Stückliste .....                                  | 56        |

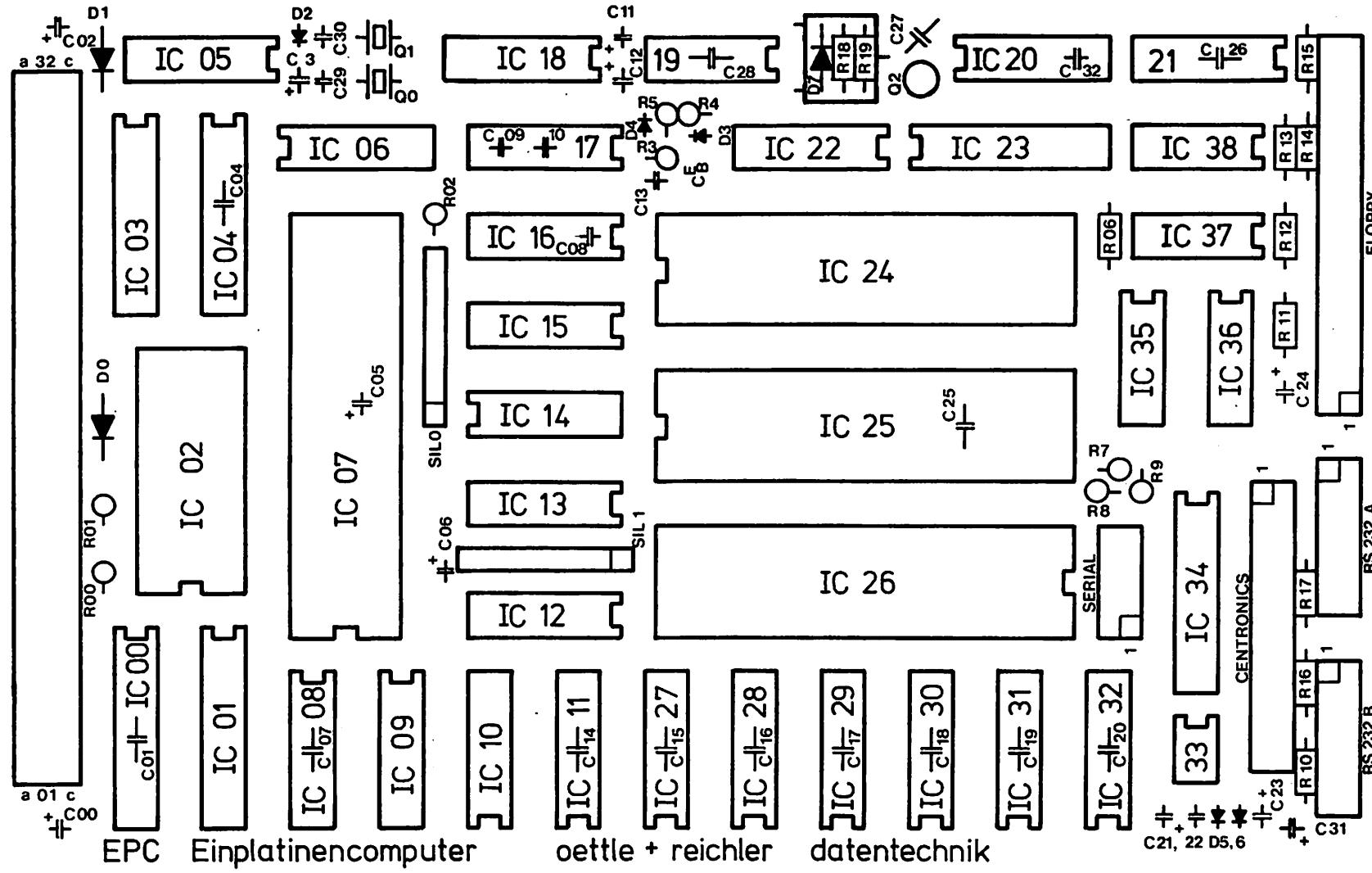

| Bestückungsplan .....                             | 57        |

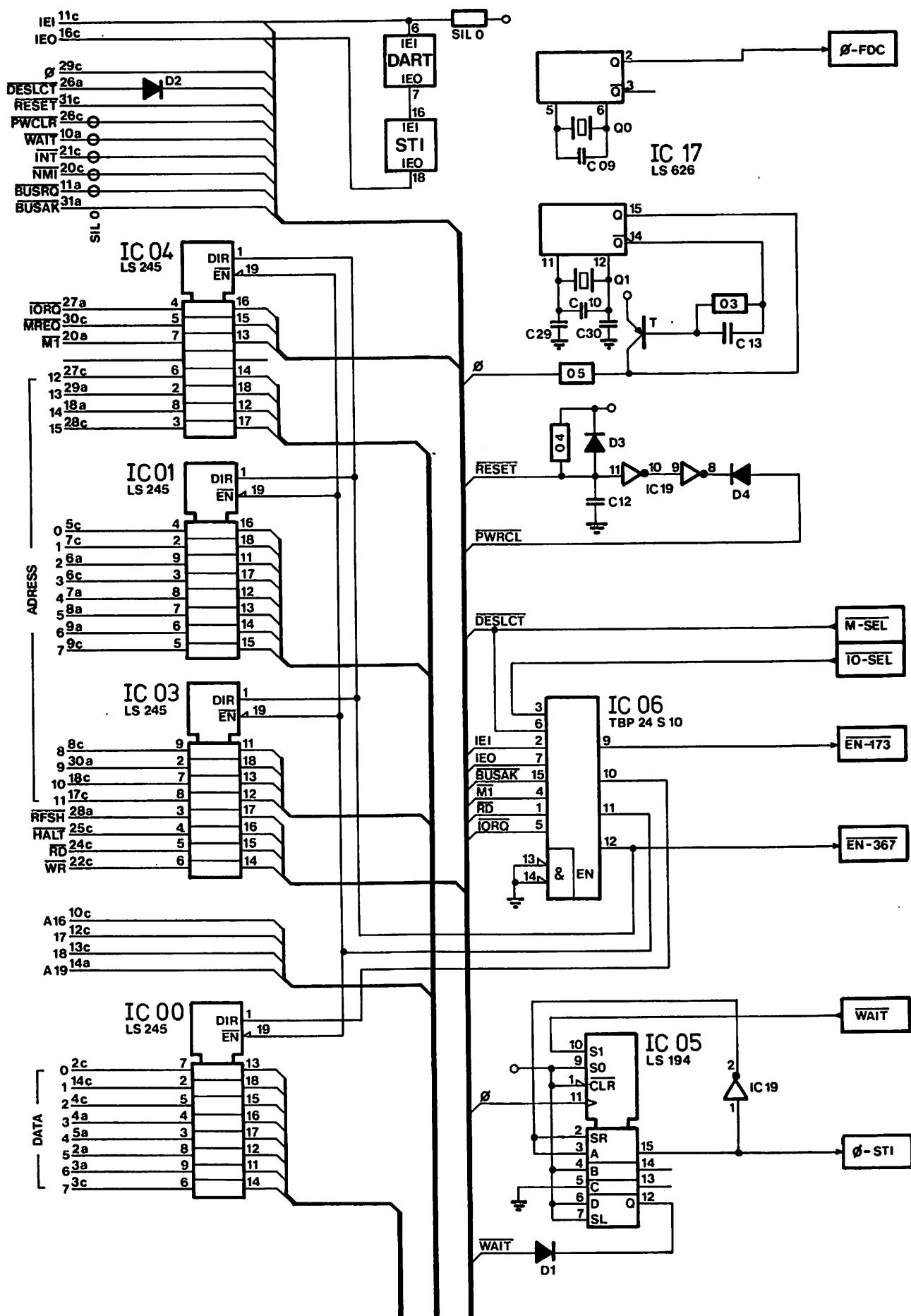

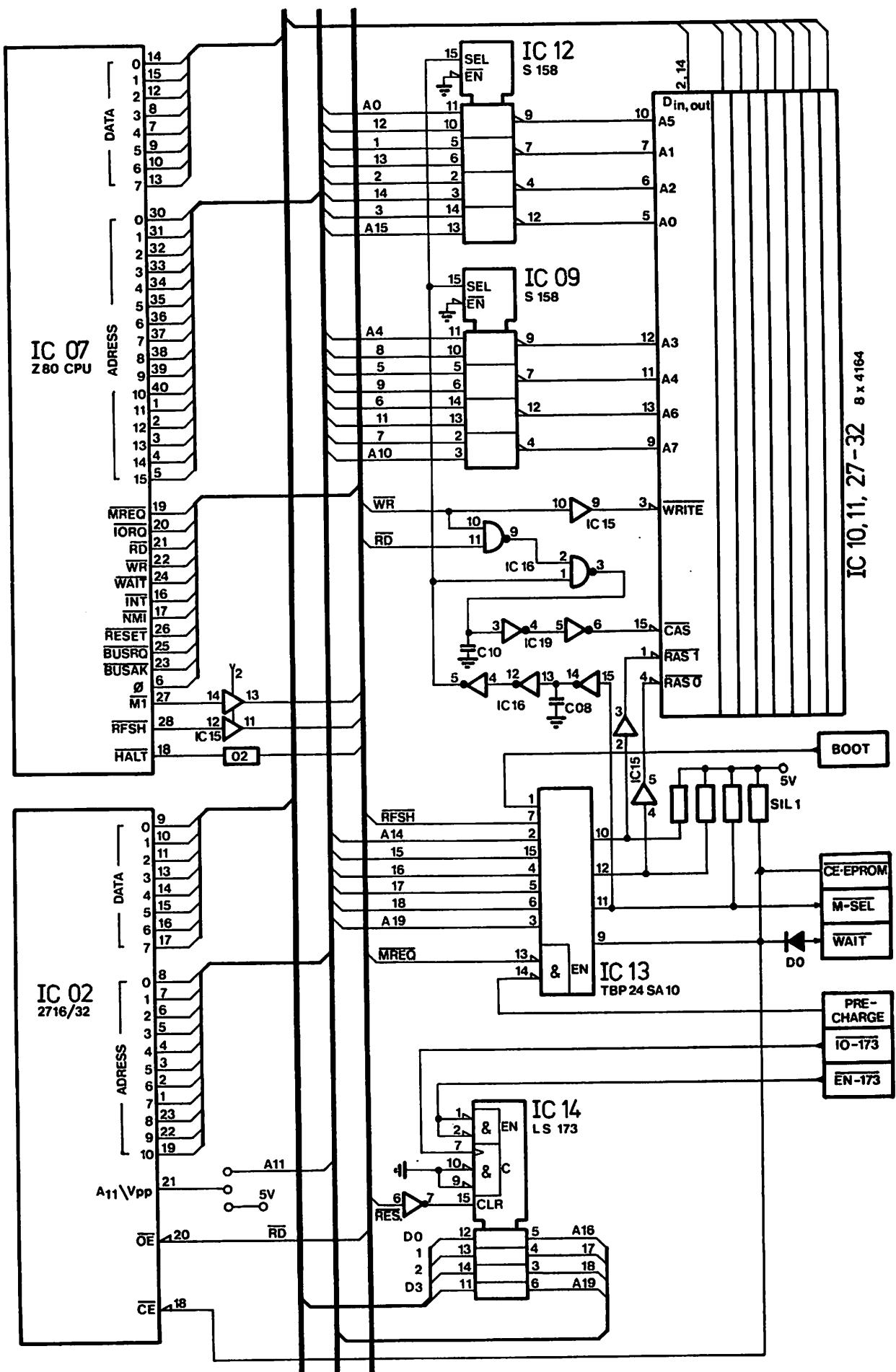

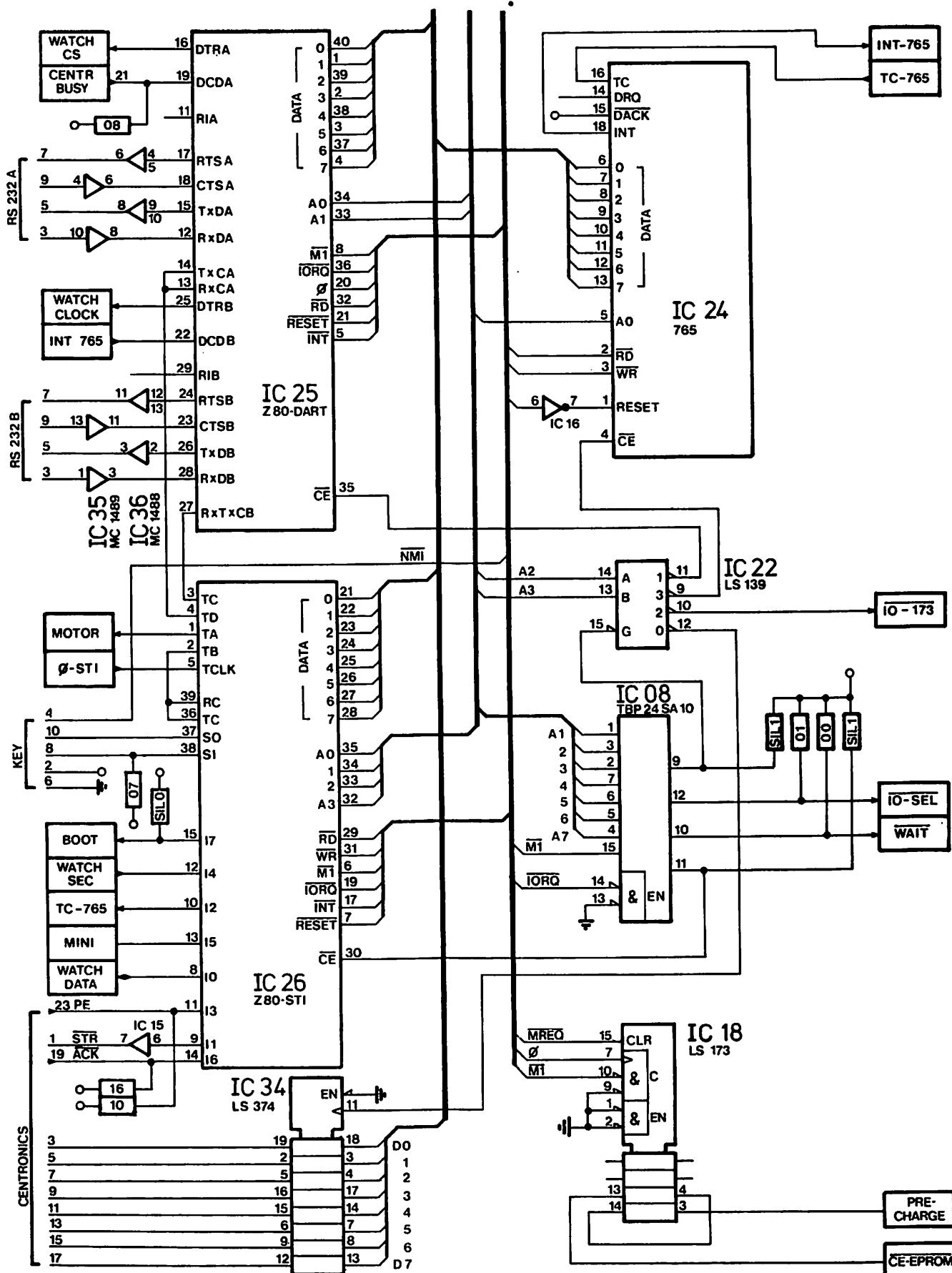

| Stromlaufplan .....                               | 58        |

---

Kein Teil dieser Veröffentlichung darf reproduziert, vervielfältigt, gespeichert oder übersetzt werden, ohne die ausdrückliche schriftliche Zustimmung von DATENTECHNIK oettle & reichler. Wir behalten uns das Recht vor, Änderungen, die einer Verbesserung einer Schaltung oder unserer Produkte dienen ohne besondere Hinweise vorzunehmen. Für die Richtigkeit der hier gegebenen Daten, Schaltpläne, Programme und Beschreibungen wird keine Haftung übernommen.

### **Einsatzmöglichkeiten**

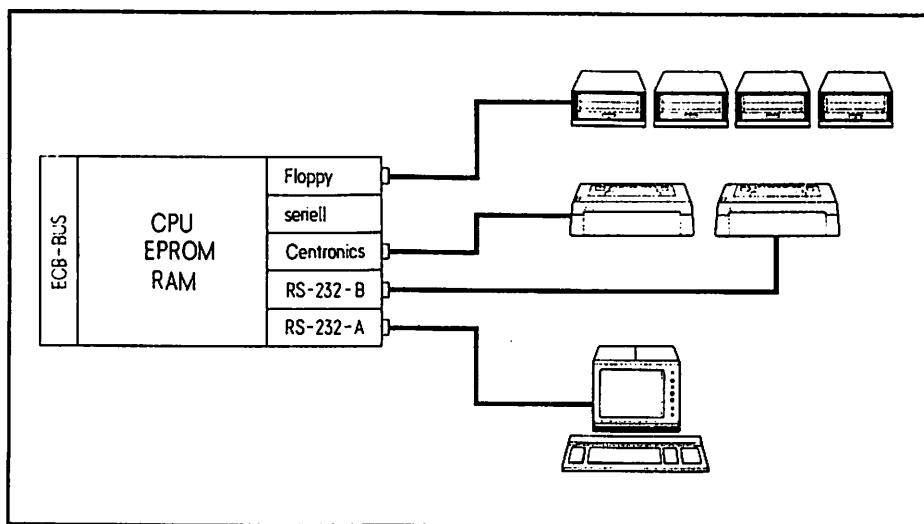

#### **stand-alone System**

Der EPC stellt sämtliche Funktionen für ein komplettes CP/M Plus Computersystem zur Verfügung. An Peripherie wird nur ein handelsübliches Terminal und mindestens ein Floppy Laufwerk benötigt.

#### **Master Baugruppe**

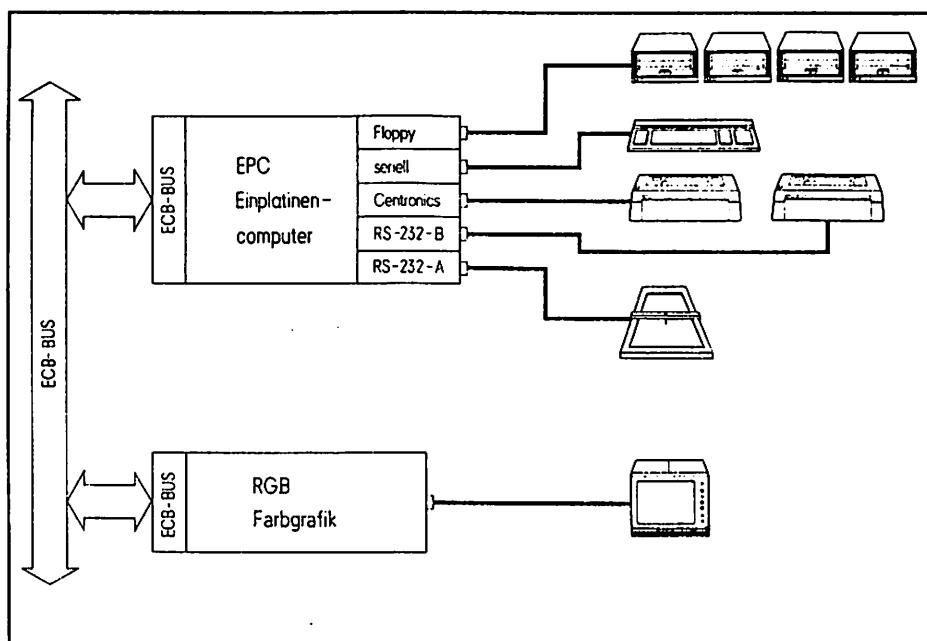

Dank der ECB-BUS Schnittstelle kann der EPC aus einer reichhaltigen Palette von Zusatzkarten erweitert werden. Zusätzlich notwendig wird dann eine ECB-BUS Rückwandverdrahtung und ein Einschubgehäuse. Es kann wahlweise ein Terminal über RS-232 oder über den ECB-BUS eine Video-Karte mit separatem Monitor und Tastatur angeschlossen werden.

### I/O Baugruppe

Sämtliche auf dem EPC befindlichen Funktionseinheiten wie RAM, Floppy und I/O können auch von einer externen CPU angesprochen werden. Der EPC lässt sich so in ein bereits bestehendes ECB-System einstecken und als I/O und RAM Karte ansprechen. Dies ermöglicht einen gezielten Test der Baugruppe beim Aufbau. Ebenso kann auf diese Weise spezielle Software für den EPC in einem bestehenden System entwickelt und getestet werden.

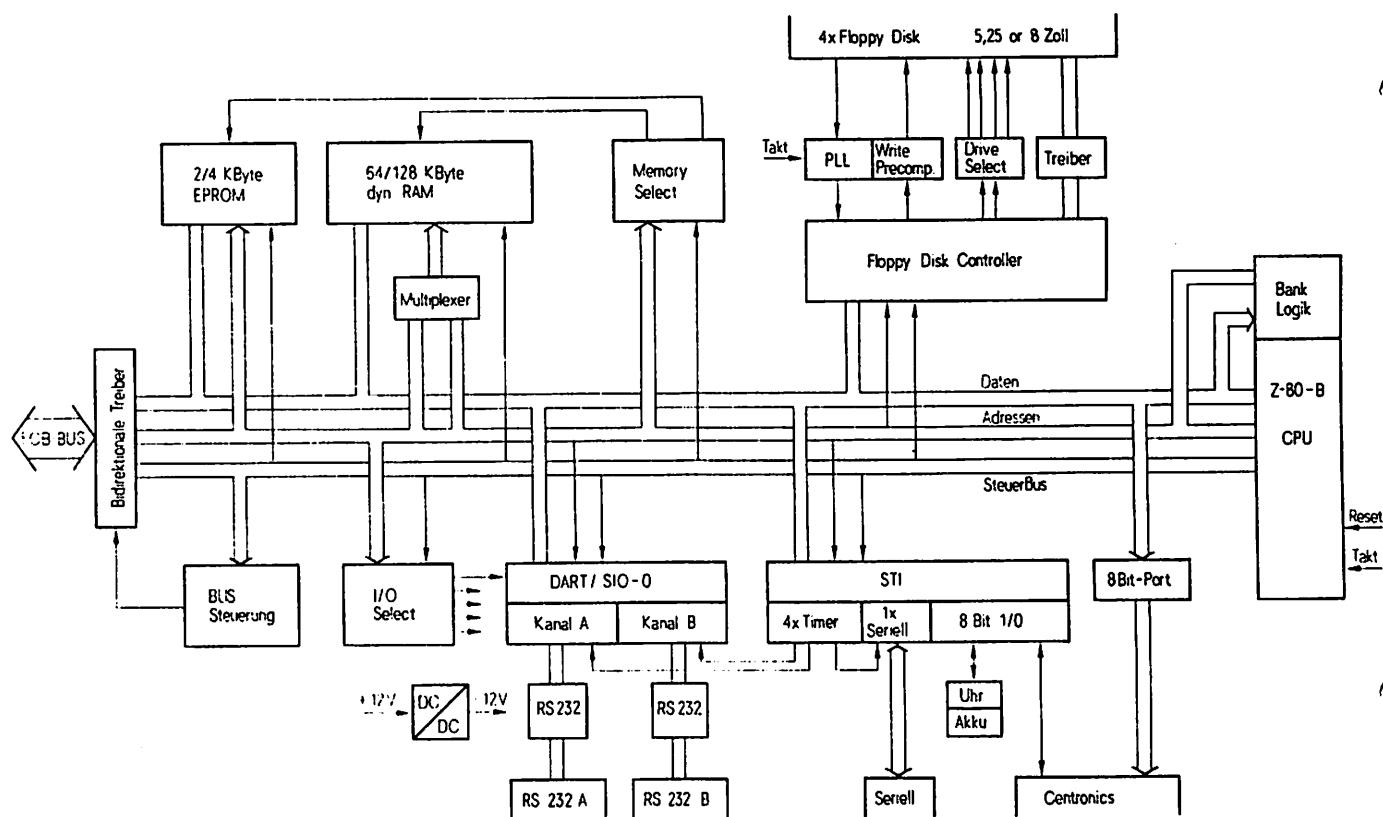

### Schaltungsübersicht

### 1 M-Byte Adressbereich

Eine Banking-Schaltung erzeugt vier zusätzliche Adressen A16-A19 und vergrößert somit den maximalen Adressbereich auf 1 M-Byte. Über einfache I/O-Befehle kann zwischen 16 verschiedenen 64K Pages umgeschaltet werden.

### Der Speicher

Der EPC verfügt über getrennte ROM- und RAM-Bereiche. Der RAM-Speicher lässt sich in zwei Schritten zu 64 K-Byte auf maximal 128

K-Byte ausbauen. Er belegt standardmäßig die untersten beiden Pages im 1 M-Byte Adressbereich. Eine 24 polige Fassung nach JEDEC kann wahlweise mit einem 2 bzw. 4 K-Byte großen Festwertspeicherbestückt werden und belegt normalerweise die untersten Adressen. Der verfügbare Speicher läßt sich in Blöcken zu 16 K-Byte beliebig im 1 M-Byte Bereich anordnen.

#### **Die Disketten Steuerung**

Der EPC ist in der Lage maximal 4 Laufwerke gemischt zwischen 3 und 8 Zoll zu verwalten. Alle gängigen Formate wie FM/MFM, SS/DS sowie Größe und Anzahl der Sektoren können softwaremäßig eingestellt werden. Am vorderen Kartenrand wird eine Shugart kompatible Schnittstelle bereitgestellt, die den direkten Anschluß der Laufwerke über ein Flachbandkabel gestattet.

Besonderer Wert wurde auf die sichere Umwandlung des Datenstroms von und zur Diskette gelegt. Beim Lesen gewährleistet eine integrierte PLL-Schaltung, beim Schreiben eine Precompensation-Schaltung den sicheren Datentransport. Eine Motor ein/aus Schaltung sorgt für eine lange Lebensdauer der Disketten und einen geräuscharmen Betrieb.

#### **I/O Schnittstellen**

Alle Schnittstellen sind am vorderen Kartenrand der Baugruppe auf 2-reihigen Postensteckern herausgeführt. Die Belegung wurde dabei so gewählt, daß Normstecker über Flachbandkabel in Schneidklemmtechnik direkt 1:1 gequetscht werden können.

Eine parallele Schnittstelle nach der Centronics Norm erlaubt den Anschluß eines Druckers.

Zwei serielle, nach RS-232/V24 gepufferte, Schnittstellen sind in der Lage ein asynchrones Datenformat in Vollduplexbetrieb zu liefern. Die Pufferung umfaßt neben dem Datenstrom auch die Signale CTS und RTS. Die dafür notwendige -12 Volt Spannung wird auf der Karte über einen DC-DC Wandler erzeugt. Die Baudrate läßt sich für beide Kanäle getrennt frei programmieren. Wahlweise ist auch eine synchrone Datenübertragung für die Formate IBM BiSynch, HDLC oder SDLC möglich.

Eine dritte serielle Schnittstelle mit TTL-Pegel eignet sich ebenfalls für asynchrone vollduplex Datenübertragung.

#### **Die Echtzeituhr**

Ein akku gepufferter Uhrenbaustein stellt dem System Echtzeit zur Verfügung. Diese kann unter CP/M Plus in Dateien eingebunden werden. Folgende Angaben stehen zur Verfügung: (Schalt-)Jahr, Monat, Wochentag, Tag, Stunde, Minute und Sekunde.

## Hardwarebeschreibung

### Stromversorgung

Die Karte benötigt zwei Betriebsspannungen: +5 und +12 Volt, wobei die +12 Volt nur für die RS-232 Schnittstelle erforderlich sind. -12 V werden von einem Spannungsinverter ICL 7660 (IC 33) erzeugt. Dem RS-232 Treiber MC 1488 (IC 36) werden somit ca. +/- 9 Volt bereit gestellt.

### Takt

Auf der Karte befinden sich zwei Quarzoszillatoren aufgebaut aus einem LS 626 Baustein und zwei Quarzen.

Der Systemtakt (6 MHz) wird direkt aus dem Oszillator abgeleitet und über eine Transistor-Treiberstufe aktiv auf High- Potential gezogen. IC 05 (74 LS 194) teilt den Systemtakt durch den Faktor zwei und versorgt damit den Timer Eingang TCLK des STI Bausteins (IC 26).

Der zweite Oszillator erzeugt den Takt (16 MHz) für den Floppy Interface Baustein FDC 9229 (IC 23).

### Reset

Ein Power-up Reset wird mittels eines RC Gliedes und zwei LS 14 Gatter (IC 19) erzeugt und über eine Open-Collector-Stufe auf PWCLR (Pin 26c am BUS-Stecker) geführt. Dieses Signal wird zum Zurücksetzen der CPU, STI, DART, FDC und dem LS 173 (Banking) benutzt. Der Eingang RESET am BUS-Stecker (31c) kann zum Anschluß eines Reset Schalters verwendet werden.

### Wait

Die Wait Schaltung kann bei I/O- und Speicheroperationen einen Wait-Stait einfügen. Der Eingang (Pin 10) des 74 LS 194 (IC 05) ist mit dem Wait-Request Signal des I/O- und des Memory-PROMs beschaltet. Wird dieses aktiv, wechselt IC 05 vom Load- in den Shift-Zustand über. Mit der nächsten steigenden Flanke des Systemtaktes wird ein Wait Stait ausgegeben.

Durch Programmieren des I/O PROM's kann festgelegt werden bei welchem der insgesamt 256 I/O Adressen ein Wait-Zyklus generiert wird. Der Memory PROM erlaubt es jedem 16 K-Byte Speicherblock innerhalb des 1 M-Byte Speicherbereichs ein Wait zuzuordnen. Standardmäßig wird bei jedem I/O-Zugriff (Ausnahme uPD 765) und bei Speicherzugriffen auf den BOOT-EPROM jeweils ein Wait-Stait eingefügt. Speicherzugriffe auf externe Speicherbaugruppen und den internen dynamischen RAM-Speicher verursachen keine Wait's.

### **Banking Speicher Verwaltung**

Diese Schaltung erlaubt es der CPU 1 M-Byte Speicher direkt zu adressieren. Ein 4 Bit Ausgabeport IC 14 (74 LS 173) erzeugt die vier Adressen A16-A19 (Pageadressen). Über I/O-Ausgabe-Befehle (D0 = A16, D3 = A19) läßt sich der Inhalt dieses Ports und damit die Bank-Adresse bestimmen.

Der Memory-PROM ist standardmäßig so ausgelegt, daß die obersten 16 K-Byte im 64 K-Byte Adressraum der CPU unabhängig von den Adressen A16-A19 eingeblendet sind. Beim Wechsel auf eine andere Page werden also nur die untersten 48 K-Byte ausgetauscht.

Nach einem Reset ist der LS 173 Baustein zurückgesetzt und die unterste 64 K-Byte Page wird angesprochen.

### **Memory Select**

Zur Adress-Dekodierung des 24 poligen Byte-Wide Sockel und der 128 K-Byte RAM wird ein 256x4 PROM (IC 13) verwendet. Durch entsprechende Programmierung kann die Adresslage der beiden Speicher bestimmt werden. Die Adresslage läßt sich dabei in 16 K-Byte Schritten frei im maximal möglichen Adressraum von 1 M-Byte bestimmen. Der BOOT Eingang am PROM erlaubt das Ein- und Ausschalten einzelner Speicherbereiche über die System-Software. Der Memory PROM ist standardmäßig so programmiert, daß der auf der Karte befindliche RAM die untersten 128 K-Byte belegt. Der EPROM ist den untersten 16 K-Byte überlagert. Führt der BOOT Eingang High Pegel, ist der EPROM eingeblendet. Wird I7 des STI Bausteins auf Low Pegel programmiert, wird der BOOT-EPROM abgeschaltet und der adressgleiche 16 K-RAM Speicher aktiviert. Der überhalb von 04000H liegende RAM ist unabhängig von dem BOOT Eingang immer aktiv.

In Abhängigkeit der 8 Eingangssignale und der beiden CE Signale werden die 4 Ausgänge RAS1, RAS2, MEM-SEL und CE-EPROM aktiv (Low) geschaltet:

Zwei der Ausgänge werden direkt als RAS Signale für die beiden 64 K-Byte RAM Blöcke benutzt. Diese sind aktiv, wenn ein Speicherzugriff auf die entsprechende Adresslage oder ein Refresh erfolgt. Der Ausgang M-SEL führt Low Pegel, wenn auf einen internen Speicher des EPC zugegriffen wird und dient zur BUS-Steuerung. Dieses Signal wird als Open Collector Ausgang auch an den BUS-Stecker DESLCT (Pin 26a) geführt. Das CAS Signal für den dynamischen Speicher wird ebenfalls aus diesem Signal abgeleitet.

Das CE-Signal für den 24 poligen Sockel wird an die Wait Schaltung weitergeleitet, welche einen Wait-Start generiert.

### Signalbelegung des Memory PROMs IC 13 (24 SA 10):

|    |        |      |    |        |               |

|----|--------|------|----|--------|---------------|

| A7 | Pin 15 | A15  | D3 | Pin 9  | CE EPROM      |

| A6 | Pin 1  | BOOT | D2 | Pin 10 | RAS 1         |

| A5 | Pin 2  | A14  | D1 | Pin 11 | Memory Select |

| A4 | Pin 3  | A19  | D0 | Pin 12 | RAS 0         |

| A3 | Pin 4  | A16  |    |        |               |

| A2 | Pin 7  | RFSH |    |        |               |

| A1 | Pin 6  | A18  |    |        |               |

| A0 | Pin 5  | A17  |    |        |               |

### Der dynamische Speicher

Als Massenspeicher werden kostengünstige dynamische 64K \* 1 Speicher eingesetzt. Wichtig ist, daß nur RAM's mit einem 7 Bit Refresh (128 Refresh-zyklen) und bei 6 MHz Systemfrequenz 150ns Typen verwendet werden. Wahlweise können 8 (64 K-Byte) oder 16 (128 K-Byte) Speicher bestückt werden.

Um 128 K-Byte RAM auf diesem kleinen Raum zu realisieren, werden jeweils zwei 64 K-Bit Speicher übereinander montiert. Pin 4 (RAS) des oberen Speichers ist nicht mit dem unteren verbunden, sondern wird getrennt über den unbelegten Pin 1 herausgeführt. Der Anschluß 1 darf dabei keine interne Verbindung haben. Alle anderen Anschlüsse werden direkt mit dem unteren IC verbunden.

### Ansteuerung

Die dynamischen Speicher werden im 'early Write' Modus betrieben. Das heißt, bei einem Schreibzugriff ist das Write Signal bereits mit der fallenden Flanke von CAS aktiv (Low). Dies hat den Vorteil, daß die Datentreiber (D out) beim Schreiben im Tri-State Zustand bleiben. Din und Dout müssen deshalb nicht getrennt gepuffert werden und lassen sich so einfach verbinden.

Die Adressen A0-A15 werden über zwei invertierende Adressmultiplexer auf die Speicher geschaltet. Wichtig ist, daß hier unbedingt Schottky Bausteine eingesetzt werden.

### Precharge Schaltung

Um bei 6 MHz Systemfrequenz einen einwandfreien Betrieb mit den dynamischen Speichern zu gewährleisten ist eine Precharge-Extension-Schaltung erforderlich. Diese hat zur Aufgabe den Precharge beim M1 Zyklus zwischen Speicherzugriff (Opcode Fetch) und Refreshzugriff während T3 aufzuweiten. Wird auf den dynamischen Speicher zugegriffen, beendet IC 18 (74 LS 173) den Opcode Fetch mit der steigenden Flanke von T3 vorzeitig.

### **Festwertspeicher**

Als Festwertspeicher kann wahlweise ein 2- bzw. 4-K-Byte EPROM eingesetzt werden. Der 24 polige Sockel ist dabei nach der JEDEC Norm ausgeführt. Pin 21 wird wahlweise mit +5V (2 K-Byte) oder A11 (4 K-Byte) beschaltet (am Pin 21 auf der Lötseite). Standardmäßig ist Pin 21 mit +5V verbunden.

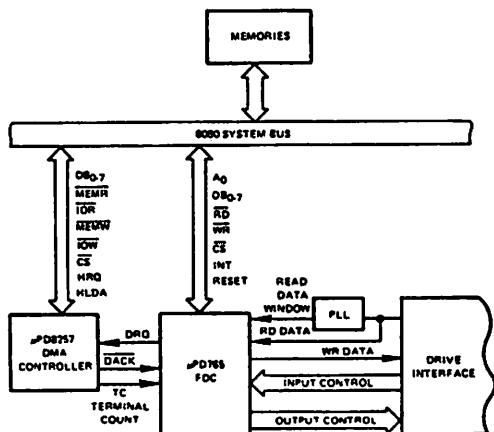

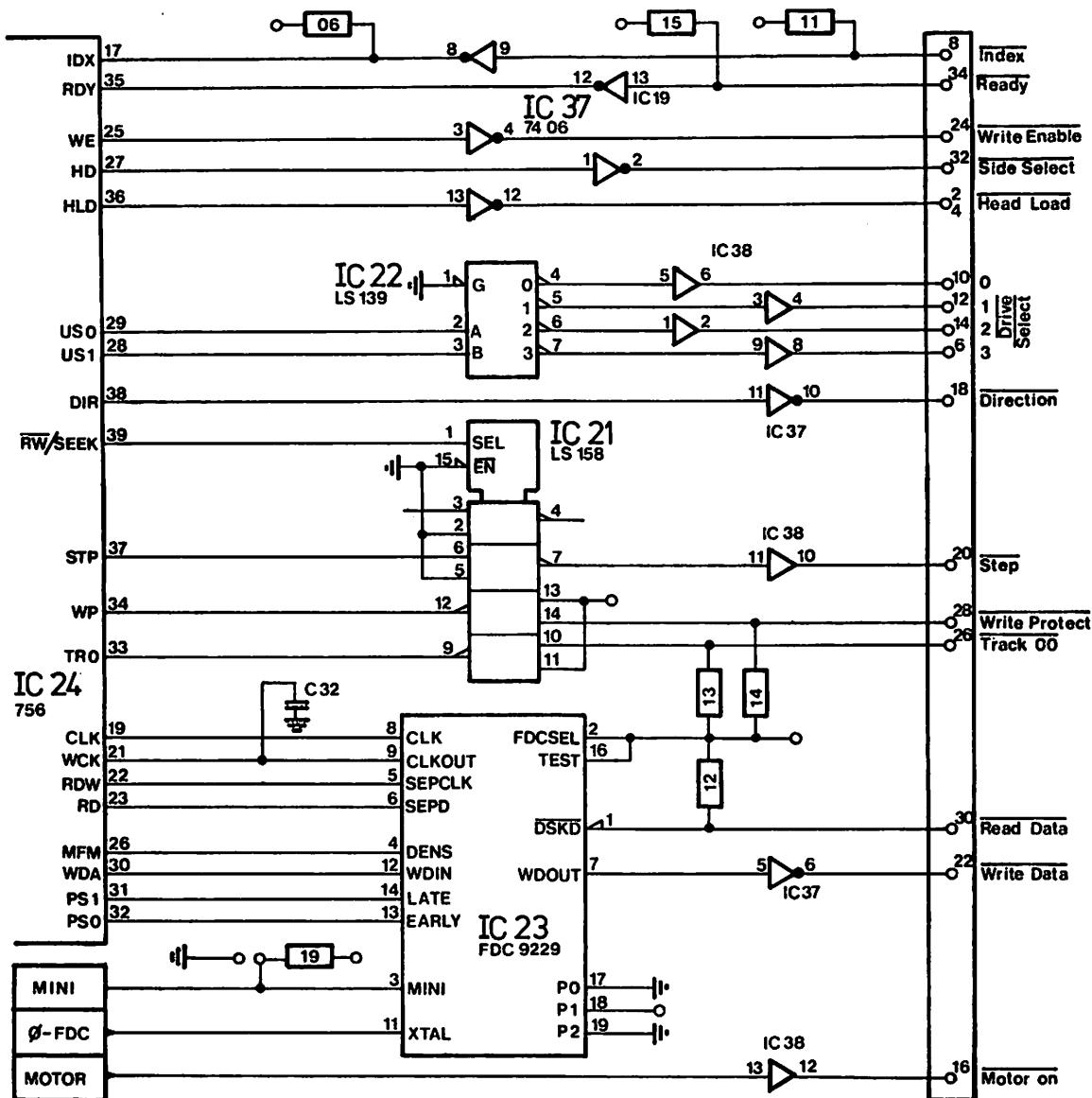

### **Die Floppy Steuerung**

#### **Der Controller**

Als Floppy Controller wurde der uPD 765 von NEC ausgewählt. Er ist in der Lage die unter CP/M 3.0 notwendigen Multi-Sector und Multi-Track Operationen zu unterstützen. Seine hohe Intelligenz entlastet die Software erheblich. So ist er in der Lage selbstständig Disketten zu formatieren und Informationen über den Zustand von 4 Laufwerken zwischenzuspeichern. Das Einstellen von irgendwelchen Trimmern entfällt vollständig.

Während des Transfers von und zur Diskette wird der uPD 765 im Polling Verfahren betrieben. Der Systemtakt von 6 MHz erlaubt es 8 Zoll Double Density Disketten mit diesem Verfahren einwandfrei zu bearbeiten.

#### **Der Interface Baustein**

Den einwandfreien Datentransfer von und zur Diskette übernimmt der Baustein FDC 9229 (IC 23). Beim Lesen von Diskette sorgt eine integrierte "Phase Lock Loop" Schaltung für die Aufbereitung des seriellen Datenstroms. Beim Schreiben gewährleistet eine Write Precompensations Schaltung die sichere Aufzeichnungen. Der Precompensations Wert beträgt bei MINI Laufwerken 250 ns und bei Standard Drives 125 ns. Prinzipiell können über die Eingänge P0 - P2 auch andere Werte eingestellt werden.

Der Eingang MINI am 9229 erlaubt es zwischen 5.25 und 8 Zoll Laufwerken umzuschalten. Im wesentlichen wird dabei die Datentransferrate von 250 KBit/sec bei 5.25 Zoll auf 500 KBit bei 8 Zoll umgeschaltet. Der Zustand des MINI Eingangs lässt sich über eine Lötbrücke (unter dem Akku auf der Lötseite) bestimmen und über den Ausgang I5 des STI Bausteins von der Software schalten.

## Signalbelegung des 34 poligen Floppysteckers:

|   |    |    |                |

|---|----|----|----------------|

| ! | 01 | 02 | Head Load      |

| ! | 03 | 04 | Head Load      |

| ! | 05 | 06 | Drive Select 3 |

| ! | 07 | 08 | Index          |

| ! | 09 | 10 | Drive Select 0 |

| ! | 11 | 12 | Drive Select 1 |

|   | 13 | 14 | Drive Select 2 |

| G | 15 | 16 | Motor on       |

| N | 17 | 18 | Direction      |

| D | 19 | 20 | Step           |

|   | 21 | 22 | Write Data     |

| ! | 23 | 24 | Write Enable   |

| ! | 25 | 26 | Track 00       |

| ! | 27 | 28 | Write Protect  |

| ! | 29 | 30 | Read Data      |

| ! | 31 | 32 | Side Select    |

| ! | 33 | 34 | Ready          |

## I/O Select

Die Dekodierung der I/O Bausteine übernimmt ein 256x4 PROM (IC 08) und ein 74 LS 139 TTL Baustein (IC 22). Durch Programmierung des PROM's lassen sich die I/O-Bausteine beliebig im maximalen I/O-Adressbereich (max. 256) anordnen.

## Signalbelegung des I/O PROMs IC 08 (24 SA 10):

|    |        |    |    |        |                      |

|----|--------|----|----|--------|----------------------|

| A7 | Pin 15 | M1 | D3 | Pin 9  | CE Cent,DART,173,FDC |

| A6 | Pin 1  | A1 | D2 | Pin 10 | Wait Request         |

| A5 | Pin 2  | A3 | D1 | Pin 11 | CE STI               |

| A4 | Pin 3  | A2 | D0 | Pin 12 | I/O Select           |

| A3 | Pin 4  | A7 |    |        |                      |

| A2 | Pin 7  | A4 |    |        |                      |

| A1 | Pin 6  | A5 |    |        |                      |

| A0 | Pin 5  | A6 |    |        |                      |

In Abhängigkeit der acht Eingangssignale M1 und A1 - A7 werden vier Ausgangssignale erzeugt:

Das Signal IO-SEL führt Low Pegel, wenn auf einen internen I/O Baustein zugegriffen wird und dient zur BUS-Steuerung.

Ein Wait-Request-Signal das an die Wait-Schaltung geführt ist gestattet jedem der 256 I/O Adressen gezielt einen Wait-Stait zuzuordnen.

Die beiden verbleibenden Ausgänge dienen als Chip Enable Signale für die I/O Bausteine.

Ein CE wird direkt an den STI Baustein geführt der 16 I/O-Adressen belegt. Die oberen vier Adreßbits A7-A4 können frei durch Programmierung des PROMs bestimmt werden.

Die Z80-DART, der FDC, der Centronics Datenport und die Banking Schaltung belegen ebenfalls 16 I/O Adressen. Die oberen vier Adressen dieses Blocks können über den PROM festgelegt werden. Die Dekodierung der Adressen A2 und A3 übernimmt IC 22 (74 LS 139). Innerhalb des 16 Byte Blocks haben die vier I/O-Baugruppen folgende Adreßlage:

|           |                       |

|-----------|-----------------------|

| XXXX 00xx | Centronics Datenport  |

| XXXX 01xx | Z-80 DART             |

| XXXX 10xx | Banking Port (LS 173) |

| XXXX 11xx | FDC 765               |

Die I/O Bausteine belegen standardmäßig folgende Adressen:

|       |                         |

|-------|-------------------------|

| 00-0F | Z-80 STI                |

| 10    | Centronics Data-Output  |

| 14-17 | Z-80 DART/SIO           |

| 18    | Banking Output (LS 173) |

| 1C,1D | FDC Controller uPD 765  |

## Schnittstellen

### a, Centronics

Die Centronics Schnittstelle erlaubt es auf einfache Weise einen Drucker anzuschließen. Der 8-Bit Datenstrom zum Printer wird über 8 D-Flip-Flops einem LS 374 Baustein (IC 34) erzeugt. Der Strobe Ausgang wird von dem STI-Baustein erzeugt und über ein Gatter (74 LS 367) gepuffert. Die Eingänge Paper empty und Acknowledge sind ebenfalls mit der STI verbunden. Busy ist an den DART-Baustein geführt. Alle Signale können somit Interrupts auslösen.

Sämtliche Signale sind auf einen 26 poligen Stecker nach Centronics Norm geführt.

## Belegung des 26 poligen Centronics Steckers:

|             |    |    |   |

|-------------|----|----|---|

| Strobe      | 01 | 02 | ! |

| D0          | 03 | 04 | ! |

| D1          | 05 | 06 | ! |

| D2          | 07 | 08 |   |

| D3          | 09 | 10 | G |

| D4          | 11 | 12 | N |

| D5          | 13 | 14 | D |

| D6          | 15 | 16 |   |

| D7          | 17 | 18 | ! |

| Acknowledge | 19 | 20 | ! |

| Busy        | 21 | 22 | ! |

| Paper Empty | 23 | 24 |   |

|             | 25 | 26 |   |

## b, RS-232

Es stehen zwei serielle asynchrone vollduplex Kanäle zur Verfügung. Alternativ ist durch Austausch der Z80-DART durch eine Z80-SIO-0 auch synchrone Datenübertragung möglich. Die Baudrate ist softwaremäßig getrennt für beide Kanäle einstellbar. Channel A der DART wird von Timer D (STI) und Channel B von Timer C mit dem Baudrate Takt versorgt.

Receive- und Transmit-Data, Clear to Send und Request to Send sind bei beiden Kanälen auf RS-232 Pegel gepuffert und getrennt für jeden Kanal auf zwei 14 polige Pfostenstecker geführt. Die Belegung dieser Stecker entspricht der RS-232 Norm. Über ein Kabel in Schneid-Klemm-Technik lassen sie sich direkt mit einem 25 poligen D-Stecker verbinden.

## Belegung der beiden 14 poligen RS-232 Stecker:

|                 |   |    |    |

|-----------------|---|----|----|

|                 | 1 | 01 | 02 |

| Receive Data    | 2 | 03 | 04 |

| Transmit Data   | 3 | 05 | 06 |

| Request to Send | 4 | 07 | 08 |

| Clear to Send   | 5 | 09 | 10 |

|                 | 6 | 11 | 12 |

| GND             | 7 | 13 | 14 |

**c, seriell 5 Volt TTL**

Eine weitere serielle asynchrone vollduplex Schittstelle mit TTL Pegel wird auf einem 10 poligen Stecker bereit gestellt. Selbige läßt sich z. B. zum Anschluß einer Tastatur verwenden. Die Baudrate ist auch hier softwaremäßig einstellbar (Timer B, STI).

Die Belegung ist wie folgt:

|   |    |    |             |

|---|----|----|-------------|

| ! | 01 | 02 | Vcc         |

| G | 03 | 04 | NMI         |

| N | 05 | 06 | GND         |

| D | 07 | 08 | seriell in  |

| ! | 09 | 10 | seriell out |

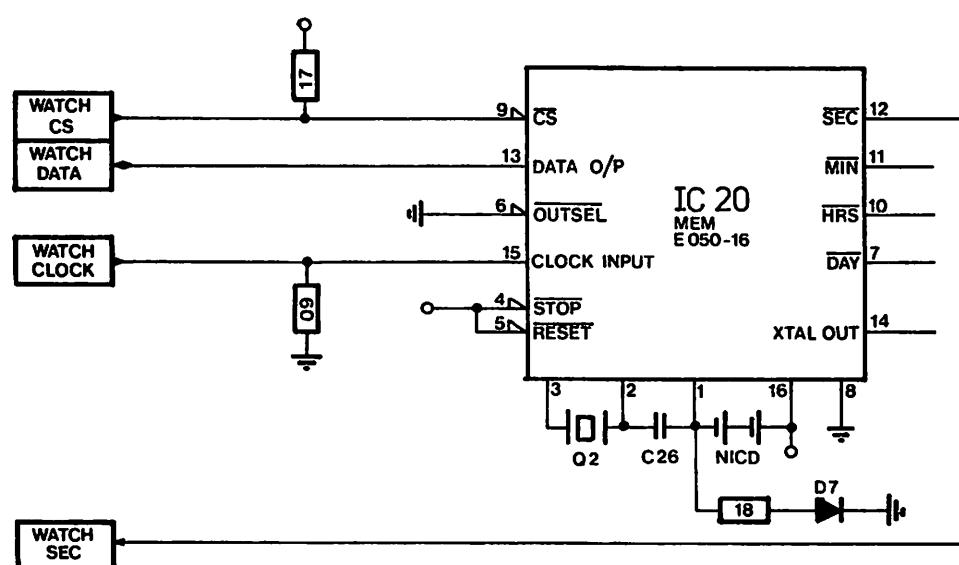

**Echtzeituhr**

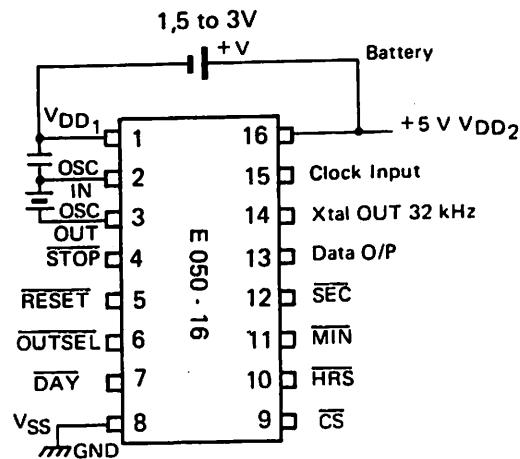

Der Uhrenbaustein E 050-16 erlaubt die Angabe von Sekunden, Minuten, Stunden, Tag, Wochentag, Monat und (Schalt-)Jahr. Ein implementierter Akku ermöglicht den Betrieb auch bei ausgeschaltetem Gerät. Über den Trimmer C27 läßt sich die Quarzfrequenz exakt auf 32,768 kHz abgleichen. Die Steuersignale des Uhrenbausteins werden über die Z-80 DART und STI beschaltet. Der Daten austausch geschieht dabei seriell über die Leitung DATA O/P. Ein Sekunden Takt ist an den Eingang I4 der STI geführt. I4 dient Timer A als Eingang im Event count mode. Entsprechend programmiert erzeugt der Ausgang TA des Timers das Motor on/off Signal für die Laufwerke, indem er den an I4 anliegenden Sekundenpuls herabzählt und bei Time-Out den Motor ausschaltet.

**Beschaltung MEM E 050-16**

|              |              |                              |           |

|--------------|--------------|------------------------------|-----------|

| OUT STOP:    | Vcc          | Inaktiv                      | Input     |

| RESET:       | Vcc          | Inaktiv                      | Input     |

| OUTSEL:      | GND          | Activ                        | Input     |

| CHIP SELECT: | DTRA         | Dart A Data Terminal Ready   | Input     |

| SECONDS:     | STI I4       | Timer A erzeugt Motor on/off | Output    |

| DATA O/P:    | STI I0       | Serieller Datenstrom         | In/Output |

| CLOCK:       | DTRB         | Dart B Data Terminal Ready   | Input     |

| MIN, HRS:    | unbeschaltet |                              | Outputs   |

**Serial Timer Interrupt Controller STI**

Der STI-Baustein stellt 8 parallel I/O-Kanäle, 1 USART und 4 Timer-Zeitgeber zur Verfügung.

**Belegung der I/O Leitungen I0 - I7:****Echtzeituhr**

|    |        |       |                                 |

|----|--------|-------|---------------------------------|

| I0 | Pin 8  | I/O   | serieller Datenstrom            |

| I4 | Pin 14 | Input | Sekunden Puls für Timer A Input |

**Centronics**

|    |        |        |                          |

|----|--------|--------|--------------------------|

| I1 | Pin 9  | Output | Strobe, Low active       |

| I3 | Pin 11 | Output | Paper empty, High active |

| I6 | Pin 14 | Input  | Acknowledge, Low active  |

**Floppy Controller**

|    |        |        |                                 |

|----|--------|--------|---------------------------------|

| I2 | Pin 10 | Output | Terminal Count 765, High active |

| I5 | Pin 13 | Output | MINI, High = MINI, Low = Std.   |

**BOOT**

|    |        |        |                                         |

|----|--------|--------|-----------------------------------------|

| I7 | Pin 15 | Output | BOOT, High = EPROM ein, Low = EPROM aus |

|----|--------|--------|-----------------------------------------|

**Timers**

|    |       |        |                             |

|----|-------|--------|-----------------------------|

| TA | Pin 1 | Output | Motor on/off FDD's          |

| TB | Pin 2 | Output | Baudrate for STI USART      |

| TC | Pin 3 | Output | Baudrate for DART Channel B |

| TD | Pin 4 | Output | Baudrate for DART Channel A |

Der STI Baustein ist derzeit nur in der A Version (4 MHz) erhältlich. Es ist deshalb bei Systemfrequenzen von 6 MHz nicht möglich die Vektor Interrupt Fähigkeiten des Bausteins auszunützen.

**BUS Schnittstelle**

Große Bedeutung wurde dem BUS-Anschluß zugemessen. So sind Daten, Adressen und Steuersignale über 4 Treiber Bausteine (74 LS 245) bidirektional gepuffert. Das heißt es können externe Baugruppen wie eine CPU oder eine DMA auf den interner Speicher bzw. I/O Baugruppen zugreifen. Der DART und STI Baustein sind in der Lage einen Vektor-Interrupt an eine externe CPU weiterzuleiten.

Die Steuerung des Daten- und Adreß-bus wird von einem 256x4 PROM (IC 06) durchgeführt. In Abhängigkeit der acht Eingangssignale werden vier Ausgangssignale erzeugt, welche die Richtung und den Tri-State Zustand der Daten- und Adreß-treiber bestimmen.

Die Signalbelegung des BUS-Steuerproms IC 06 ist wie folgt:

|    |        |            |    |        |            |

|----|--------|------------|----|--------|------------|

| A7 | Pin 15 | BUSAK      | D3 | Pin 9  | EN 173     |

| A6 | Pin 1  | RD         | D2 | Pin 10 | DIR DATA   |

| A5 | Pin 2  | IEI        | D1 | Pin 11 | EN BUS     |

| A4 | Pin 3  | IO-SEL     | D0 | Pin 12 | DIR Adress |

| A3 | Pin 4  | M1         |    |        |            |

| A2 | Pin 7  | IEO        |    |        |            |

| A1 | Pin 6  | Memory-SEL |    |        |            |

| A0 | Pin 5  | IORD       |    |        |            |

Die vier Treiber Bausteine sind grundsätzlich 'enabled'. Wird die Karte als Slave eingesetzt besteht die Möglichkeit die Treiber auch in den Tri-State Zustand zu versetzen.

Das Signal BUSAK bestimmt die Richtung der Adress und Steuerleitungen. Ist BUSAK inaktiv (High) sind die Treiber nach außen auf den BUS geschaltet. Die oberen vier Adressen A16-A19 werden getrennt angesprochen. Diese können bei aktiven BUSAK wahlweise in den Tri-State Zustand versetzt werden oder nicht (standardmäßig Tri-State).

Um die Richtung des Datenstromes festzulegen sind eine Reihe von Informationen notwendig. Hierbei muß unterschieden werden, ob die interne CPU aktiv ist oder nicht, ob auf einen internen oder externen Speicher oder I/O Baugruppe zugegriffen wird und ob ein Vektor Interrupt vorliegt.

Grundsätzlich ist der Datenstrom nach außen geschaltet. Außnahmen sind Lesebefehle, die auf externe Baugruppen zugreifen und Interrupt Acknowledge Zyklen die von externen I/O Baugruppen ausgelöst wurden.

Ist die interne CPU inaktiv geht der Datenstrom zum Karteninneren. Außnahmen sind Lesebefehle von einer externen Einheit auf Baugruppen im Karteninneren.

### Einsatz als I/O Karte

Sämtliche auf der CPU Karte befindlichen Baugruppen können auch von einer externen CPU angesprochen werden. D. h. die EPC-Baugruppe kann auch in einem bestehenden System als I/O Karte eingesetzt werden.

Zum Einsatz als I/O-Karte sind folgende Punkte zu beachten:

- 1, Der Systemtakt ist extern zuzuführen. D.h. der interne Taktgenerator muß durch Entfernen des Widerstandes R05 deaktiviert werden.

- 2, Der BUSAK Ausgang ist vom BUS abzutrennen.

- 3, Die CPU muß aus der Fassung genommen und durch eine Brücke von GND (Pin 29) nach BUSAK (Pin 23) ersetzt werden.

- 4, Es ist zu überprüfen ob das PWRCLR Signal auf dem Systembus als open Collector ausgeführt wurde. Wenn nicht, ist es vom BUS abzutrennen.

### Einsatz als Slave Prozessor

Ebenfalls ist die CPU Karte als Slave in einem Multiprozessor-Multi-User System einsetzbar. Die Karte arbeitet dabei parallel zu anderen Prozessoren in dem System ohne die Aktivitäten des Masters auf dem Systembus zu stören. Der Datenaustausch zwischen Slave und Master kann dabei mit der vollen Geschwindigkeit des Systembuses erfolgen. Der Datenaustausch erfolgt über den RAM auf der EPC Karte.

Folgende Änderungen sind vorzunehmen:

- 1, Pin 2 des Memory PROMs wird mit BUSAK beschaltet

- 2, Ein spezieller Memory PROM ist einzusetzen

- 3, Ein spezieller BUS PROM ist einzusetzen

- 4, Die Leitungen IEI, IEO, CLK, DESLCT, WAIT, INT, NMI sind nicht auf des MASTER Bus zu schalten.

- 5, Die PWRCLR Leitung muß als open Collector ausgeführt sein

- 6, BUSREQ und BUSAK sind nicht auf den BUS zu legen, sondern über zwei parallele I/O Leitungen mit dem Master zu verbinden.

Die BUSREQ Leitung dient dann als Slave Request Leitung,

die BUSAK Leitung als Slave Acknowledge Signal.

Des weiteren kann eine I/O Leitung auf der EPC-Karte mit

einer I/O Leitung des Masters verbunden werden die als Master

Request Signal dient.

Bei mehreren Slave Baugruppen in einem System empfiehlt es sich eine spezielle Rückwandverdrahtung anzufertigen.

### Funktionsweise als Slave Baugruppe

Nach einem System Reset sind sämtliche Leitungstreiber zum BUS nach beiden Richtungen im Tri-State-Zustand. Sowohl Master als auch Slave beginnen simultan und autonom zu arbeiten. Nun kann z.B. der Slave über die Master-Request Leitung die einen Interrupt im Master System auslöst Bearbeitung beantragen. Der Master muß das Slave-Request-Signal, das an BUSREQ der Slave CPU herangeführt ist, aktivieren. Die Slave CPU antwortet mit BUSAK (Slave Acknowledge), das gleichzeitig an den Memory PROM herangeführt wird. Dies hat zur Folge, daß der auf der Slave Karte befindliche Speicher in eine Adreßlage gebracht werden kann, die sich nicht mit dem Speicher des Masters überlagert. Ebenfalls werden sämtliche Treiberbausteine aktiviert. Der Master kann nun ungehindert auf den Speicher der Slave Karte zugreifen.

Nach Zurücknehmen des Slave-Request Signals und des daraus resultierenden inaktiv werden des Slave Acknowledge Signals können sowohl Master als auch Slave wieder autonom arbeiten.

**Inbetriebnahme****Terminalanschluß**

Wahlweise kann an den EPC unsere RGB Grafikkarte oder über RS-232 ein handelsübliches Terminal angeschlossen werden. Die Software überprüft beim Einschalten ob die RGB Baugruppe am BUS vorhanden ist. Falls nicht erfolgt die Ausgabe über RS-232 Channel A.

Das Übertragungsprotokoll ist standardmäßig folgendes:

Baudrate 9600, 1 Stopbit, keine Parität

**Tastaturanschluß**

Wird die RGB Grafikkarte als Ausgabeeinheit verwendet, erwartet die Standardsoftware an der seriellen TTL Schnittstelle auf dem EPC die Tastatureingabe.

Das Übertragungsprotokoll ist standardmäßig folgendes:

Baudrate 9600, 1 Stopbit, keine Parität

**Laufwerksanschluß****Head Load**

Der EPC stellt ein Head-Load Signal auf Pin 2 und 4 der Floppy-Steckerleiste zur Verfügung. Dieses Signal kann zum Laden der Köpfe herangezogen werden. Werden TEAC- Laufwerke eingesetzt, so ist die Steckbrücke **HL** und **SM** zu setzen.

Alternativ kann der Kopf der Laufwerke auch durch das Motor-On-Signal des EPC-Computers geladen werden. Dadurch werden die Kopf-Lade-Geräusche stark herabgesetzt, der Kopf bleibt jedoch länger auf der Diskette abgesenkt (trotzdem empfehlenswert!). Bei den TEAC-Laufwerken sind hierzu die Steckbrücken **HM** und **SM** zu setzen.

**Drive-Select**

Je nach gewünschter Laufwerksnummer sind die entsprechenden Jumper auf den Laufwerken zu setzen (DS0 - DS3). Laufwerk A (DS0) muß auf jeden Fall vorhanden sein. Dabei ist zu beachten, daß der Floppy-Controller uPD 765 beim 'Steppen' die Drive-Select-Leitung des gewünschten Laufwerks nur für die Zeit des 'Step'-Pulses aktiviert, da nach werden nacheinander auch die restlichen drei Drive-Select-Leitungen angesprochen, um den 'Ready-Zustand' dieser Laufwerke abzufragen. Dies kann vereinzelt zu Problemen bei Einsatz älterer 8 Zoll Laufwerke führen.

|            |                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>Pin</b> | <b>Description</b>                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            | <b>B/A.</b> <i>Channel A Or B Select</i> (input, High selects Channel B). This input defines which channel is accessed during a data transfer between the CPU and the Z-80 DART.                                                                                                                                                                           | as an interrupt acknowledge if the Z-80 DART is the highest priority device that has interrupted the Z-80 CPU.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|            | <b>C/D.</b> <i>Control Or Data Select</i> (input, High selects Control). This input specifies the type of information (control or data) transferred on the data bus between the CPU and the Z-80 DART.                                                                                                                                                     | <b>IORQ.</b> <i>Input/Output Request</i> (input from CPU, active Low). $\overline{IORQ}$ is used in conjunction with B/A, C/D, $\overline{CE}$ and $\overline{RD}$ to transfer commands and data between the CPU and the Z-80 DART. When $\overline{CE}$ , $\overline{RD}$ and $\overline{IORQ}$ are all active, the channel selected by B/A transfers data to the CPU (a read operation). When $\overline{CE}$ and $\overline{IORQ}$ are active, but $\overline{RD}$ is inactive, the channel selected by B/A is written to by the CPU with either data or control information as specified by C/D. |

|            | <b>CE.</b> <i>Chip Enable</i> (input, active Low). A Low at this input enables the Z-80 DART to accept command or data input from the CPU during a write cycle, or to transmit data to the CPU during a read cycle.                                                                                                                                        | <b>RxC.</b> <i>RxCB.</i> <i>Receiver Clocks</i> (inputs). Receive data is sampled on the rising edge of $\overline{RxC}$ . The Receive Clocks may be 1, 16, 32 or 64 times the data rate.                                                                                                                                                                                                                                                                                                                                                                                                            |

|            | <b>CLK.</b> <i>System Clock</i> (input). The Z-80 DART uses the standard Z-80 single-phase system clock to synchronize internal signals.                                                                                                                                                                                                                   | <b>RD.</b> <i>Read Cycle Status.</i> (input from CPU, active Low). If $\overline{RD}$ is active, a memory or I/O read operation is in progress.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|            | <b>CTS<sub>A</sub>, CTS<sub>B</sub>.</b> <i>Clear To Send</i> (inputs, active Low). When programmed as Auto Enables, a Low on these inputs enables the respective transmitter. If not programmed as Auto Enables, these inputs may be programmed as general-purpose inputs. Both inputs are Schmitt-trigger buffered to accommodate slow-risetime signals. | <b>RxD.</b> <i>RxD.</i> <i>Receive Data</i> (inputs, active High).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            | <b>D<sub>0</sub>-D<sub>7</sub>.</b> <i>System Data Bus</i> (bidirectional, 3-state) transfers data and commands between the CPU and the Z-80 DART.                                                                                                                                                                                                         | <b>RESET.</b> <i>Reset</i> (input, active Low). Disables both receivers and transmitters, forces $\overline{TxD}$ and $\overline{TxB}$ marking, forces the modem controls High and disables all interrupts.                                                                                                                                                                                                                                                                                                                                                                                          |

|            | <b>DCDA, DCDB.</b> <i>Data Carrier Detect</i> (inputs, active Low). These pins function as receiver enables if the Z-80 DART is programmed for Auto Enables; otherwise they may be used as general-purpose input pins. Both pins are Schmitt-trigger buffered.                                                                                             | <b>RIA, RIB.</b> <i>Ring Indicator</i> (inputs, Active Low). These inputs are similar to $\overline{CTS}$ and $\overline{DCD}$ . The Z-80 DART detects both logic level transitions and interrupts the CPU. When not used in switched-line applications, these inputs can be used as general-purpose inputs.                                                                                                                                                                                                                                                                                         |

|            | <b>DTRA, DTRB.</b> <i>Data Terminal Ready</i> (outputs, active Low). These outputs follow the state programmed into the DTR bit. They can also be programmed as general-purpose outputs.                                                                                                                                                                   | <b>RTSA, RTSB.</b> <i>Request to Send</i> (outputs, active Low). When the RTS bit is set, the $\overline{RTS}$ output goes Low. When the RTS bit is reset, the output goes High after the transmitter empties.                                                                                                                                                                                                                                                                                                                                                                                       |

|            | <b>IEI.</b> <i>Interrupt Enable In</i> (input, active High) is used with IEO to form a priority daisy chain when there is more than one interrupt-driven device. A High on this line indicates that no other device of higher priority is being serviced by a CPU interrupt service routine.                                                               | <b>TxC.</b> <i>TxC.</i> <i>Transmitter Clocks</i> (inputs). $\overline{TxD}$ changes on the falling edge of $\overline{TxC}$ . The Transmitter Clocks may be 1, 16, 32 or 64 times the data rate; however, the clock multiplier for the transmitter and the receiver must be the same. The Transmit Clock inputs are Schmitt-trigger buffered. Both the Receiver and Transmitter Clocks may be driven by the Z-80 CTC Counter Time Circuit for programmable baud rate generation.                                                                                                                    |

|            | <b>IEO.</b> <i>Interrupt Enable Out</i> (output, active High). IEO is High only if IEI is High and the CPU is not servicing an interrupt from this Z-80 DART. Thus, this signal blocks lower priority devices from interrupting while a higher priority device is being serviced by its CPU interrupt service routine.                                     | <b>TxD.</b> <i>TxD.</i> <i>Transmit Data</i> (outputs, active High).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | <b>INT.</b> <i>Interrupt Request</i> (output, open drain, active Low). When the Z-80 DART is requesting an interrupt, it pulls $\overline{INT}$ Low.                                                                                                                                                                                                       | <b>W/RDY<sub>A</sub>, W/RDY<sub>B</sub>.</b> <i>Wait/Ready</i> (outputs, open drain when programmed for Wait function, driven High and Low when programmed for Ready function). These dual-purpose outputs may be programmed as Ready lines for a DMA controller or as Wait lines that synchronize the CPU to the Z-80 DART data rate. The reset state is open drain.                                                                                                                                                                                                                                |

|            | <b>M1.</b> <i>Machine Cycle One</i> (input from Z-80 CPU, active Low). When M1 and $\overline{RD}$ are both active, the Z-80 CPU is fetching an instruction from memory; when M1 is active while $\overline{IORQ}$ is active, the Z-80 DART accepts M1 and $\overline{IORQ}$                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

**Functional Description**

The functional capabilities of the Z-80 DART can be described from two different points of view: as a data communications device, it transmits and receives serial data, and meets the requirements of asynchronous data communications protocols; as a Z-80 family peripheral, it interacts with the Z-80 CPU and other Z-80 peripheral circuits, and shares the data, address and control buses, as well as being a part of the Z-80 interrupt structure. As a peripheral to other microprocessors, the Z-80 DART offers valuable features such as non-vectorized interrupts, polling and simple hand-shake capability.

**Communications Capabilities.** The Z-80 DART provides two independent full-duplex channels for use as an asynchronous receiver/transmitter. The following is a short description of receiver/transmitter capabilities. For more details, refer to the Asynchronous Mode section of the *Z-80 S/I/O Technical Manual*. The Z-80 DART offers transmission and reception of five to eight bits per character, plus optional even or odd parity. The transmitter can supply one, one and a half or two stop bits per character and can provide a break output at any time. The receiver break detection logic interrupts the CPU both at the start and end of a received break. Reception is protected from spikes by a transient spike rejection mechanism that checks the signal one-half a bit time after a Low level is detected on the Receive Data input. If the Low does not persist—as in the case of a transient—the character assembly process is not started.

**I/O Interface Capabilities.** The Z-80 DART offers the choice of Polling, Interrupt (vectorized or non-vectorized) and Block Transfer modes to transfer data, status and control information to

The first part of the following functional description introduces Z-80 DART data communications capabilities; the second part describes the interaction between the CPU and the Z-80 DART.

The Z-80 DART offers RS-232 serial communications support by providing device signals for external modem control. In addition to dual-channel Request To Send, Clear To Send, and Data Carrier Detect ports, the Z-80 DART also features a dual channel Ring Indicator (RIA, RIB) input to facilitate local/remote or station-to-station communication capability.

Framing errors and overrun errors are detected and buffered together with the character on which they occurred. Vectored interrupts allow fast servicing of interrupting conditions using dedicated routines. Furthermore, a built-in checking process avoids interpreting a framing error as a new start bit: a framing error results in the addition of one-half a bit time to the point at which the search for the next start bit is begun.

The Z-80 DART does not require symmetric Transmit and Receive Clock signals—a feature that allows it to be used with a Z-80 CTC or any other clock source. The transmitter and receiver can handle data at a rate of 1, 1/16, 1/32 or 1/64 of the clock rate supplied to the Receive and Transmit Clock inputs. When using Channel B, the bit rates for transmit and receive operations must be the same because  $\overline{RxC}$  and  $\overline{TxC}$  are bonded together ( $\overline{RxC}B$ ).

and from the CPU. The Block Transfer mode can be implemented under CPU or DMA control.

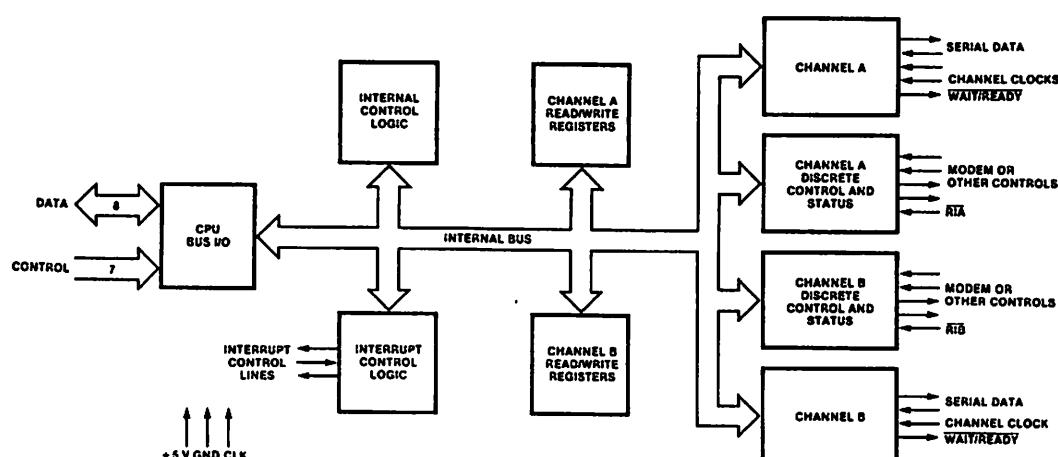

Figure 3. Block Diagram

**Functional Description**

(Continued)

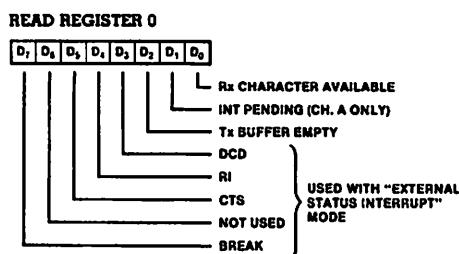

**POLLING.** There are no interrupts in the Polled mode. Status registers RR0 and RR1 are updated at appropriate times for each function being performed. All the interrupt modes of the Z-80 DART must be disabled to operate the device in a polled environment.

While in its Polling sequence, the CPU examines the status contained in RR0 for each channel; the RR0 status bits serve as an acknowledge to the Poll inquiry. The two RR0

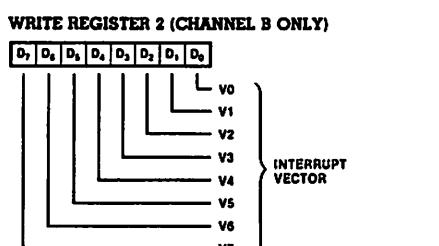

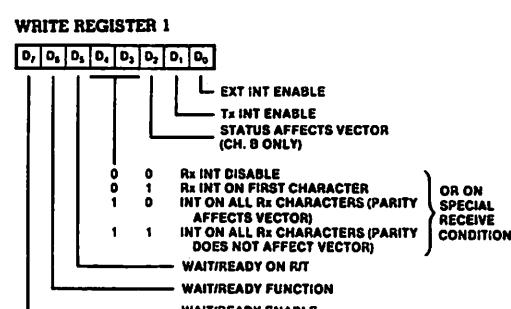

**INTERRUPTS.** The Z-80 DART offers an elaborate interrupt scheme that provides fast interrupt response in real-time applications. As a member of the Z-80 family, the Z-80 DART can be daisy-chained along with other Z-80 peripherals for peripheral interrupt-priority resolution. In addition, the internal interrupts of the Z-80 DART are nested to prioritize the various interrupts generated by Channels A and B. Channel B registers WR2 and RR2 contain the interrupt vector that points to an interrupt service routine in the memory. To eliminate the necessity of writing a status analysis routine, the Z-80 DART can modify the interrupt vector in RR2 so it points directly to one of eight interrupt service routines. This is done under program control by setting a program bit (WR1, D<sub>2</sub>) in Channel B called "Status Affects Vector." When this bit is set, the interrupt vector in RR2 is modified according to the assigned priority of the various interrupting conditions.

Transmit interrupts, Receive interrupts and External/Status interrupts are the main sources of interrupts. Each interrupt source is enabled under program control with Channel A having a higher priority than Channel B, and with Receiver, Transmit and External/Status interrupts prioritized in that order within each channel. When the Transmit interrupt is enabled, the CPU is interrupted by the transmit buffer *becoming* empty. (This implies that the transmitter must have had a data character written into it so it can become

**CPU/DMA BLOCK TRANSFER.** The Z-80 DART provides a Block Transfer mode to accommodate CPU block transfer functions and DMA block transfers (Z-80 DMA or other designs). The Block Transfer mode uses the W/RDY output in conjunction with the Wait/Ready bits of Write Register 1. The W/RDY output can be defined under software control as a Wait line in the CPU Block

status bits D<sub>0</sub> and D<sub>2</sub> indicate that a data transfer is needed. The status also indicates Error or other special status conditions (see "Z-80 DART Programming"). The Special Receive Condition status contained in RR1 does not have to be read in a Polling sequence because the status bits in RR1 are accompanied by a Receive Character Available status in RR0.

empty.) When enabled, the receiver can interrupt the CPU in one of three ways:

- Interrupt on the first received character

- Interrupt on all received characters

- Interrupt on a Special Receive condition

Interrupt On First Character is typically used with the Block Transfer mode. Interrupt On All Receive Characters can optionally modify the interrupt vector in the event of a parity error. The Special Receive Condition interrupt can occur on a character basis. The Special Receive condition can cause an interrupt only if the Interrupt On First Receive Character or Interrupt On All Receive Characters mode is selected. In Interrupt On First Receive Character, an interrupt can occur from Special Receive conditions (except Parity Error) after the first receive character interrupt (example: Receive Overrun interrupt).

The main function of the External/Status interrupt is to monitor the signal transitions of the  $\overline{CTS}$ ,  $\overline{DCD}$  and  $\overline{RI}$  pins; however, an External/Status interrupt is also caused by the detection of a Break sequence in the data stream. The interrupt caused by the Break sequence has a special feature that allows the Z-80 DART to interrupt when the Break sequence is detected or terminated. This feature facilitates the proper termination of the current message, correct initialization of the next message, and the accurate timing of the Break condition.

Transfer mode or as a Ready line in the DMA Block Transfer mode.

To a DMA controller, the Z-80 DART Ready output indicates that the Z-80 DART is ready to transfer data to or from memory. To the CPU, the Wait output indicates that the Z-80 DART is not ready to transfer data, thereby requesting the CPU to extend the I/O cycle.

**Internal Architecture**

The device internal structure includes a Z-80 CPU interface, internal control and interrupt logic, and two full-duplex channels. Each channel contains read and write registers, and discrete control and status logic that provides the interface to modems or other external devices.

The read and write register group includes five 8-bit control registers and two status registers. The interrupt vector is written into an additional 8-bit register (Write Register 2) in Channel B that may be read through Read Register 2 in Channel B. The registers for both channels are designated as follows:

WR0-WR5 — Write Registers 0 through 5

RR0-RR2 — Read Registers 0 through 2

The bit assignment and functional grouping of each register is configured to simplify and

organize the programming process.

The logic for both channels provides formats, bit synchronization and validation for data transferred to and from the channel interface. The modem control inputs Clear to Send (CTS), Data Carrier Detect (DCD) and Ring Indicator (RI) are monitored by the control logic under program control. All the modem control signals are general purpose in nature and can be used for functions other than modem control.

For automatic interrupt vectoring, the interrupt control logic determines which channel and which device within the channel has the highest priority. Priority is fixed with Channel A assigned a higher priority than Channel B; Receive, Transmit and External/Status interrupts are prioritized in that order within each channel.

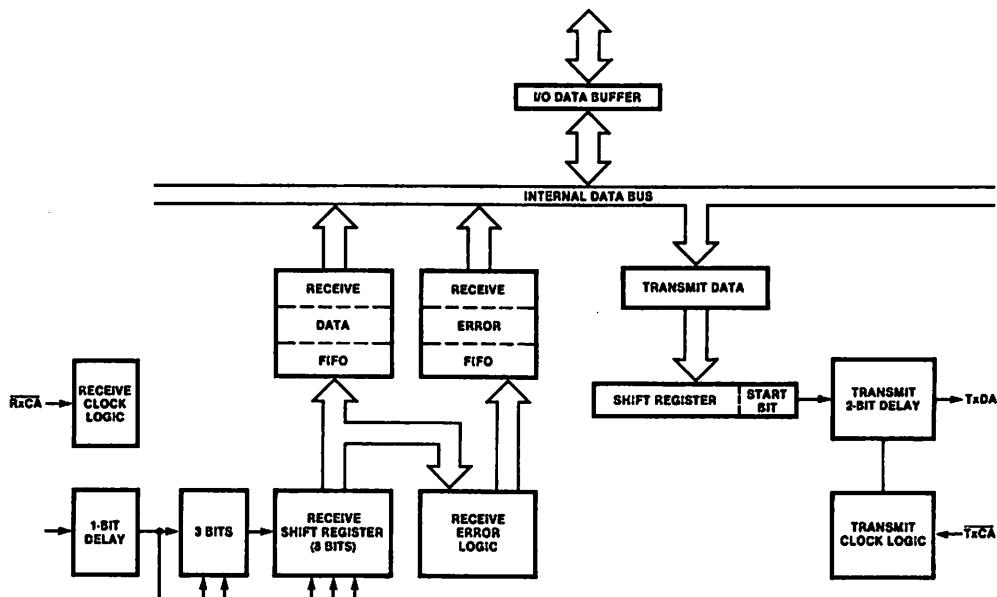

**Data Path.** The transmit and receive data path illustrated for Channel A in Figure 4 is identical for both channels. The receiver has three 8-bit buffer registers in a FIFO arrangement in addition to the 8-bit receive shift register. This scheme creates additional time for the CPU to

service a Receive Character Available interrupt in a high-speed data transfer.

The transmitter has an 8-bit transmit data register that is loaded from the internal data bus, and a 9-bit transmit shift register that is loaded from the transmit data register.

Figure 4. Data Path

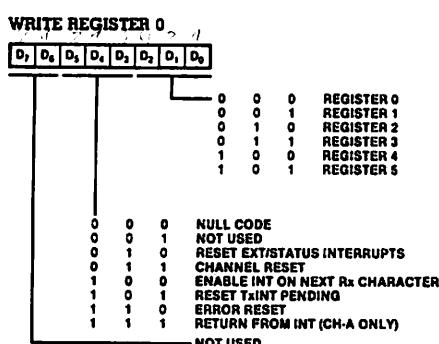

**Z-80 DART Programming** To program the Z-80 DART, the system program first issues a series of commands that initialize the basic mode and then other commands that qualify conditions within the selected mode. For example, the character length, clock rate, number of stop bits, even or odd parity are first set, then the Interrupt mode and, finally, receiver or transmitter enable.

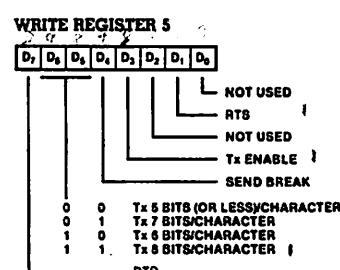

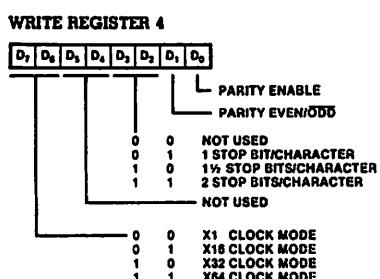

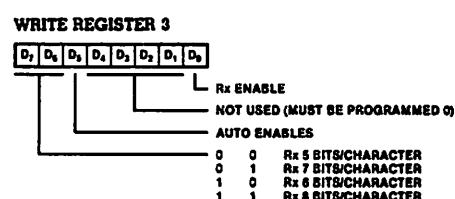

**Write Registers.** The Z-80 DART contains six registers (WR0-WR5) in each channel that are programmed separately by the system program to configure the functional personality of the channels (Figure 4). With the exception of WR0, programming the write registers requires two bytes. The first byte contains three bits ( $D_0-D_2$ ) that point to the selected register; the second byte is the actual control word that is written into the register to configure the Z-80 DART.

WR0 is a special case in that all the basic commands ( $CMD_0-CMD_2$ ) can be accessed with a single byte. Reset (internal or external) initializes the pointer bits  $D_0-D_2$  to point to WR0. This means that a register cannot be

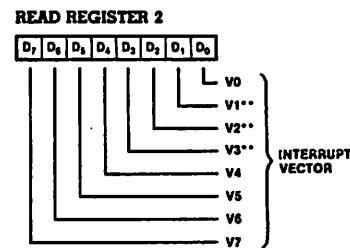

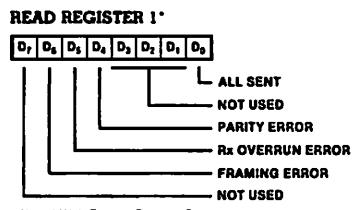

**Read Registers.** The Z-80 DART contains three registers (RR0-RR2) that can be read to obtain the status information for each channel (except for RR2, which applies to Channel B only). The status information includes error conditions, interrupt vector and standard communications-interface signals.

To read the contents of a selected read register other than RR0, the system program must first write the pointer byte to WR0 in exactly the same way as a write register operation. Then, by executing an input instruction, the contents of the addressed read register can be read by the CPU.

Both channels contain command registers that must be programmed via the system program prior to operation. The Channel Select input ( $B/A$ ) and the Control/Data input ( $C/D$ ) are the command structure addressing controls, and are normally controlled by the CPU address bus.

pointed to in the same operation as a channel reset.

#### Write Register Functions

- |     |                                                                        |

|-----|------------------------------------------------------------------------|

| WR0 | Register pointers, initialization commands for the various modes, etc. |

| WR1 | Transmit/Receive interrupt and data transfer mode definition.          |

| WR2 | Interrupt vector (Channel B only)                                      |

| WR3 | Receive parameters and control                                         |

| WR4 | Transmit/Receive miscellaneous parameters and modes                    |

| WR5 | Transmit parameters and controls                                       |

The status bits of RR0 and RR1 are carefully grouped to simplify status monitoring. For example, when the interrupt vector indicates that a Special Receive Condition interrupt has occurred, all the appropriate error bits can be read from a single register (RR1).

#### Read Register Functions

- |     |                                                                      |

|-----|----------------------------------------------------------------------|

| RR0 | Transmit/Receive buffer status, interrupt status and external status |

| RR1 | Special Receive Condition status                                     |

| RR2 | Modified interrupt vector (Channel B only)                           |

**Z-80 DART**

**Read and Write**

**Registers**

| SIGNAL NAME        | DESCRIPTION                                                                                                                                                                                                                                                                          |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $V_{SS}$           | Ground                                                                                                                                                                                                                                                                               |

| $V_{CC}$           | +5 volts ( $\pm 5$ percent)                                                                                                                                                                                                                                                          |

| $\overline{CE}$    | Chip Enable (Input, active low)                                                                                                                                                                                                                                                      |

| $\overline{RD}$    | Read Enable (Input, active low)                                                                                                                                                                                                                                                      |

| $\overline{WR}$    | Write Enable (Input, active low)                                                                                                                                                                                                                                                     |

| $A_0-A_3$          | Address Inputs. Used to address one of the internal registers during a read or write operation                                                                                                                                                                                       |

| $D_0-D_7$          | Data Bus (bi-directional)                                                                                                                                                                                                                                                            |

| $\overline{RESET}$ | Device Reset (negative true). When activated, all internal registers (except for Timer or USART Data registers) will be cleared, all timers stopped, USART turned off, all interrupts disabled and all pending interrupts cleared, and all I/O lines placed in tri-state input mode. |

| $I_0-I_7$          | General purpose I/O and interrupt lines                                                                                                                                                                                                                                              |

| $\overline{INT}$   | Interrupt Request (Output, active low, open drain)                                                                                                                                                                                                                                   |

| $\overline{IORQ}$  | Input/Output Request from Z80-CPU (input, active low). The $\overline{IORQ}$ signal is used in conjunction with $M1$ to signal the MK3801 that the CPU is acknowledging its interrupt.                                                                                               |

| $IEI$              | Interrupt Enable In, active High                                                                                                                                                                                                                                                     |

| $IEO$              | Interrupt Enable Out, active High                                                                                                                                                                                                                                                    |

| $SO$               | Serial Output                                                                                                                                                                                                                                                                        |

| $SI$               | Serial Input                                                                                                                                                                                                                                                                         |

| $RC$               | Receiver Clock Input                                                                                                                                                                                                                                                                 |

| $TC$               | Transmit Clock Input                                                                                                                                                                                                                                                                 |

| $TAO-TDO$          | Timer Outputs                                                                                                                                                                                                                                                                        |

| $TCLK$             | Timer Clock Input                                                                                                                                                                                                                                                                    |

| $M1$               | Z80 Machine Cycle One (negative true)                                                                                                                                                                                                                                                |

#### PIN DESCRIPTION

Figure 1 illustrates the pinout of the MK3801. The functions of these individual pins are described above.

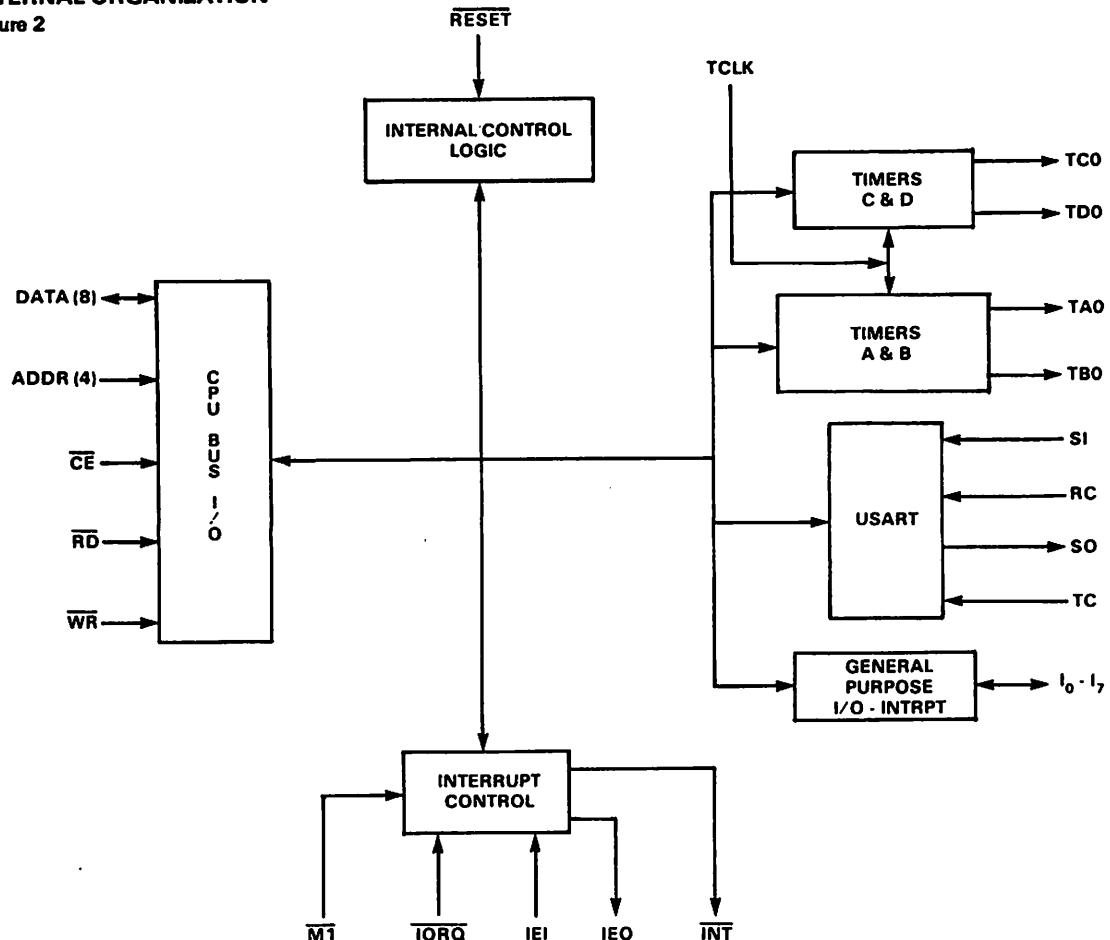

#### INTERNAL ORGANIZATION

Figure 2 illustrates the MK3801 internal organization, which supports the full set of timing, communications, parallel I/O, and interrupt processing functions available in the device.

#### CPU BUS I/O

The CPU BUS I/O provides the means of communications between the system and the MK3801. Data, Status, and Control Registers in the MK3801 are accessed by the bus in order to establish device parameters, assert control, and transfer status and data between the system and the MK3801.

Each register in the MK3801 is addressed over the address bus in conjunction with Chip Enable ( $\overline{CE}$ ), while data is transferred over the eight bit Data bus under control of Read ( $\overline{RD}$ ) and Write ( $\overline{WR}$ ) signals.

#### REGISTER ACCESSES

All register accesses are independent of any system clock. To read a register, both  $\overline{CE}$  and  $\overline{RD}$  must be active. The internal read control signal is essentially the combination of

both  $\overline{CE}$  and  $\overline{RD}$  active; thus the read operation will begin when the later of these two signals goes active and will end when the first signal goes inactive. The address bus must be stable prior to the start of the operation and must remain stable until the end of the operation. Unless a read operation or an interrupt acknowledge cycle is in progress, the data bus ( $D_0-D_7$ ) will remain in the tri-state condition.

To write a register, both  $\overline{CE}$  and  $\overline{WR}$  must be active. The address must be stable prior to the start of the operation and must remain stable until the end of the operation. The data must be stable prior to the end of the operation and must remain stable until the end of the operation. The data presented on the bus will be latched into the register shortly after either  $\overline{WR}$  or  $\overline{CE}$  goes inactive.

#### INTERNAL REGISTERS

There are 24 internal registers used to control the operation of the STI. Sixteen of these registers are directly addressable and accessible. Eight registers are indirectly addressable via the Pointer/Vector Register and accessible via the Indirect Data Register.

#### DIRECTLY ADDRESSABLE REGISTERS

The Directly Addressable Registers are accessed by placing the address of the desired register on the address lines ( $A_0-A_3$ ) during a write or read cycle. Figure 3 lists the Directly Addressable Registers.

## INTERNAL ORGANIZATION

Figure 2

## DIRECTLY ACCESSIBLE REGISTERS

Figure 3

| ADDRESS | ABBREVIATION | REGISTER NAME                   |

|---------|--------------|---------------------------------|

| 0       | IDR          | Indirect Data Register          |

| 1       | GPIP         | General Purpose I/O-Interrupt   |

| 2       | IPRB         | Interrupt Pending Register B    |

| 3       | IPRA         | Interrupt Pending Register A    |

| 4       | ISRB         | Interrupt in-Service Register B |

| 5       | ISRA         | Interrupt in-Service Register A |

| 6       | IMRB         | Interrupt Mask Register B       |

| 7       | IMRA         | Interrupt Mask Register A       |

| 8       | PVR          | Pointer/Vector Register         |

| 9       | TABCR        | Timers A and B Control Register |

**DIRECTLY ACCESSIBLE REGISTERS (Continued)**

**Figure 3**

| ADDRESS | ABBREVIATION | REGISTER NAME               |

|---------|--------------|-----------------------------|

| A       | TBDR         | Timer B Data Register       |

| B       | TADR         | Timer A Data Register       |

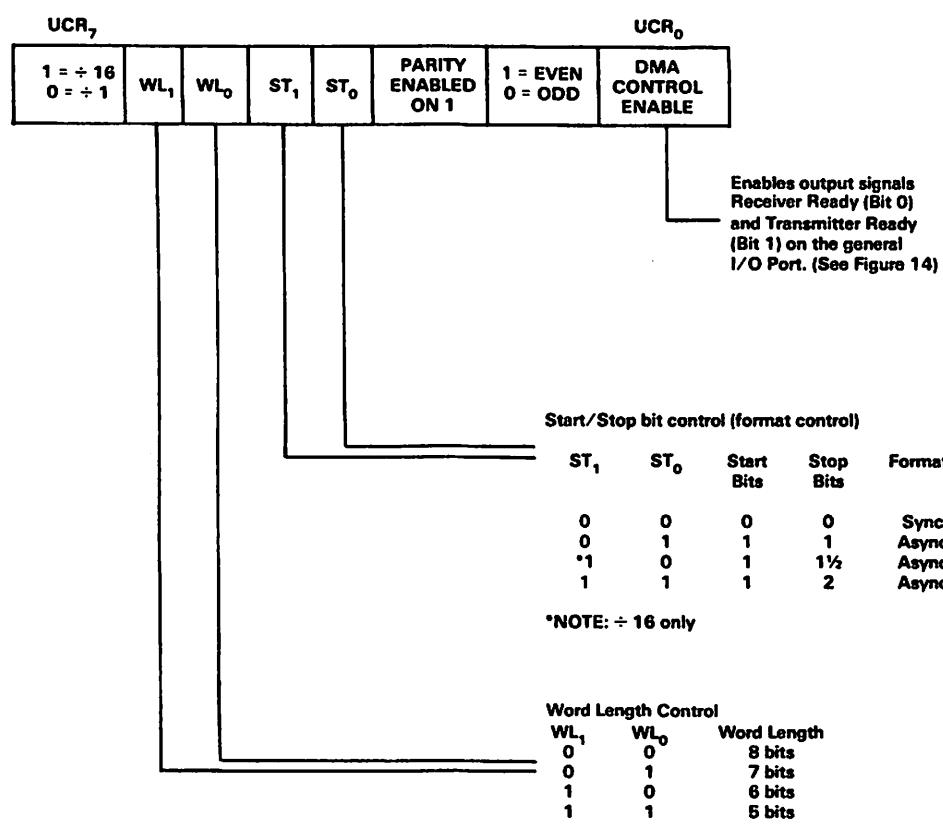

| C       | UCR          | USART Control Register      |

| D       | RSR          | Receiver Status Register    |

| E       | TSR          | Transmitter Status Register |

| F       | UDR          | USART Data Register         |

**INDIRECTLY ADDRESSABLE REGISTERS**

Figure 4

| INDIRECT ADDRESS | ABBREVIATION | REGISTER NAME                   |

|------------------|--------------|---------------------------------|

| 0                | SCR          | Sync Character Register         |

| 1                | TDDR         | Timer D Data Register           |

| 2                | TCDR         | Timer C Data Register           |

| 3                | AER          | Active Edge Register            |

| 4                | IERB         | Interrupt Enable Register B     |

| 5                | IERA         | Interrupt Enable Register A     |

| 6                | DDR          | Data Direction Register         |

| 7                | TCDCR        | Timers C and D Control Register |

**INDIRECTLY ADDRESSABLE REGISTERS**

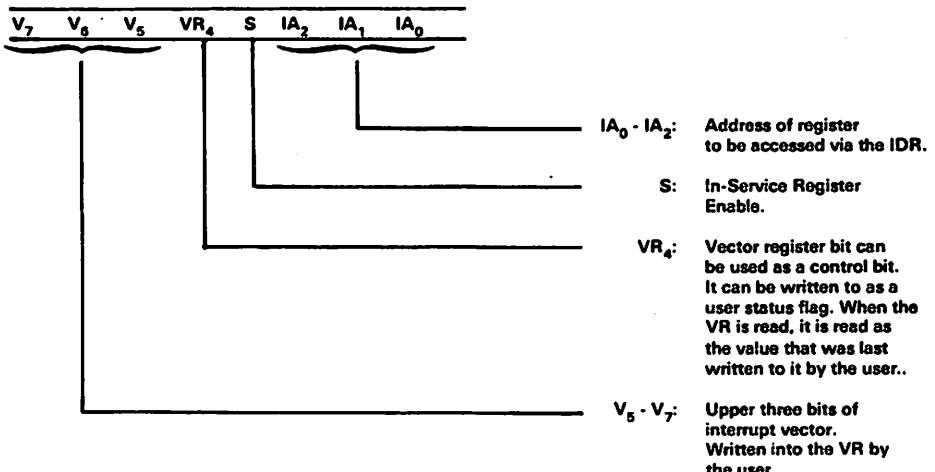

Indirectly Addressable Registers are addressed by placing the indirect address in bits IA0-IA2 of the Pointer/Vector Register, as defined in Figure 5. Data may be written to or read from the register indicated by these Indirect Register Address bits by a write or read access of the Indirect Data Register (selected when A<sub>0</sub>-A<sub>3</sub> are all zero). The indirect address bits of the Pointer/Vector Register will remain unchanged after an indirect access. Repeated accesses of the Indirect Data Register will access the same indirect register as long as the indirect address in the Pointer/Vector Register remains unchanged. The Indirectly Addressable Registers are listed in Figure 4.

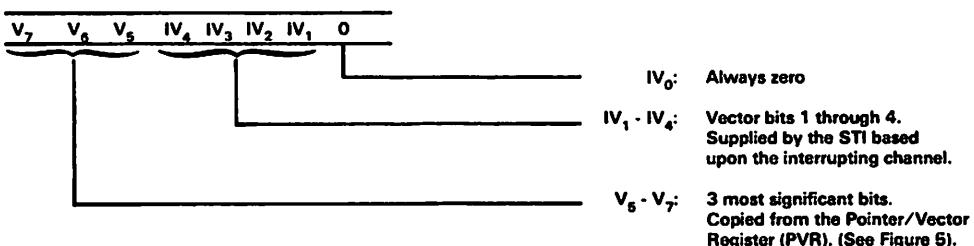

**INTERRUPT VECTOR DEFINITION**

Each individual function in the MK3801 is provided with a unique interrupt vector that is presented to the system during the interrupt acknowledge cycle. The interrupt vector returned during interrupt acknowledge is formed as shown in Figure 6. There are 16 vector addresses generated internally by the MK3801, one for each of the 16 interrupt channels. The three most significant bits of these vector addresses correspond to the three most significant bits of the Pointer/Vector Register shown in Figure 5. The least significant bit of each vector address is always 0, thus producing even vector addresses. The remaining 4 bits (IV<sub>1</sub> through IV<sub>4</sub>) identify each of the 16 interrupt channels individually. The lowest priority channel responds with 0000 for IV<sub>4</sub>-IV<sub>1</sub>, respectively. The next higher priority channel responds with 0001, and so on in binary order, with the highest priority channel responding with 1111. Figure 7 lists each of the 16 interrupt channels in order of descending priority.

through IV<sub>4</sub>) identify each of the 16 interrupt channels individually. The lowest priority channel responds with 0000 for IV<sub>4</sub>-IV<sub>1</sub>, respectively. The next higher priority channel responds with 0001, and so on in binary order, with the highest priority channel responding with 1111. Figure 7 lists each of the 16 interrupt channels in order of descending priority.

**INTERRUPT CONTROL REGISTERS**

The Interrupt Control Registers provide control of interrupt processing for all I/O facilities of the MK3801. These registers allow the programmer to enable or disable any or all of the 16 interrupts, provide masking for any interrupts, and access to the pending or in-service status of the interrupts. Optional End-of-Interrupt modes are available under software control. The format of each of the Interrupt Control Registers is presented in Figure 8.

**INTERRUPT OPERATION**

The Interrupt Enable Registers enable or disable the setting of an interrupt in the Interrupt Pending Registers. A 0 in a bit of the Interrupt Enable Registers disables the interrupt for the associated channel while a 1 enables the interrupt.

Once an interrupt is enabled, the occurrence of an interrupting condition on that channel will cause the

**POINTER/VECTOR REGISTER (PVR) Port 08**

Figure 5

**INTERRUPT VECTOR**

Figure 6

corresponding bit in the Interrupt Pending Register to be set. This indicates that an interrupt is pending in the MK3801.

Pending interrupts are presented to the Z80 CPU in order of priority (see Figure 1) unless they have been masked off. This is done by clearing the bit in the Interrupt Mask Register corresponding to the channel whose interrupt is to be masked. The channel's interrupt will remain pending until the mask bit for that channel is set, at which time the interrupt for that channel will be processed in order of priority.

When an interrupt vector is generated for a pending interrupt and passed to the Z80 CPU, the bit in the Interrupt Pending Register, associated with the channel generating the interrupt, will be cleared. At this time, no history of the

interrupt remains in the MK3801.

In order to retain historical evidence of an interrupt being serviced by the Z80, the In-Service Register may be enabled by setting the S-bit in the Pointer/Vector Register (see Figure 5). If the In-Service Register is enabled, the bit of the In-Service Register corresponding to the interrupting channel will be set when the interrupt vector is passed to the Z80. At the same time, the Interrupt Pending bit will be cleared since the interrupt is now in service. The In-Service bit will be cleared on execution of a Return-from-Interrupt (H'ED4D') instruction. The In-Service Registers are directly addressable, and the In-Service bit for any interrupt may be cleared by writing to the In-Service Register if the Return-from-Interrupt instruction is not used.

**INTERRUPT CONTROL REGISTER DEFINITIONS**

Figure 7