MFA-MEDIENSYSTEM

# Mikrocomputer- Technik

Fachpraktische Übungen

Band 5

5

# - Ihr Partner für Ausbildungssysteme

## Neue Produkte im Bereich Mediensysteme

Mit Medien, Aus- und Weiterbildung begann sich die vgs bereits vor 20 Jahren mit dem Begleitbuch zur Fernsehreihe „Einführung in die Elektronik“ von Jean Pütz zu beschäftigen. Über die Jahre hinweg entstanden in Zusammenarbeit mit ARD und ZDF weitere Bücher und Bausätze aus den Bereichen Elektronik, Chemie und Biotechnologie. Inzwischen ist die vgs der Spezialist für Medienverbund auf allen Gebieten. Die Zusammenarbeit mit dem Berufsförderungszentrum Essen e.V. begann 1983, als die vgs den Zuschlag für die Produktion und Verbreitung des dort entwickelten Mikrocomputer-Ausbildungssystems MFA erhielt. Inzwischen umfaßt das Programm der vgs für den Bereich der Aus- und Weiterbildung folgende Produkte:

- **MFA** – ein Mikrocomputer-Ausbildungssystem, das in den industriellen Metall- und Elektro-Berufen sowie in den handwerklichen Elektro-Berufen im In- und Ausland eine zentrale Rolle spielt. Das vom BFZ in Essen entwickelte Grundsystem wird von der vgs ständig zukunftsorientiert weiterentwickelt, produziert und vertrieben, so daß inzwischen ca. 90 Baugruppen zur Verfügung stehen.

- **40 900 NORMCOMPUTER** – ein Computer-Lehrsystem für die Schulung im Bereich Digitaltechnik, bei dem Wert auf die Einhaltung der gültigen internationalen Digitalnorm nach DIN 40 900 gelegt wurde (in Zusammenarbeit mit dem BBZ Köln). Mit diesem, aus 8 Lehrplatten bestehendem Lehrsystem, kann die immer noch bestehende Lücke zwischen Digitaltechnik und Mikrocomputertechnik geschlossen werden. Basis des NORMCOMPUTERS ist der in der Aus- und Weiterbildung nach wie vor optimal einzusetzende Mikrocomputer 8085.

- **PC-Modelle** für die Schulung – hier bietet die vgs Anwendungsmodelle aus den Bereichen Logikanalyse, Meßtechnik und Robotik an.

- **PTQ** (steht für Produktionstechnische Qualifikation im Lernverbund). An dieser neuen Entwicklung vom BFZ Essen ist die vgs als Werkvertragsnehmer über die Konstruktion und Dokumentation sowie Fertigungsarbeiten für „Portallader-Komponenten“ beteiligt.

Die vgs liefert in das Inland (inzwischen mit Schwerpunkt neue Bundesländer) und über Vertragspartner in das Ausland an Industrie, Handwerk, Ausbildungszentren und Schulen.

Bitte fordern Sie weitere Informationen an bei:

vgs verlagsgesellschaft mbH & Co. KG

Postfach 180269

Breite Straße 118-120, 5000 Köln 1

Telefon 02 21/2 0811-12

Telefax 02 21/24 5799

Telex 888 2202 vgs d

---

MFA-MEDIENSYSTEM

---

# Mikrocomputer- Technik

---

Fachpraktische Übungen · Band 5

---

Die Deutsche Bibliothek – CIP-Einheitsaufnahme

**MFA-Mediensystem Mikrocomputer-Technik** / [Red.: F. Derriks ...]. – Köln : vgs.

Teilw. redigiert von N. Meyer ... Teilw. hrsg. vom BFZ Essen

NE: Meyer, Norbert [Red.]; Derriks, Franz [Red.];

Berufsförderungszentrum <Essen>; Mikrocomputer-Technik

Fachpraktische Übungen.

Bd. 5. – 1. Aufl. – 1992

ISBN 3-8025-1259-6

Herausgeber: vgs verlagsgesellschaft mbH & Co. KG

Breite Str. 118-120,

5000 Köln 1

Redaktion: F. Derriks, M. Hüllweg, R. Lüdecke,

E. Matz, Fr.G. Roßmanek, K.D. Strelow,

H. Storbeck, S. Wirtgen, W. Hild,

W. Oehlert, D. Piller

C 1991 vgs verlagsgesellschaft mbH & Co. KG

Berufsförderungszentrum Essen e.V.

Diese Publikation ist urheberrechtlich

geschützt. Alle Rechte sind vorbehalten.

Verlag: vgs verlagsgesellschaft, Köln

1. Auflage 1991

Satz und Zeichnungen: BFZ Essen; Teba-Elektronik, Nenderoth

## Hinweise zu den Übungen in diesem Band

Die in diesem Band enthaltenen Übungen sind nicht durchgehend, sondern einzeln paginiert, und zwar oben rechts auf jeder Seite. Dabei ist jeweils auch die Systemnummer der betreffenden Übung angegeben (z.B. 64-K-RAM-Baugruppe BFZ/MFA 3.3). Hierdurch ist es möglich, den Band auseinanderzunehmen und die Übungen einzusetzen.

Dieser Band enthält folgende Übungen:

- 64-K-RAM-Baugruppe BFZ/MFA 3.3

- Galvan. getrennte 8-Bit-Eingabe BFZ/MFA 4.8

- Galvan. getrennte 8-Bit-Ausgabe BFZ/MFA 4.9

- V.24/RS232-Schnittstelle BFZ/MFA 4.10

- AD/DA-Wandler (mit Hardwarewandlern) BFZ/MFA 4.13

- Vektor-Interrupt-Karte (erfordert 62.FG) BFZ/MFA 4.15

# FACHPRAKTISCHE ÜBUNG

# MIKROCOMPUTER-TECHNIK

64-KByte-RAM

BFZ/MFA 3.3.

---

Inhaltsverzeichnis

---

| Inhalt                                  | Seite |

|-----------------------------------------|-------|

| Hinweise                                | 1     |

| Blockschaltbild                         | 2     |

| Funktionsbeschreibung                   | 3     |

| Stromlaufplan                           | 7     |

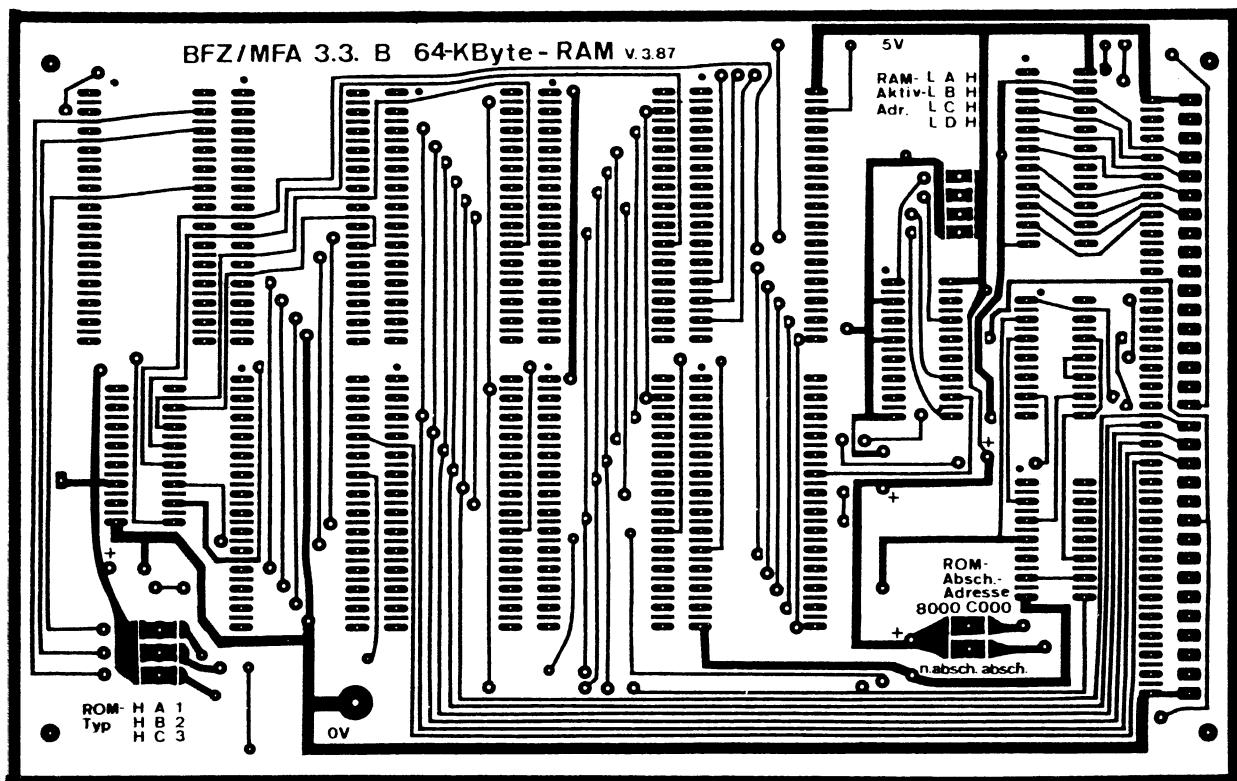

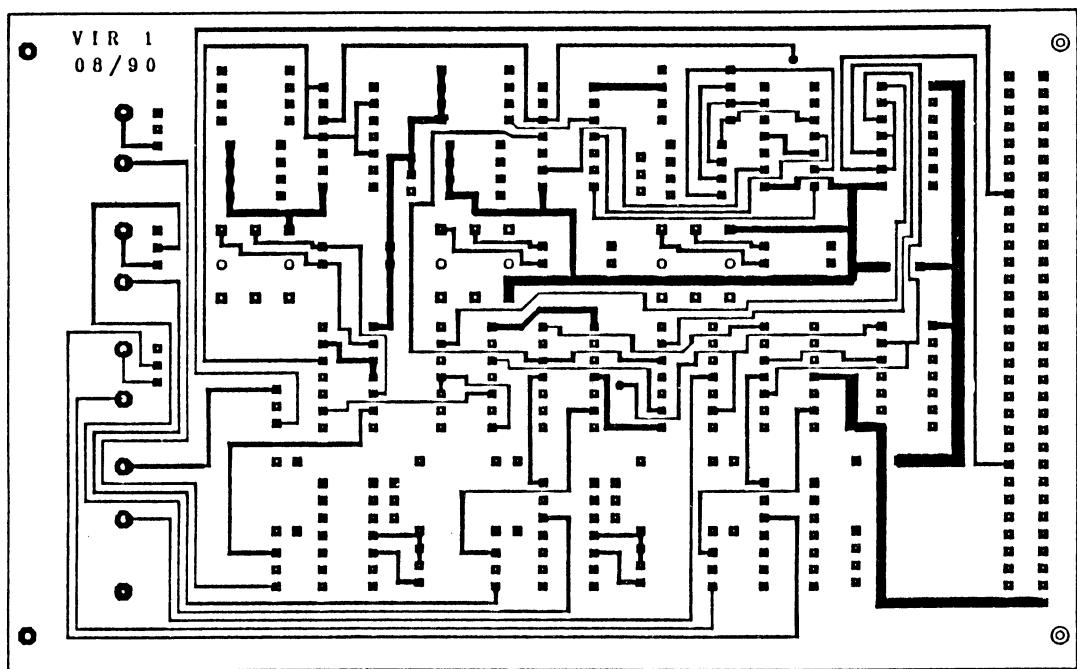

| Bestückung Leiterplatte                 | 8     |

| Bereitstellungsliste zur Inbetriebnahme | 10    |

| Inbetriebnahme                          | 11    |

| Bereitstellungsliste                    | 16    |

| Bohrplan Leiterplatte                   | 18    |

| Layout Bestückungsseite                 | 19    |

| Beschriftung Frontplatte                | 20    |

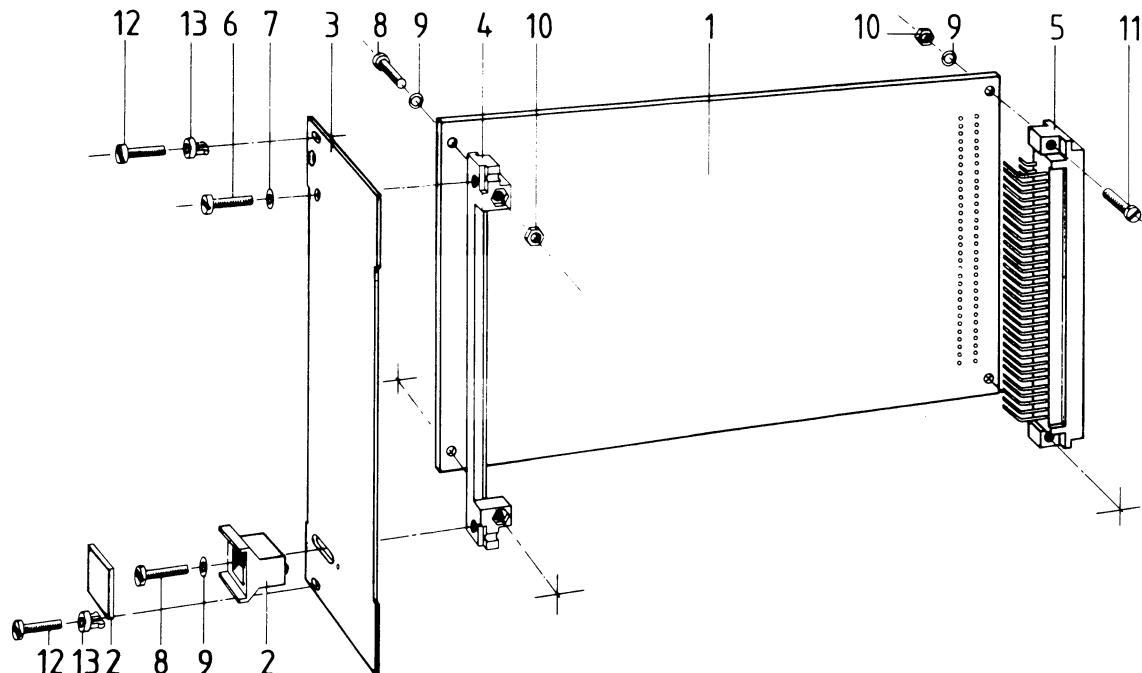

| Zusammenbau Baugruppe                   | 21    |

**Hinweise**

Die 64-KByte-RAM-Baugruppe ist für den Betrieb des BFZ/MFA-Mikrocomputers unter dem Betriebssystem "CP/M" vorgesehen. Die Baugruppe enthält acht 8-KByte-RAM-Bausteine und ein EPROM mit wahlweise 2-, 4-, 8-, 16- oder 32-KByte-Speicherkapazität.

Unter "CP/M" wird das EPROM nach dem Laden des Betriebssystems abgeschaltet, so daß anschließend der ganze 64-KByte-RAM-Bereich zur Verfügung steht. Für andere Anwendungen ist es möglich, RAM und EPROM gemeinsam zu benutzen, wobei der nutzbare RAM-Bereich um die Kapazität des EPROMs verringert wird.

Einzelheiten zum Betrieb des BFZ/MFA-Mikrocomputers in Verbindung mit dem Betriebssystem "CP/M" sind in der Übung "CP/M-Ausbaustufe des BFZ/MFA-Mikrocomputers" BFZ/MFA 7.3. beschrieben.

## Blockschaltbild

---

## Funktionsbeschreibung

---

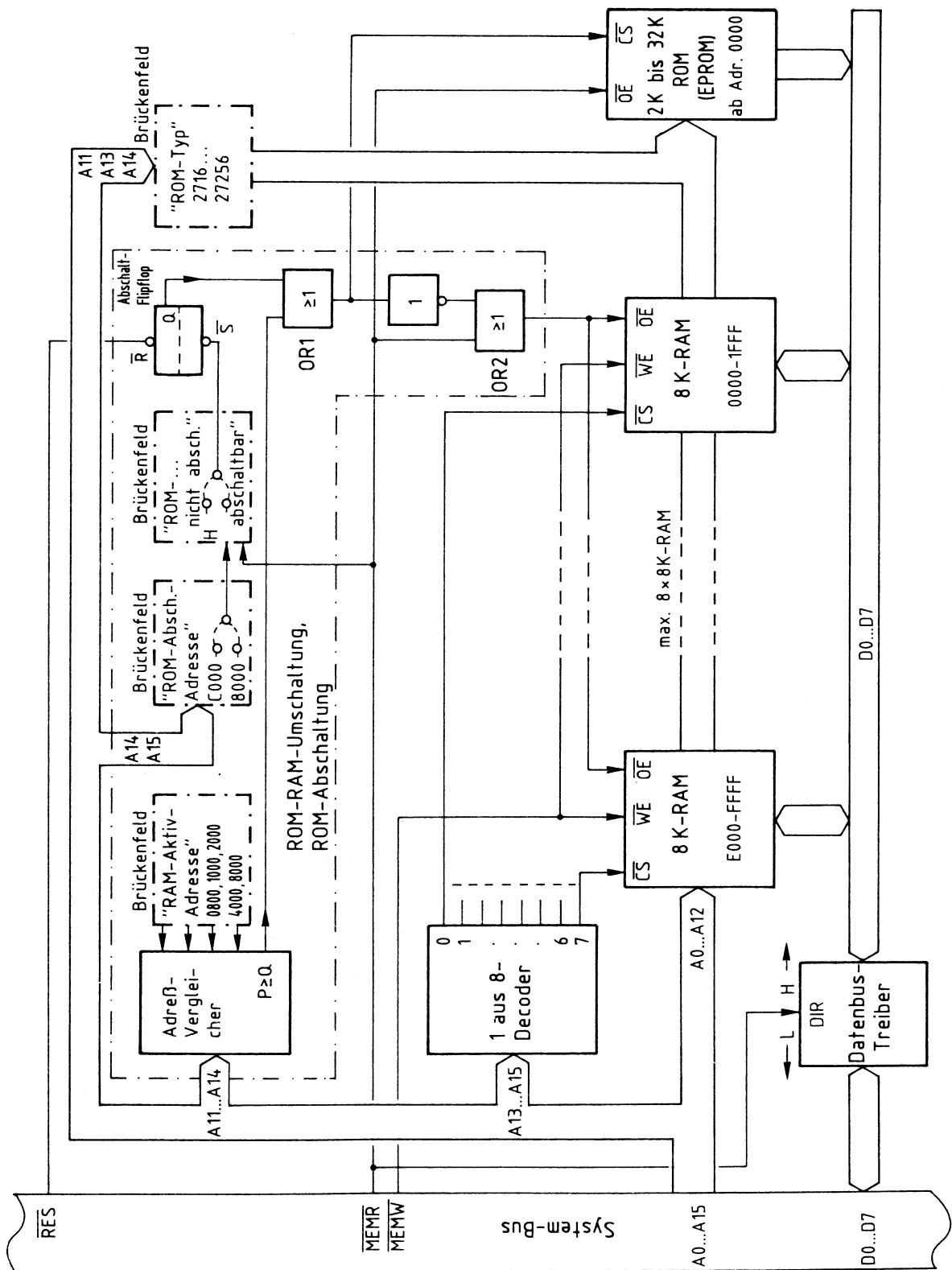

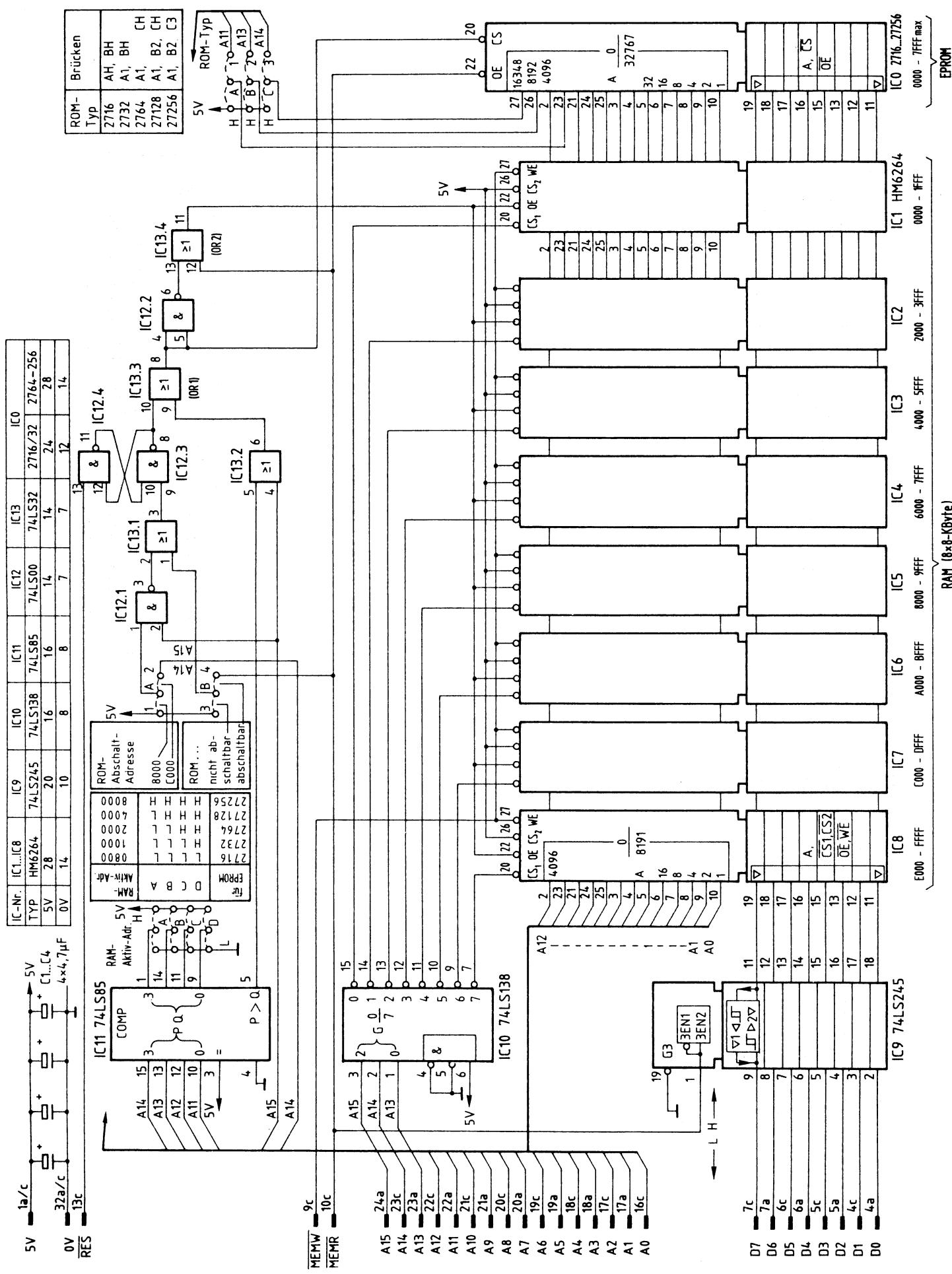

Die Funktionsbeschreibung bezieht sich auf das Blockschaltbild der Baugruppe. Schaltungseinzelheiten sind dem Stromlaufplan zu entnehmen.

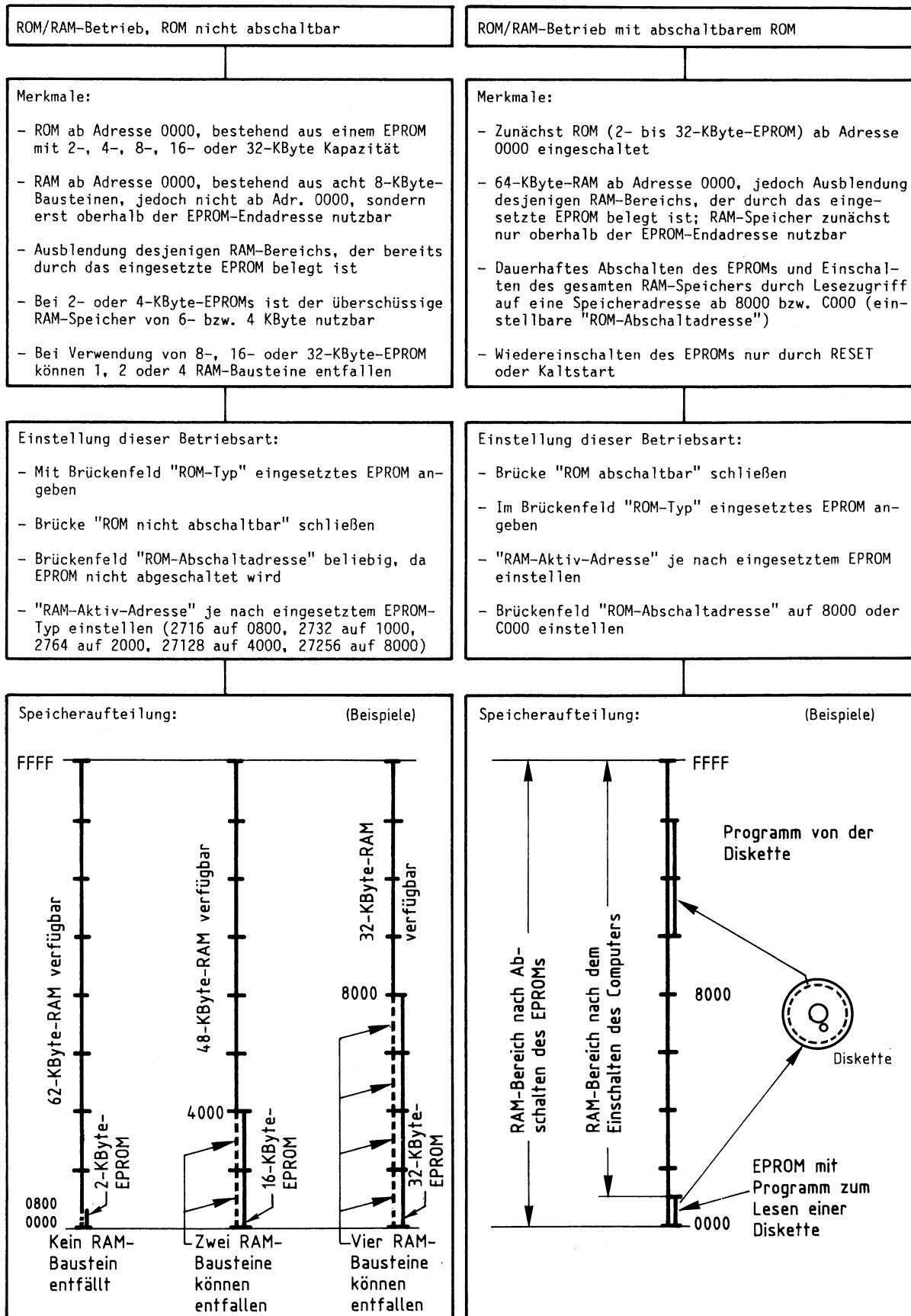

Die 64-KByte-RAM-Baugruppe kann wahlweise in der Betriebsart "ROM/RAM-Betrieb, ROM nicht abschaltbar" oder "ROM/RAM-Betrieb mit abschaltbarem ROM" eingesetzt werden. Die Einrichtung der Baugruppe für die gewünschte Betriebsart erfolgt durch Lötbrücken auf mehreren Brückenfeldern. Alle hierzu erforderlichen Angaben (technische Merkmale, typische Speicheraufteilungen) befinden sich am Ende der Funktionsbeschreibung.

### Datenbus-Treiber, 1 aus 8-Decoder und Speicher

Der Daten-Bus der Baugruppe ist über einen Datenbus-Treiber mit dem System-Bus verbunden. Die Arbeitsrichtung des Datenbus-Treibers wird mit dem Signal MEMR gesteuert.

Mit den Adreßleitungen A0 bis A12 werden die einzelnen Speicherzeilen der RAM-Bausteine und des EPROMs adressiert. Je nach verwendetem EPROM (2716...27256) werden die Adreßleitungen A11, A13 und A14 im Brückenfeld "ROM-Typ" an die unterschiedlichen Anschlußbelegungen der EPROMs angepaßt.

Die Adreßleitungen A13 bis A15 führen auf einen 1 aus 8-Decoder, der jeweils einen der 8-KByte-RAM-Bausteine über dessen CS-Anschluß freigibt.

Die OE-Anschlüsse aller RAM-Bausteine sind zusammengeführt. Daten des RAM-Speichers können nur dann gelesen werden, wenn die OE-Anschlüsse L-Pegel erhalten. Die Schreib-Lese-Umschaltung der RAM-Bausteine erfolgt über MEMW.

### ROM-RAM-Umschaltung

Zur ROM-RAM-Umschaltung gehören der Adreßvergleicher mit dem Brückenfeld "RAM-Aktiv-Adresse", die ODER-Verknüpfung "OR1", der Inverter und die ODER-Verknüpfung "OR2".

Beim Einschalten des Mikrocomputers (oder bei Betätigung der RESET-Taste) wird das Abschalt-Flipflop über das Signal RES zurückgesetzt, so daß der Ausgang Q an die ODER-Verknüpfung OR1 L-Pegel abgibt.

---

## Funktionsbeschreibung

---

Der zweite Eingang von OR1 erhält nach dem Einschalten vom Ausgang  $P \geq Q$  des Adreßvergleichers ebenfalls L-Pegel, da die vom Prozessor ausgegebene Adresse 0000 stets kleiner als die mit dem Brückenfeld "RAM-Aktiv-Adresse" einstellbare Vergleichsadresse ist. Die ODER-Verknüpfung OR1 gibt daher zunächst L-Pegel ab. Hiermit wird der  $\overline{CS}$ -Anschluß des EPROMs angesteuert und das EPROM aktiviert.

Bei aktivem EPROM muß der RAM-Speicher abgeschaltet sein. Die RAM-Abschaltung erfolgt durch H-Pegel an den  $\overline{OE}$ -Anschlüssen der RAM-Bausteine. Dieser H-Pegel stammt von der ODER-Verknüpfung OR2 und wird durch Invertierung des Ausgangssignals von OR1 ( $\overline{CS}$ -Signal für das EPROM) gebildet.

Durch das beschriebene Verfahren wird nach dem Einschalten bzw. RESET stets zunächst das EPROM aktiviert und der RAM-Speicher abgeschaltet.

Mit dem Brückenfeld "RAM-Aktiv-Adresse" wird eingestellt, ab welcher Speicheradresse statt des EPROMs der RAM-Speicher aktiv sein soll. Einstellbar sind die Adreßwerte 0800, 1000, 2000, 4000 und 8000. Der einzustellende Wert richtet sich nach dem EPROM-Typ.

Sobald der Prozessor eine Adresse ausgibt, die gleich oder größer der eingestellten RAM-Aktiv-Adresse ist, führt der Adreßvergleicher am Ausgang  $P \geq Q$  H-Pegel und schaltet über OR1 das EPROM ab.

Zum Lesen von Daten aus dem Speicher steuert der Prozessor die  $\overline{MEMR}$ -Leitung auf L-Pegel. Da das EPROM z.Zt. nicht aktiviert ist, führen jetzt beide Eingänge von OR2 L-Pegel, wodurch die  $\overline{OE}$ -Anschlüsse der RAM-Bausteine L-Pegel erhalten und der RAM-Speicher zum Lesen von Daten freigegeben ist.

Zum Einschreiben von Daten in den RAM-Speicher ist L-Pegel an den  $\overline{OE}$ -Anschlüssen nicht erforderlich.

Arbeitet der Prozessor wieder unterhalb der RAM-Aktiv-Adresse, nimmt der Ausgang  $P \geq Q$  des Adreßvergleichers wieder L-Pegel an. Hierdurch wird wieder vom RAM auf das EPROM umgeschaltet. Das Abschalt-Flipflop ist an dieser Umschaltung nicht beteiligt.

## Funktionsbeschreibung

---

### ROM-Abschaltung

Beim Einschalten des Mikrocomputers ist zunächst immer das EPROM aktiviert. Für bestimmte Anwendungsfälle der Speicherbaugruppe wie z.B. das Arbeiten unter dem Betriebssystem "CP/M" muß der Speicher bereits ab der Adresse 0000 mit RAM beginnen. Da "CP/M" nicht in EPROMs gespeichert wird, sondern auf einer Diskette, muß das EPROM ein Programm enthalten, mit dessen Hilfe "CP/M" von der Diskette in den RAM-Speicher geladen wird. Nach diesem als "BOOTEN" bezeichneten Ladevorgang wird das EPROM nicht mehr benötigt und muß abgeschaltet werden.

Die Abschaltung des EPROMs erfolgt durch das Abschalt-Flipflop in Verbindung mit den Brückenfeldern "ROM nicht abschaltbar/abschaltbar" und "ROM-Abschalt-Adresse".

Bedingungen für das Abschalten des EPROMs:

- Brückenfeld "ROM nicht abschaltbar/abschaltbar" in Stellung "abschaltbar"

- Speicher-Lesezugriff des Prozessors auf die mit dem Brückenfeld "ROM-Abschalt-Adresse" eingestellte oder eine höhere Adresse

Nur wenn beide Bedingungen gemeinsam erfüllt sind, wird das Abschalt-Flipflop gesetzt und hierdurch das EPROM dauerhaft abgeschaltet. Anschließend kann auf das EPROM nicht mehr zugegriffen werden. Dieser Zustand bleibt bis zum nächsten RESET erhalten.

### Zusammenfassung

Auf der nächsten Seite sind die Betriebsarten der 64-KByte-RAM-Baugruppe zusammengefaßt dargestellt und Beispiele für einige mögliche Speicheraufteilungen angegeben.

## Funktionsbeschreibung

## Stromlaufplan

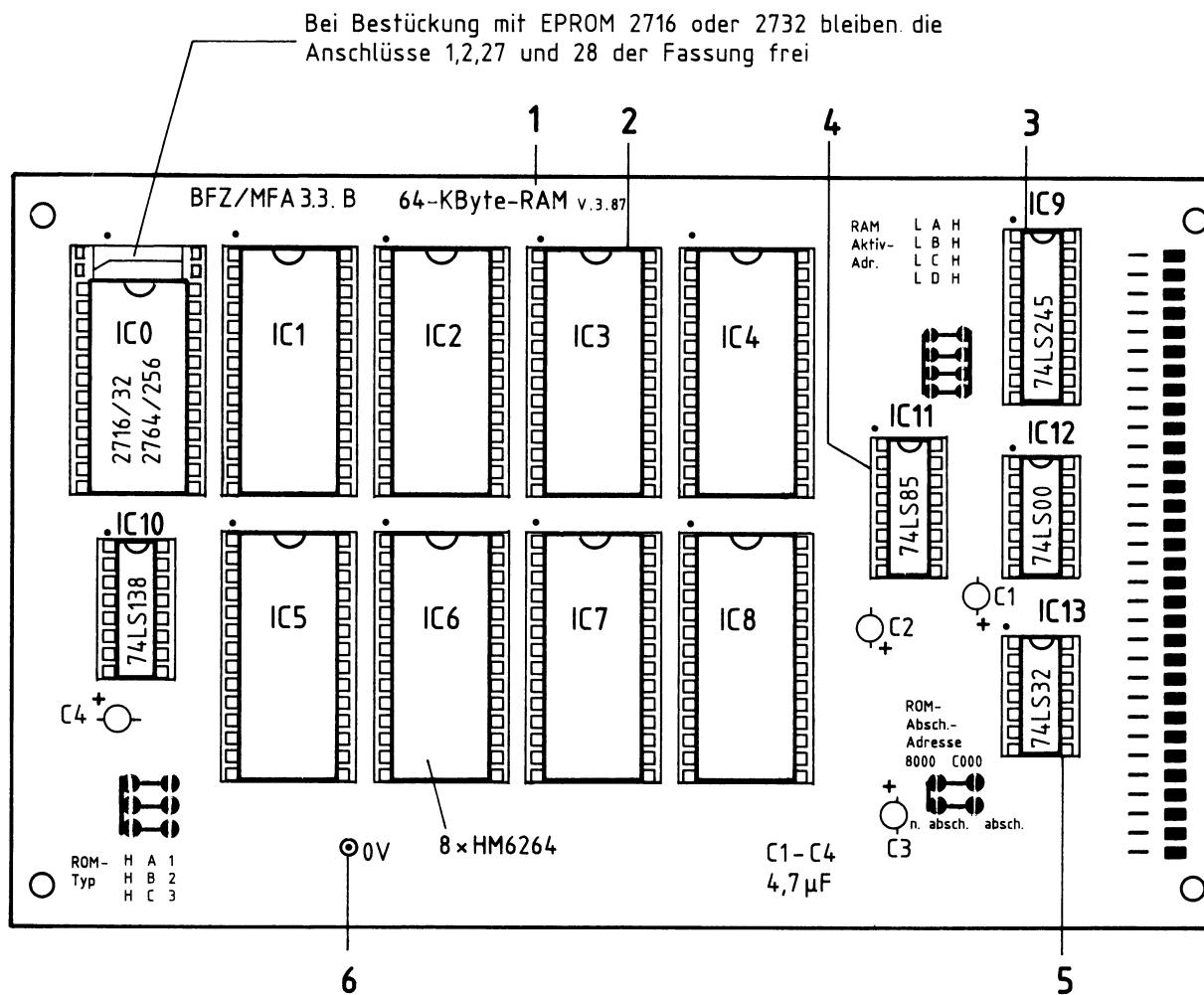

## Bestückung Leiterplatte

## Stückliste Leiterplatte BFZ/MFA 3.3.

| Pos. | Stckz. | Benennung/Daten                   | Bemerkung                |

|------|--------|-----------------------------------|--------------------------|

| 1    | 1      | Leiterplatte BFZ/MFA 3.3.         |                          |

| 2    | 9      | IC-Fassung 28polig                |                          |

| 3    | 1      | IC-Fassung 20polig                |                          |

| 4    | 2      | IC-Fassung 16polig                |                          |

| 5    | 2      | IC-Fassung 14polig                |                          |

| 6    | 1      | Lötstift/-nagel für 1,3 mm Loch-Ø | Meßstift für Masse (0 V) |

---

Bestückung Leiterplatte

---

## Bauteilliste Leiterplatte BFZ/MFA 3.3.

| Kennz.    | Benennung/Daten                | Bemerkung |

|-----------|--------------------------------|-----------|

| C1...C4   | Tantal-E1ko 4,7 µF/35 V        |           |

| IC1...IC8 | RAM-Baustein 8K x 8 Bit        |           |

| IC9       | Acht Bus-Transceiver 74 LS 245 | Tri-State |

| IC10      | 3-Bit-Binärdekoder 74 LS 138   |           |

| IC11      | 4-Bit-Vergleicher 74 LS 85     |           |

| IC12      | Vier NAND-Gatter 74 LS 00      |           |

| IC13      | Vier ODER-Gatter 74 LS 32      |           |

Bereitstellungsliste zur Inbetriebnahme

Zur Inbetriebnahme bzw. Prüfung der Baugruppe "64-KByte-RAM" wird folgendes Material benötigt:

| Stckz. | Benennung/Daten                                     | Bemerkung                                                 |

|--------|-----------------------------------------------------|-----------------------------------------------------------|

| 1      | Baugruppenträger mit Busverdrahtung<br>BFZ/MFA 0.1. | All die Baugruppen<br>komplett aufge-<br>baut und geprüft |

| 1      | Bus-Abschluß BFZ/MFA 0.2.                           |                                                           |

| 1      | Trafo-Einschub BFZ/MFA 1.1.                         |                                                           |

| 1      | Spannungsregelung BFZ/MFA 1.2.                      |                                                           |

| 1      | Prozessor 8085 BFZ/MFA 2.1.                         |                                                           |

| 1      | 8-Bit-Parallel-Ausgabe BFZ/MFA 4.1.                 |                                                           |

| 1      | Bus-Signalgeber BFZ/MFA 5.1.                        |                                                           |

| 1      | Bus-Signalanzeige BFZ/MFA 5.2.                      |                                                           |

| 1      | Prüf-EPROM BFZ/MFA 3.3.P1                           | wird während der Inbetrieb-<br>nahme programmiert         |

Zur Programmierung eines Prüf-EPROMs wird zusätzlich folgendes Material benötigt:

| Stckz. | Benennung/Daten                                                   | Bemerkung                                                                       |

|--------|-------------------------------------------------------------------|---------------------------------------------------------------------------------|

| 1      | 8-K-RAM/EPROM BFZ/MFA 3.1., einge-<br>richtet als EPROM-Baugruppe | bestückt mit MAT 85                                                             |

| 1      | 8-K-RAM/EPROM BFZ/MFA 3.1., einge-<br>richtet als RAM-Baugruppe   | bestückt mit mind. zwei<br>Stück 2-K-RAM-Bausteinen<br>ab Adresse F800 und E000 |

| 1      | EPROM-Programmierer BFZ/MFA 4.3.a                                 |                                                                                 |

| 1      | ASCII-Tastatur BFZ/MFA 8.1.                                       |                                                                                 |

| 1      | Video-Interface BFZ/MFA 8.2.                                      |                                                                                 |

| 1      | Datensichtgerät                                                   |                                                                                 |

| 1      | Gleichspannungsnetzgerät                                          | auf 27 V einstellbar, 1 A                                                       |

| 1      | EPROM 2K x 8 Bit, max. 350 ns,<br>INTEL-kompatibel, z.B. 2716     | unprogrammiert                                                                  |

---

## Inbetriebnahme

---

### 1. Sichtkontrolle

Die Sichtkontrolle wird anhand von Stromlauf- und Bestckungsplan sowie Stück- und Bauteilliste durchgeführt.

- Sind alle Lötstellen ordnungsgemäß verlötet?

- Sind die Kondensatoren richtig gepolt?

- Sind alle ICs richtig eingesteckt?

- Sind alle Schrauben festgezogen?

### 2. Prüfen der Funktion

Folgende Lötbrücken müssen geschlossen sein: Im Brückenzeld...

- "RAM-Aktiv-Adr.": A-L, B-L, C-L, D-L

- "ROM-Absch.-Adr.": 8000

- "ROM n. absch. - absch.": absch.

- "ROM-Typ": A-H, B-H

#### 2.1. Statische Überprüfung der 64-KByte-RAM-Baugruppe

Die statische Überprüfung erfolgt mit Hilfe eines TTL-Testers oder Vielfach-Meßinstrumentes. Zur Erzeugung und Anzeige der erforderlichen Adreß-, Daten- und Steuersignale dienen Bus-Signalgeber und Bus-Signalanzeige.

Bestückung des Baugruppenträgers:

- Bus-Signalgeber

- Bus-Signalanzeige

- 64-KByte-RAM (über Adapterkarte)

---

Inbetriebnahme

---

2.1.1.  $\overline{CS}$  der RAMs

- Bus-Signalgeber-Schalter "ON/OFF" in Stellung "ON"

- Adreßeinstellung lt. Tabelle und Überprüfung der  $\overline{CS}$ -Signale jeweils an Pin 20 von IC1 bis IC8

| ADDRESS<br>(eingest.) | Pegel an den $\overline{CS}$ -Anschlüssen (Pin 20) von ... |     |     |     |     |     |     |     |

|-----------------------|------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

|                       | IC1                                                        | IC2 | IC3 | IC4 | IC5 | IC6 | IC7 | IC8 |

| 0000                  | L                                                          | H   | H   | H   | H   | H   | H   | H   |

| 2000                  | H                                                          | L   | H   | H   | H   | H   | H   | H   |

| 4000                  | H                                                          | H   | L   | H   | H   | H   | H   | H   |

| 6000                  | H                                                          | H   | H   | L   | H   | H   | H   | H   |

| 8000                  | H                                                          | H   | H   | H   | L   | H   | H   | H   |

| A000                  | H                                                          | H   | H   | H   | H   | L   | H   | H   |

| C000                  | H                                                          | H   | H   | H   | H   | H   | L   | H   |

| E000                  | H                                                          | H   | H   | H   | H   | H   | H   | L   |

2.1.2. Datenflußrichtung,  $\overline{OE}$  des EPROMs,  $\overline{WE}$  der RAMs

- Bei betätigter MEMR-Taste muß an Pin 1 von IC9 und an Pin 22 von IC0 L-Pegel auftreten.

- Bei betätigter MEMW-Taste muß jeweils an Pin 27 von IC1 bis IC8 L-Pegel auftreten.

**Inbetriebnahme****2.1.3. EPROM-Abschalt-Logik**

- CPU-Baugruppe zusätzlich im Baugruppenträger

- Bus-Signalgeber-Schalter "ON/OFF" in Stellung "ON"

- Einmal Taste "RESET" betätigt

- Messung der Pegel lt. Tabelle (Reihenfolge einhalten!)

| ADRESS<br>(eingest.) | Taste<br>MEMR | IC 12.3<br>Pin 8 | IC 13.2<br>Pin 6 | IC 0<br>Pin 20 | IC 1<br>Pin 22 | IC 5<br>Pin 22 | Bemerkung         |

|----------------------|---------------|------------------|------------------|----------------|----------------|----------------|-------------------|

| 0000                 | n.b.          | L                | L                | L              | H              | H              |                   |

| 0000                 | bet.          | L                | L                | L              | H              | H              | EPROM aktiv       |

| 7FFF                 | n.b.          | L                | H                | H              | H              | H              |                   |

| 7FFF                 | bet.          | L                | H                | H              | L              | L              | EPROM n. abgesch. |

| 8000                 | n.b.          | L                | H                | H              | H              | H              |                   |

| 8000                 | bet.          | H                | H                | H              | L              | L              | EPROM abgesch.    |

| 0000                 | n.b.          | H                | L                | H              | H              | H              |                   |

| 0000                 | bet.          | H                | L                | H              | L              | L              | RAM aktiv         |

n.b. = nicht betätigt

bet. = betätigt

**2.2. Dynamische Prüfung der 64-KByte-RAM-Baugruppe**

Die dynamische Prüfung erfolgt mit Hilfe eines Programms, das alle 65536 Speicherstellen der 64-KByte-RAM-Baugruppe testet. In den nächsten Arbeitsschritten wird die Erstellung eines 2-KByte-EPROMs beschrieben, welches das RAM-Testprogramm enthält.

---

Inbetriebnahme

---

### 2.2.1. Schritte zur Programmierung eines Prüf-EPROMs

Bestückung des Baugruppenträgers:

- CPU 8085

- Video-Interface mit Tastatur und Datensichtgerät

- 8-K-RAM/EPROM, bestückt mit MAT 85

- 8-K-RAM/EPROM, bestückt mit mind. 4-K-RAM ab Adresse E000 und F800

- EPROM-Programmierer (mit 27 V versorgt)

- Eingabe des folgenden RAM-Prüfprogramms mit dem Kommando "MEMORY" ab Adresse E000:

```

E000 31 FF FF F3 21 00 20 36

E008 00 23 7C FE FF C2 07 00

E010 16 3F 06 55 21 00 20 78

E018 77 2F 47 23 7D FE FF C2

E020 17 00 7C BA C2 17 00 21

E028 00 20 06 55 78 BE C2 57

E030 00 2F 47 23 7D FE FF C2

E038 2C 00 7C BA C2 2C 00 7A

E040 C6 20 57 23 AF BE C2 57

E048 00 7D FE FF C2 43 00 7C

E050 BA C2 43 00 C3 5C 00 2B

E058 3E 76 77 E9 21 6F 00 11

E060 00 20 06 76 7E 12 23 13

E068 05 C2 64 00 C3 00 20 16

E070 5F 21 00 40 2B 23 06 55

E078 78 77 2F 47 23 7D FE FF

E080 C2 09 20 7C BA C2 09 20

E088 23 7C D6 20 67 06 55 78

E090 BE C2 5E 20 2F 47 23 7D

E098 FE FF C2 20 20 7C BA C2

E0A0 20 20 FE 1F CA 63 20 7A

E0A8 C6 20 57 FE FF CA 06 20

E0B0 FE 1F CA 06 20 23 AF BE

E0B8 C2 5E 20 7D FE FF C2 46

E0C0 20 7C BA C2 46 20 7C D6

E0C8 20 67 C3 06 20 2B 3E 76

E0D0 77 E9 06 55 D3 00 11 FF

E0D8 4F 1B 7B B2 C2 6A 20 78

EOE0 2F 47 C3 65 20 00 00 00

```

- Kontrolle des eingegebenen RAM-Prüfprogramms mit dem Kommando "PRINT"

- Programmierung des EPROMs 2716 (Adresse 1E06 aufrufen, Start-Adr. E000)

---

Inbetriebnahme

---

### 2.2.2. Dynamische Prüfung der 64-KByte-RAM-Baugruppe

- Prüf-EPROM wie dargestellt in den Sockel für ICO der 64-KByte-RAM-Baugruppe gesteckt

- Bestückung des Baugruppenträgers: CPU 8085

64-KByte-RAM

Bus-Signalanzeige

8-Bit-Parallel-Ausgabe (Port-Adr. 00)

- Schalter "ON/OFF" der Bus-Signalanzeige in Stellung "OFF"

- Schalter "HLT/RUN" der Bus-Signalanzeige in Stellung "RUN"

- Netzteil eingeschaltet

Beginnen nach kurzer Zeit die Leuchtdioden der 8-Bit-Parallel-Ausgabe zu blinken, so ist die 64-KByte-RAM-Baugruppe in Ordnung. Die Betriebsspannung kann dann abgeschaltet, die RAM-Baugruppe gezogen und das Prüf-EPROM entfernt werden.

Ist dies jedoch nicht der Fall, so ist die 64-KByte-RAM-Baugruppe defekt. Erscheint auf der Bus-Signalanzeige eine stabile Anzeige (z.B. ADDRESS: 6000, DATA: FF), gibt die Adresse die letzte regulär arbeitende Speicherstelle (gezählt ab 0000) an.

Nach der Reparatur der Baugruppe ist oben beschriebene Inbetriebnahme zu wiederholen.

Damit ist die Inbetriebnahme beendet.

## Bereitstellungsliste

| Stckz. | Benennung/Daten                                                | Bemerkung                                   |

|--------|----------------------------------------------------------------|---------------------------------------------|

| 1      | Leiterplatte, BFZ/MFA 3.3.                                     |                                             |

| 1      | Frontplatte, Teilung L-C 05<br>Alu, 2 mm dick, Breite: 25,1 mm | z.B. Intermas<br>Nr. 409-017 665            |

| 1      | Griff komplett mit Abdeckung T03                               | z.B. Intermas<br>Nr. 409-017 927            |

| 1      | Frontverbinder 1,6 FEE                                         | z.B. Intermas<br>Nr. 409-024 830            |

| 1      | Messerleiste 64polig, DIN 41612                                | z.B. Erni STV-P-364 a/c<br>Nr. 9722.333.401 |

| 1      | Zylinderschraube M2,5x8 DIN 84                                 |                                             |

| 2      | Zylinderschraube M2,5x10 DIN 84                                |                                             |

| 3      | Zylinderschraube M2,5x12 DIN 84                                |                                             |

| 2      | Zylinderschraube mit Schaft<br>BM2,5x10/5 DIN 84               |                                             |

| 2      | Schraubensicherung, Kunststoff                                 |                                             |

| 5      | Federscheibe A2,7 DIN 137                                      | z.B. Intermas<br>Nr. 409-026 748            |

| 1      | Federring B2,5 DIN 127                                         |                                             |

| 4      | Sechskantmutter M2,5 DIN 439                                   |                                             |

| 4      | Tantal-Elko 4,7 µF/35 V                                        | Tropfenform                                 |

| 1      | IC 74 LS 00, Vier NAND-Gatter                                  |                                             |

| 1      | IC 74 LS 32, Vier ODER-Gatter                                  |                                             |

| 1      | IC 74 LS 85, 4-Bit-Vergleicher                                 |                                             |

| 1      | IC 74 LS 138, 3-Bit-Binärdekoder                               |                                             |

| 1      | IC 74 LS 245, Acht Bus-Transceiver                             | Tri-State                                   |

## Bereitstellungsliste

| Stckz. | Benennung/Daten                                                           | Bemerkung                          |

|--------|---------------------------------------------------------------------------|------------------------------------|

| 8      | RAM-Baustein 8K x 8 Bit, statisch,<br>max. 300 ns, pinkompatibel mit 6264 | z.B. HM 6264<br>MB 8464-15L        |

| 9      | IC-Fassung 28polig DIL                                                    |                                    |

| 1      | IC-Fassung 20polig DIL                                                    |                                    |

| 2      | IC-Fassung 16polig DIL                                                    |                                    |

| 2      | IC-Fassung 14polig DIL                                                    |                                    |

| 1      | Lötstift/Lötnagel für 1,3 mm Loch-Ø                                       | Meßstift für Masse (0 V)           |

| n.B.   | Lötdraht                                                                  |                                    |

| n.B.   | Lötlack                                                                   |                                    |

| n.B.   | Reinigungsmittel                                                          | zum Entfetten der<br>Frontplatte   |

| n.B.   | Beschriftungsmaterial, Abreibe-<br>symbole oder Tuscheschreiber           | zum Beschriften der<br>Frontplatte |

| n.B.   | Plastik-Spray                                                             | zum Besprühen der<br>Frontplatte   |

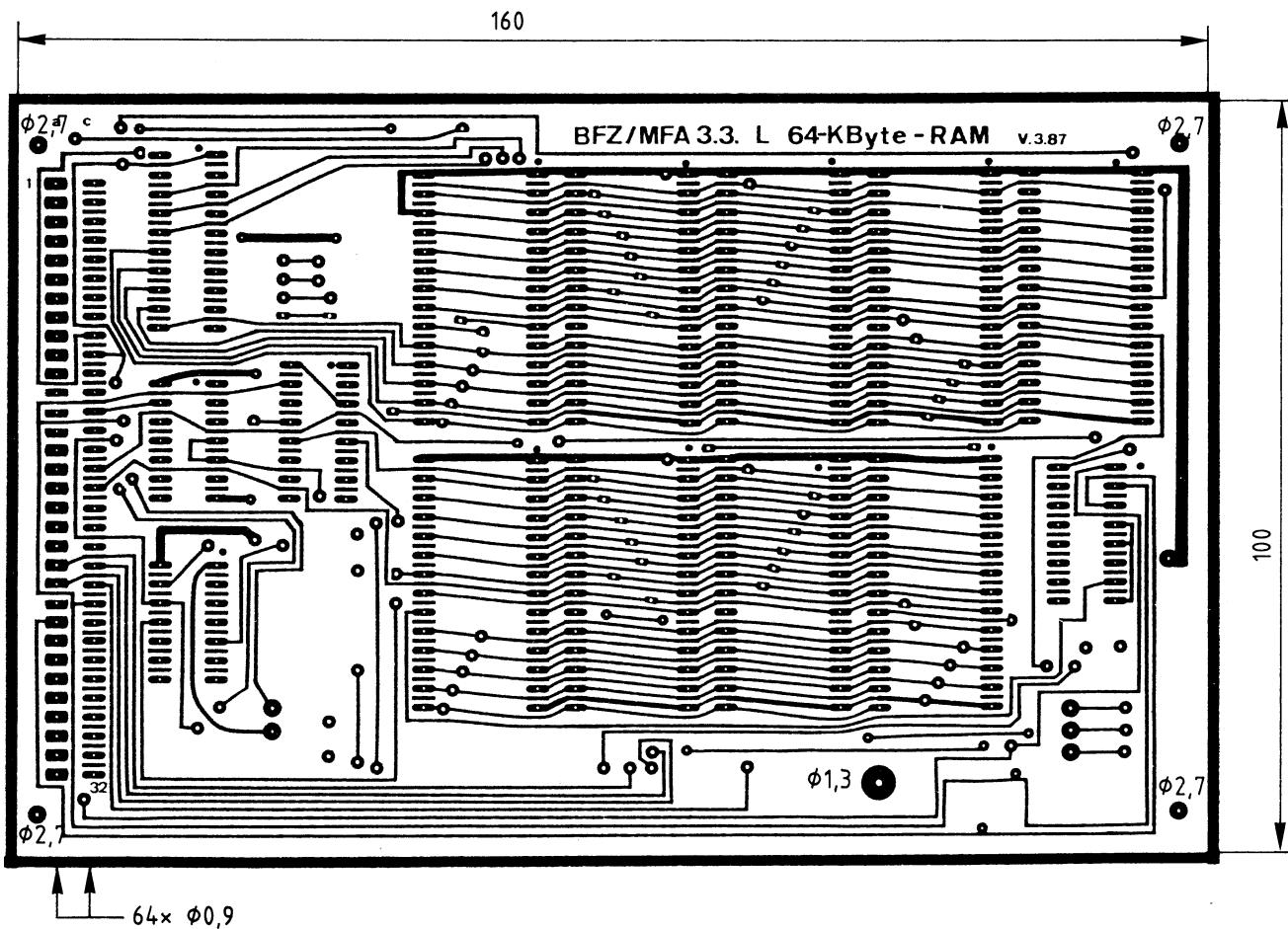

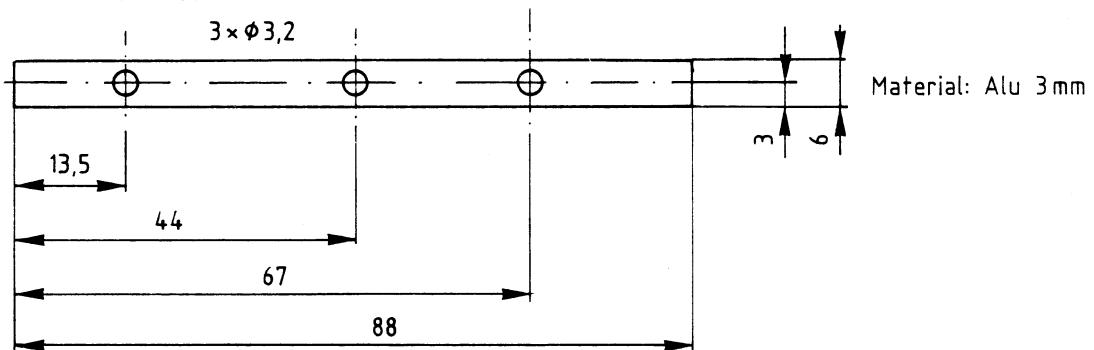

## Bohrplan Leiterplatte

Alle nicht bemaßten Bohrungen  $\phi 0,8$  mm

Benötigte Bohrer: 0,8 - 0,9 - 1,3 - 2,7 mm

## Layout Bestückungsseite

Beschriftung Frontplatte

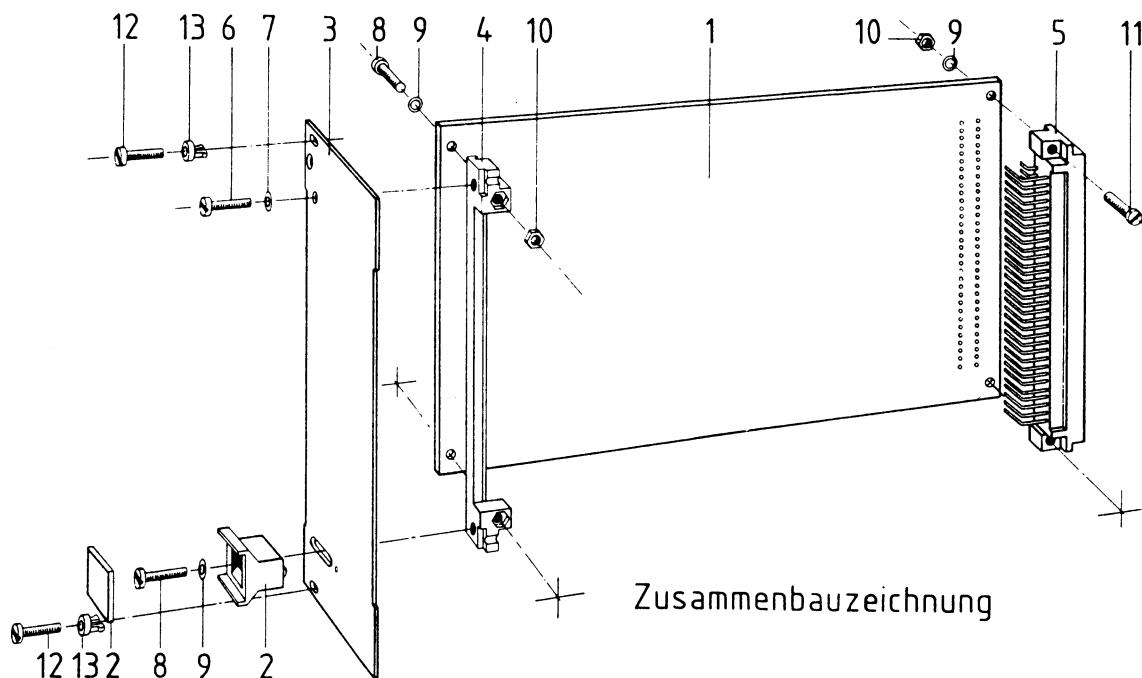

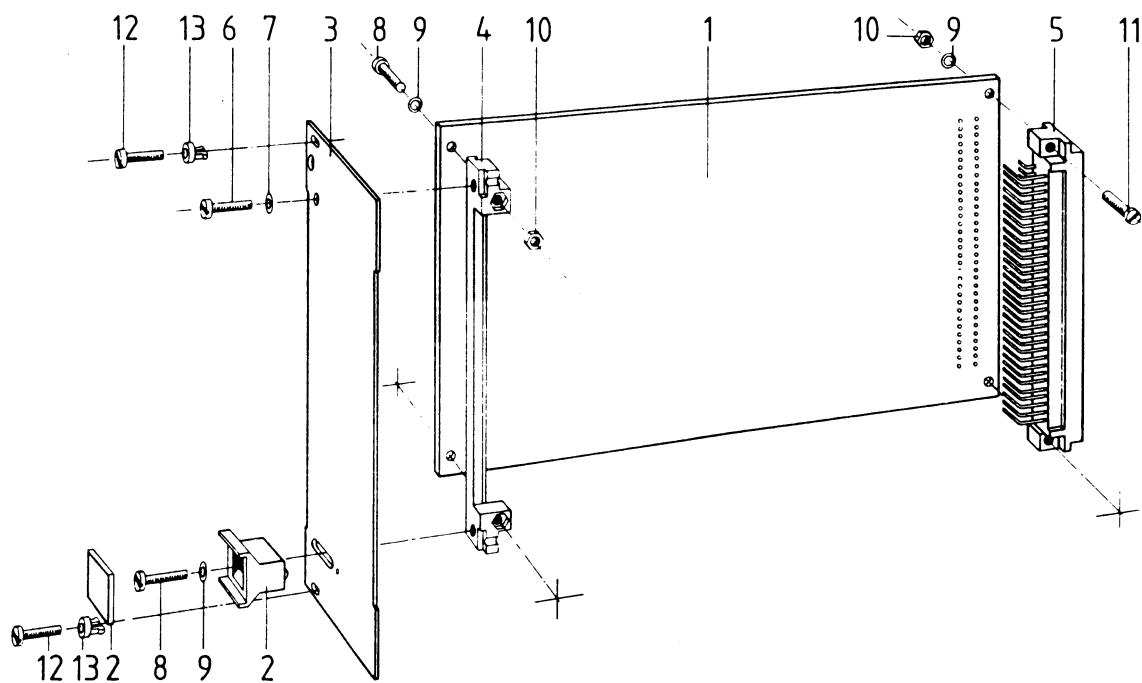

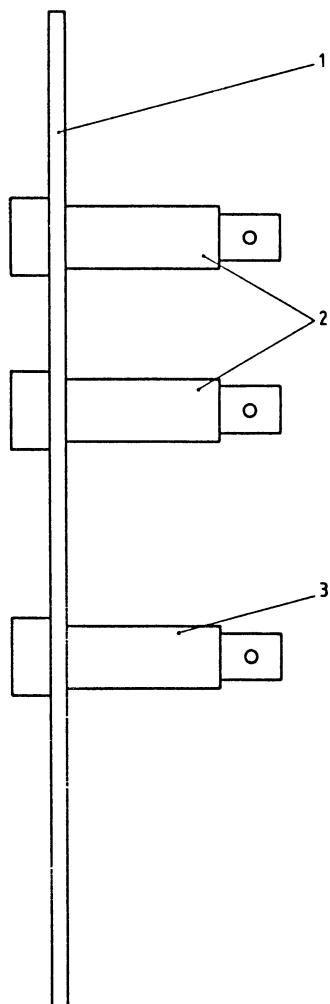

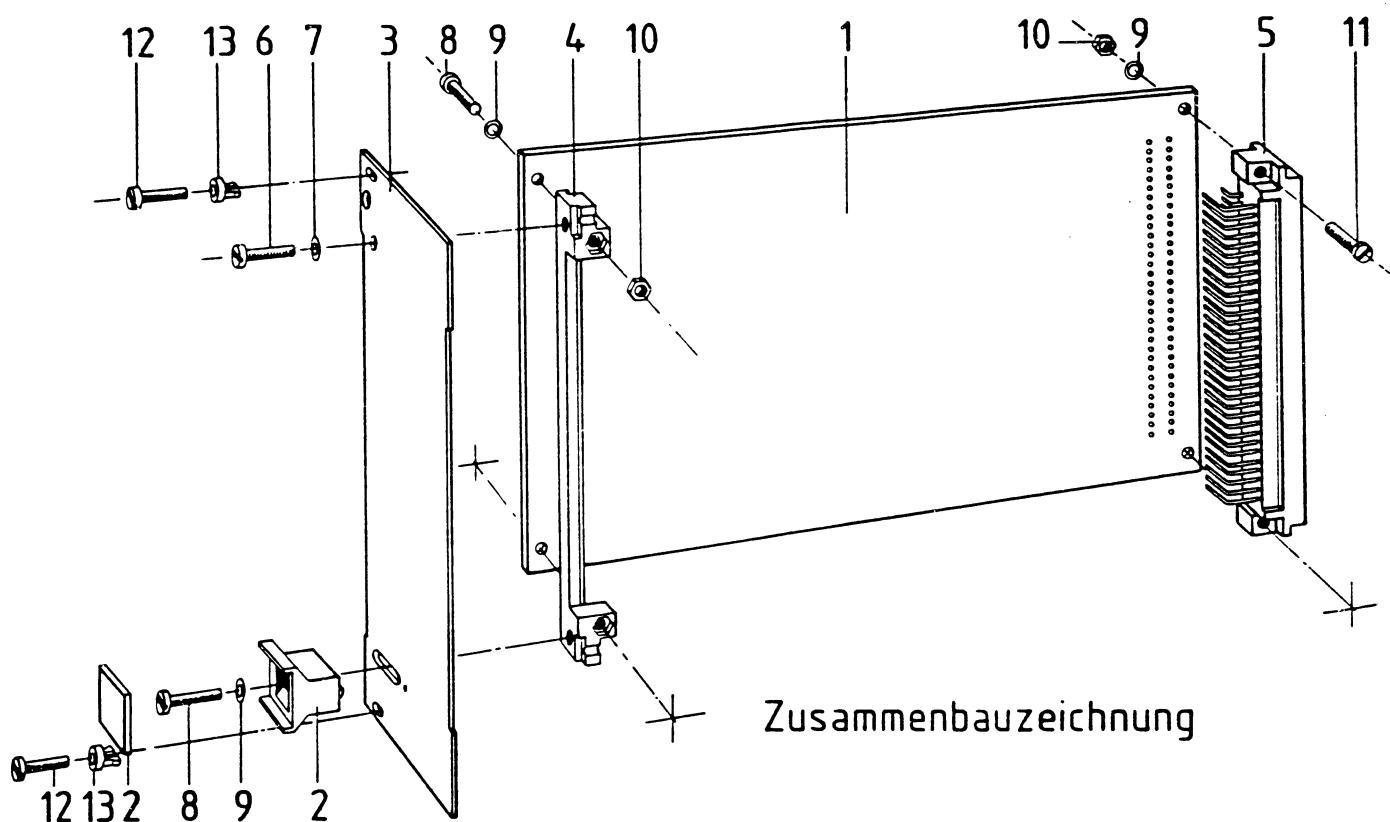

## Zusammenbau Baugruppe

## Stückliste für den Zusammenbau

| Pos. | Stckz. | Benennung/Daten                                   | Bemerkung         |

|------|--------|---------------------------------------------------|-------------------|

| 1    | 1      | Leiterplatte BFZ/MFA 3.3.                         | komplett bestückt |

| 2    | 1      | Griff komplett                                    |                   |

| 3    | 1      | Frontplatte                                       |                   |

| 4    | 1      | Frontverbinder                                    |                   |

| 5    | 1      | Messerleiste 64polig, DIN 41612                   |                   |

| 6    | 1      | Zylinderschraube M2,5x8 DIN 84                    |                   |

| 7    | 1      | Federring B2,5 DIN 127                            |                   |

| 8    | 3      | Zylinderschraube M2,5x12 DIN 84                   |                   |

| 9    | 5      | Federscheibe A2,7 DIN 137                         |                   |

| 10   | 4      | Sechskantmutter M2,5 DIN 439                      |                   |

| 11   | 2      | Zylinderschraube M2,5x10 DIN 84                   |                   |

| 12   | 2      | Zylinderschraube mit Schaft,<br>BM2,5x10/5 DIN 84 |                   |

| 13   | 2      | Schraubensicherung, Kunststoff                    |                   |

# FACHPRAKTISCHE ÜBUNG

## MIKROCOMPUTER-TECHNIK

8-Bit-Parallel-Eingabe

(galv. getrennt)

BFZ/MFA 4.8.

---

Inhaltsverzeichnis

---

| Inhalt                                  | Seite |

|-----------------------------------------|-------|

| Hinweise                                | 1     |

| Blockschaltbild                         | 2     |

| Funktionsbeschreibung                   | 3     |

| Technische Daten                        | 3     |

| Stromlaufplan                           | 4     |

| Bestückung Leiterplatte                 | 5     |

| Bereitstellungsliste zur Inbetriebnahme | 7     |

| Inbetriebnahme                          | 8     |

| Bereitstellungsliste                    | 11    |

| Bohrplan Leiterplatte                   | 13    |

| Layout Bestückungsseite                 | 14    |

| Bohrplan Frontplatte                    | 15    |

| Zusammenbau Baugruppe                   | 16    |

**Hinweise**

Die 8-Bit-Parallel-Eingabe-Baugruppe mit galvanisch getrennten Eingängen ist für den Anschluß von Modellen und Anlagen an den BFZ/MFA-Mikrocomputer vorgesehen. Die Baugruppe sollte immer dann eingesetzt werden, wenn die Gefahr von Störeinkopplungen besteht, wie z.B. beim Schalten von induktiven Lasten. Darüber hinaus wird sie notwendig, wenn Sensoren und Signalgeber mit externen Betriebsspannungen an den Mikrocomputer angeschlossen werden sollen. Zur galvanischen Trennung besitzen die acht Eingänge Optokoppler.

Die Eingangsspannung der Baugruppe darf bis zu 24 V betragen (Gleichspannung), wobei Werte zwischen 0 V und 2 V L-Pegel und Werte zwischen 5 V und 24 V H-Pegel entsprechen. Der maximale Eingangsstrom bei H-Pegel beträgt ca. 10 mA.

Da diese Werte weitgehend den Daten industrieüblicher SPS-Steuerungen entsprechen, ist die Baugruppe auch für den Ausbau des BFZ/MFA-Mikrocomputers zur SPS-Steuerung geeignet.

Der hierzu erforderliche SPS-Interpreter ist Bestandteil der "Software-Erweiterung SP 1" zum BFZ/MFA-Mikrocomputer (siehe im Band "Fachtheoretische Übungen"). Einzelheiten zum Betrieb von Eingabe-Ports sind in der Übung "8-Bit-Parallel-Eingabe" (BFZ/MFA 4.2.) beschrieben.

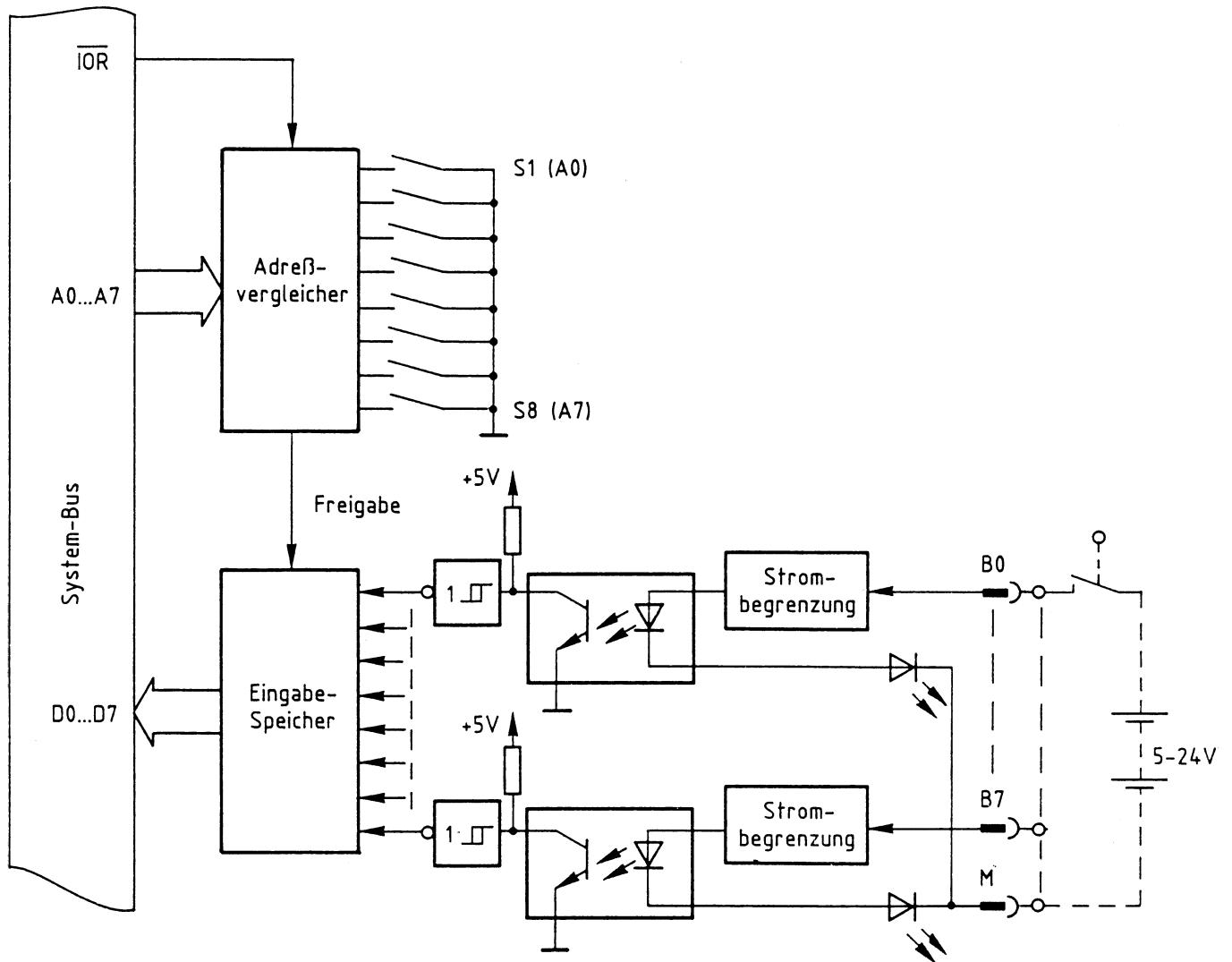

## Blockschaltbild

## Funktionsbeschreibung

---

Die Funktionsbeschreibung bezieht sich nur auf das Blockschaltbild und ist für den Ausbilder gedacht. Schaltungseinzelheiten werden nicht behandelt.

Die Baugruppe "8-Bit-Parallel-Eingabe (galv. getrennt)" besitzt acht Eingänge mit Optokopplern zur galvanischen Trennung zwischen den Potentialen des Eingangskreises und des Mikrocomputers.

Die Eingangsspannung kann maximal 24 V betragen. Werte oberhalb von 5 V werden als H-Pegel und unterhalb von 2 V als L-Pegel erkannt.

Bei offenem Eingang (z.B. B0) fließt im Eingangskreis kein Strom und der Fototransistor des Optokopplers ist gesperrt. Hierdurch erhält der Eingang des invertierenden Schmitt-Triggers H-Pegel und der Eingang des Eingabe-Speichers L-Pegel. Wird z.B. an B0 eine Spannung zwischen 5 V und 24 V angelegt, so fließt ein auf ca. 10 mA begrenzter Strom durch die LED des Optokopplers und durch die Kontroll-LED, die sich auf der Frontplatte der Baugruppe befindet. Die Optokoppler-LED steuert den Fototransistor durch, so daß der Eingang des invertierenden Schmitt-Triggers nun L-Pegel und der Eingang des Eingabe-Speichers H-Pegel erhält.

Die Eingabe-Daten gelangen nur bei Freigabe des Eingabe-Speichers auf den Daten-Bus. Die Freigabe erfolgt, wenn der Prozessor die richtige Port-Adresse (mit S1 bis S8 einstellbar) und das Steuersignal  $\overline{IOR}$  ausgibt.

## Technische Daten

- \* Acht galvanisch getrennte Eingänge (Optokoppler) mit gemeinsamem Bezugspotential; Eingangssignalanzeige für jedes Bit; einstellbare Portadresse

- \* Eingangsspannung für L-Pegel: 0 V bis 2 V (Gleichspannung)

für H-Pegel: 5 V bis 24 V (Gleichspannung)

- \* Eingangsstrom für H-Pegel: 2 mA

bei 5 V Eingangsspannung : ca. 6 mA

ab 8 V Eingangsspannung : auf 10 mA begrenzt

- \* Anschluß von Sensoren, Signalgebern, Modellen und Anlagen, Realisierung von SPS-Steuerungen mit dem BFZ/MFA-Computer

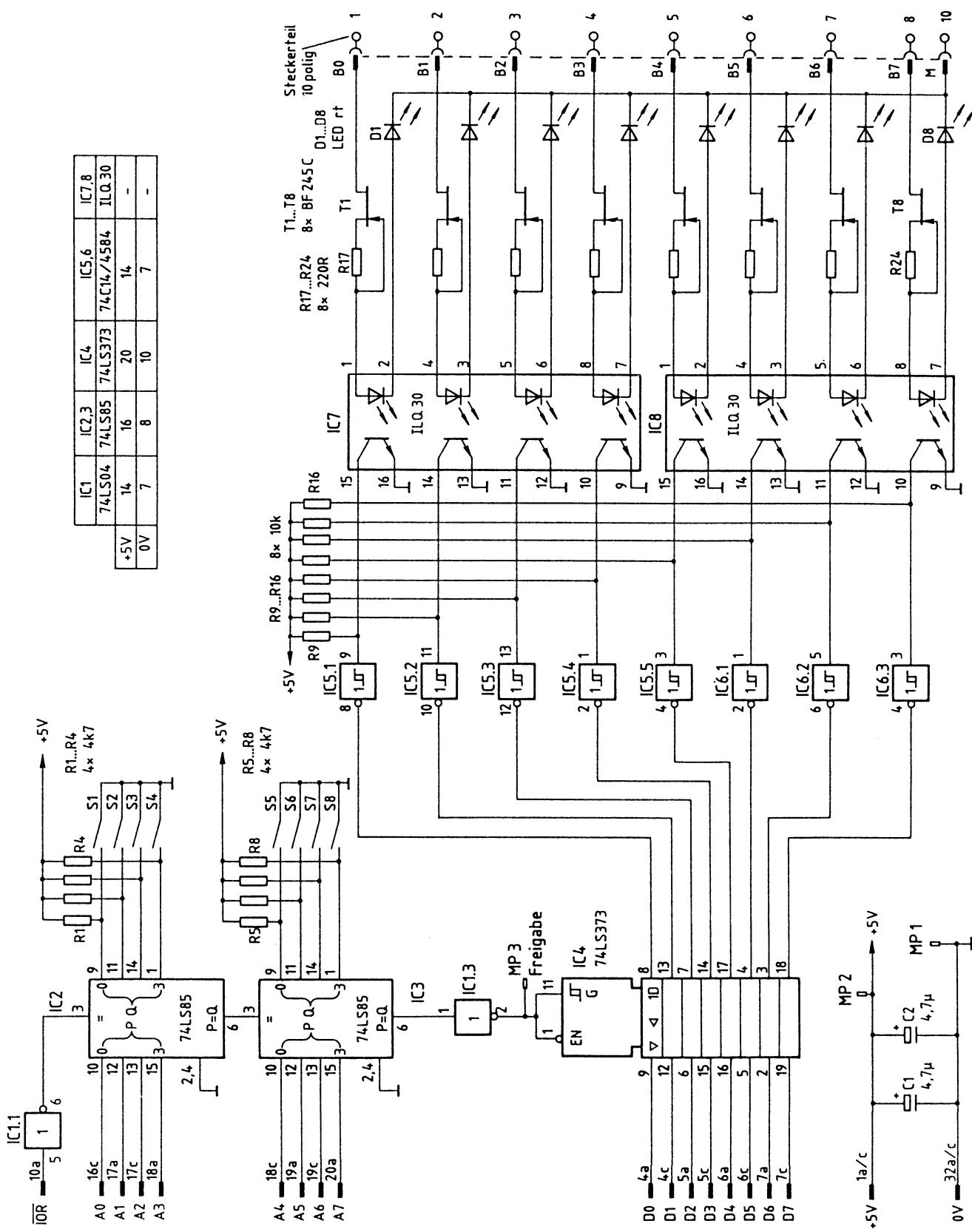

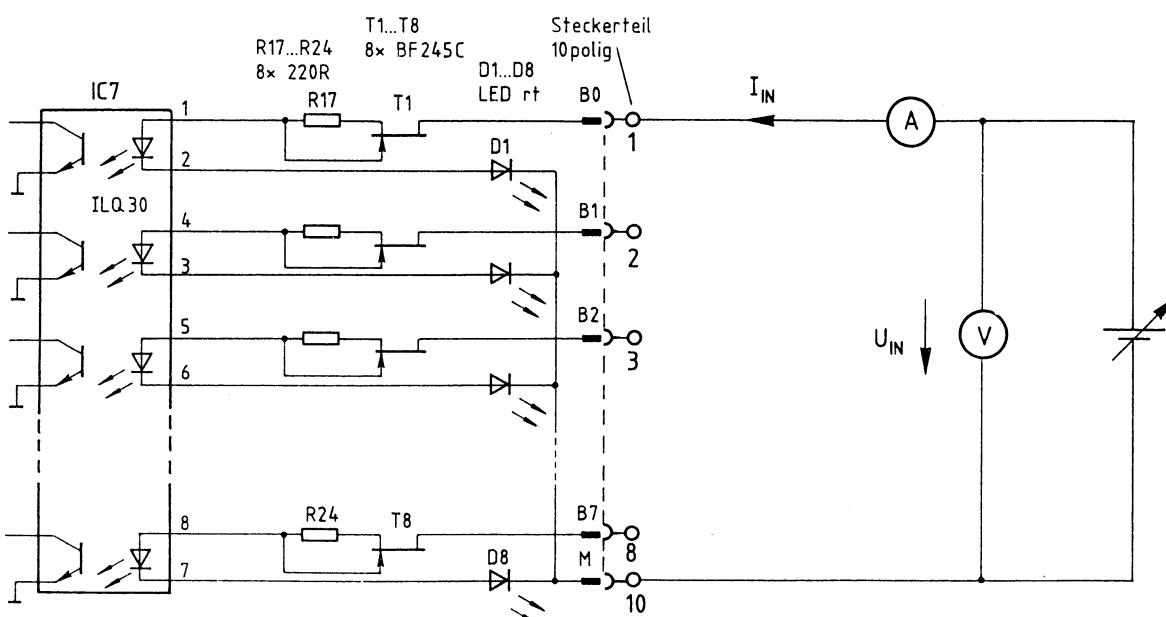

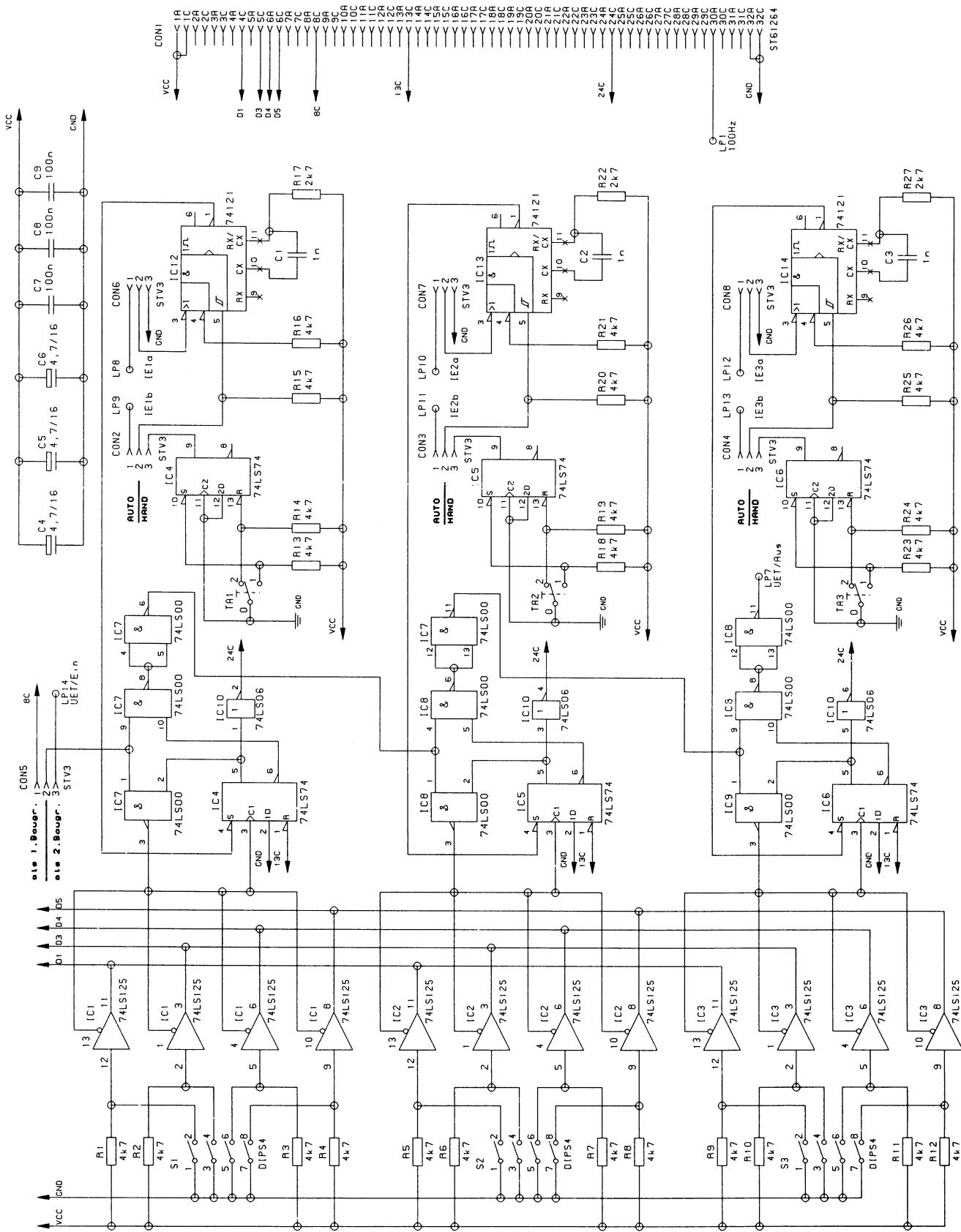

## Stromlaufplan

Stromlaufplan 8-Bit-Parallel-Eingabe (galv. getrennt)

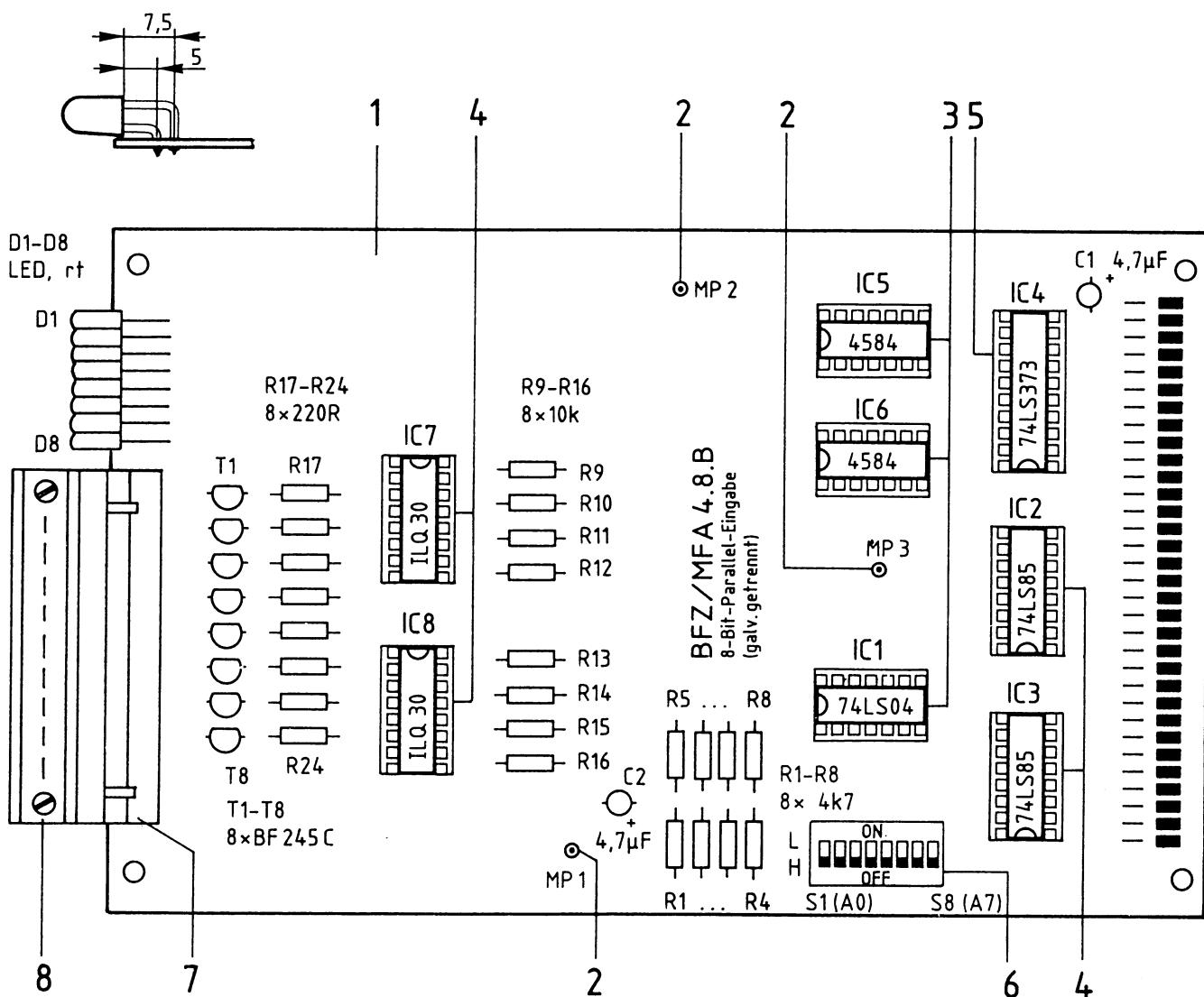

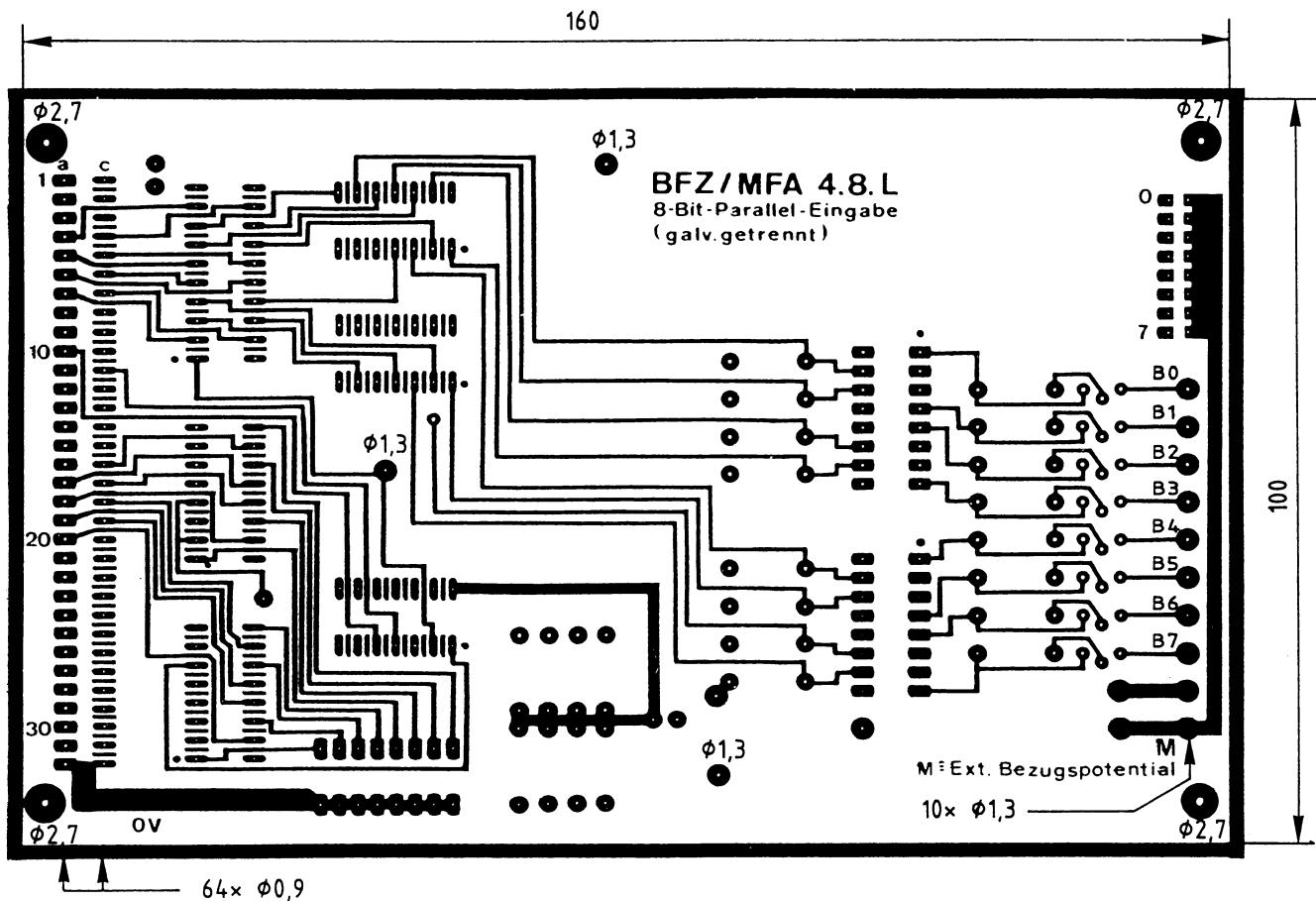

## Bestückung Leiterplatte

Stückliste Leiterplatte BFZ/MFA 4.8.

| Pos. | Stckz. | Benennung/Daten                   | Bemerkung           |

|------|--------|-----------------------------------|---------------------|

| 1    | 1      | Leiterplatte BFZ/MFA 4.8.         |                     |

| 2    | 3      | Lötstift/-nagel für 1,3 mm Loch-Ø | Meßpunkte MP1 – MP3 |

| 3    | 3      | IC-Fassung 14polig                |                     |

| 4    | 4      | IC-Fassung 16polig                |                     |

| 5    | 1      | IC-Fassung 20polig                |                     |

| 6    | 1      | Miniatur-Schiebeschalter 8polig   |                     |

| 7    | 1      | Grundgehäuse 10polig              |                     |

| 8    | 1      | Steckerteil 10polig               |                     |

## Bestückung Leiterplatte

## Bauteilliste Leiterplatte BFZ/MFA 4.8.

| Kennz.    | Benennung/Daten             | Bemerkung                               |

|-----------|-----------------------------|-----------------------------------------|

| R1...R8   | Widerstand 4,7 kΩ           | Alle Widerstände<br><u>±5%</u> , 0,25 W |

| R9...R16  | Widerstand 10 kΩ            |                                         |

| R17...R24 | Widerstand 220Ω             |                                         |

| C1, C2    | Tantal-Elko 4,7 µF/35 V     | Tropfenform                             |

| IC1       | Sechs Inverter 74 LS 04     |                                         |

| IC2, IC3  | 4-Bit-Vergleicher 74 LS 85  |                                         |

| IC4       | 8-Bit-D-Flipflop 74 LS 373  |                                         |

| IC5, IC6  | 6 Inv. Schmitt-Trigger 4584 | oder 74 C 14                            |

| IC7, IC8  | 4-fach Optokoppler ILQ 30   | oder ILQ 74                             |

| T1...T8   | Sperrsicht-FET BF 245 C     |                                         |

| D1...D8   | LED, rot, anreihbar         | abgewinkelt montiert                    |

---

Bereitstellungsliste zur Inbetriebnahme

---

Zur Inbetriebnahme bzw. Prüfung der Baugruppe "8-Bit-Parallel-Eingabe (galv. getrennt)" wird folgendes Material benötigt:

| Stckz. | Benennung/Daten                                                  | Bemerkung                                              |

|--------|------------------------------------------------------------------|--------------------------------------------------------|

| 1      | Baugruppenträger mit Busverdrahtung<br>BFZ/MFA 0.1.              | Alle Baugruppen<br>komplett aufge-<br>baut und geprüft |

| 1      | Bus-Abschluß BFZ/MFA 0.2.                                        |                                                        |

| 1      | Trafo-Einschub BFZ/MFA 1.1.                                      |                                                        |

| 1      | Spannungsregelung BFZ/MFA 1.2.                                   |                                                        |

| 1      | Bus-Signalgeber BFZ/MFA 5.1.                                     |                                                        |

| 1      | Bus-Signalanzeige BFZ/MFA 5.2.                                   |                                                        |

| 1      | Adapterkarte 64polig BFZ/MFA 5.3.                                |                                                        |

| 1      | Gleichspannungs-Netzgerät, Spannung<br>einstellbar 0...30 V, 1 A |                                                        |

| 2      | Vielfachmeßinstrument                                            |                                                        |

## Inbetriebnahme

---

### 1. Sichtkontrolle

Die Sichtkontrolle wird anhand von Stromlauf- und Bestückungsplan sowie Stück- und Bauteilliste durchgeführt.

- Sind alle Lötstellen ordnungsgemäß verlötet?

- Sind alle Elektrolytkondensatoren richtig gepolt?

- Sind alle ICs richtig eingesteckt?

- Sind alle Schrauben festgezogen?

### 2. Funktionsprüfung

#### 2.1. Prüfen der Eingangsströme

Die Eingänge B0 bis B7 werden einzeln daraufhin überprüft, ob die erforderlichen Ströme eingehalten werden. Der Stromkreis jedes Eingangs besteht aus einem Feldeffekttransistor, der als Strombegrenzer geschaltet ist, einer Optokoppler-LED und einer Kontroll-LED.

- Aufbau der Meßschaltung für Bit 0 nach untenstehendem Bild

---

Inbetriebnahme

---

Messung der Eingangsströme:

- Spannung  $U_{IN}$  auf 2 V eingestellt und  $I_{IN}$  gemessen:  $I_{IN}$  muß kleiner als 0,1 mA sein, die Kontroll-LED für Bit 0 darf nicht leuchten

- Spannung  $U_{IN}$  auf 5 V eingestellt und  $I_{IN}$  gemessen:  $I_{IN}$  muß einen Wert zwischen 4 mA und 8 mA haben, die Kontroll-LED für Bit 0 leuchtet

- Spannung  $U_{IN}$  auf 24 V eingestellt und  $I_{IN}$  gemessen:  $I_{IN}$  darf nicht größer als 12 mA sein, die Kontroll-LED für Bit 0 leuchtet

- Wiederholung dieser Messungen für die Bits B1 bis B7

## 2.2. Prüfen des Freigabesignals und des Eingabe-Speichers

- DIL-Schalter S1 bis S8 der 8-Bit-Parallel-Eingabe (galv. getrennt) in Stellung "ON" geschaltet (Port-Adresse 00), Baugruppe über Adapterkarte in den Baugruppenträger eingesteckt, alle Eingänge frei

- Bus-Signalgeber in den Baugruppenträger eingesteckt, Einstellungen: Schalter "ON/OFF" in Stellung "ON", ADDRESS = 0000, DATA = 55

- Bus-Signalanzeige eingesteckt (beliebige Stellung der Schalter)

- Messung des logischen Pegels am Meßpunkt MP3 gegen 0 V (MP1), Beobachtung der DATA-Anzeige:

1. Keine Steuertaste des Bus-Signalgebers betätigt: H-Pegel an MP3, DATA-Anzeige: "55" (Anzeige der am Bus-Signalgeber eingestellten Daten)

2. Steuertaste "IOR" des Bus-Signalgebers betätigt: L-Pegel an MP3, DATA-Anzeige: "00" (Anzeige der Eingabedaten, B0 bis B7 haben L-Pegel)

3. Neuer Wert für ADDRESS : 0001, Steuertaste "IOR" des Bus-Signalgebers betätigt: H-Pegel an MP3, DATA-Anzeige: "FF" (Bus-Signalgeber zeigt die Daten des "offenen" Daten-Busses an, da falsche Port-Adresse vorliegt)

---

## Inbetriebnahme

---

### 2.3. Überprüfung der Optokoppler

Nun wird geprüft, ob die Optokoppler richtig arbeiten und an B0 bis B7 angelegte Eingabe-Daten richtig gelesen werden können.

- Einstellungen am Bus-Signalgeber: ADDRESS = 0000, DATA = CC

- Anschluß der Eingabe-Bits B0, B2, B4 und B6 an  $U_{IN} = 5 \text{ V}$

1. Die Kontroll-LEDs für B0, B2, B4 und B6 müssen leuchten

2. Bei Betätigung der Taste "IOR" des Bus-Signalgebers muß der Datenwert 55 angezeigt werden

- Anschluß der Eingabe-Bits B1, B3, B5 und B7 an  $U_{IN} = 5 \text{ V}$

1. Die Kontroll-LEDs für B1, B3, B5 und B7 müssen leuchten

2. Bei Betätigung der Taste "IOR" des Bus-Signalgebers muß der Datenwert AA angezeigt werden

Damit ist die Inbetriebnahme beendet

## Bereitstellungsliste

| Stckz. | Benennung/Daten                                                                                     | Bemerkung                                                                                       |

|--------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 1      | Leiterplatte, BFZ/MFA 4.8                                                                           |                                                                                                 |

| 1      | Frontplatte, Teilung L-C 05<br>Alu, 2 mm dick, Breite: 25,1 mm                                      | z.B. Intermas<br>Nr. 409-017 665                                                                |

| 1      | Griff komplett mit Abdeckung T03                                                                    | z.B. Intermas<br>Nr. 409-017 927                                                                |

| 1      | Frontverbinder 1,6 FEE                                                                              | z.B. Intermas<br>Nr. 409-024 830                                                                |

| 1      | Messerleiste 64polig, DIN 41612                                                                     | z.B. Erni STV-P-364 a/c<br>Nr. 9722.333.401                                                     |

| 1      | Combicon-Grundgehäuse 10polig, Einbauraster 5,08 mm, 90°-abgewinkelte Montage, ohne seitliche Wände | Phoenix-Contact<br>Typ MSTB 1,5/10-G-5,08<br>Best. Nr. 175 9091<br>(Postf. 1341, 4933 Blomberg) |

| 1      | Combicon-Steckerteil 10polig, Draht einföhrung in Steckrichtung                                     | Phoenix-Contact<br>Typ MSTB 1,5/10-ST-5,08<br>Best. Nr. 175 7093                                |

| 1      | Zylinderschraube M2,5x8 DIN 84                                                                      |                                                                                                 |

| 2      | Zylinderschraube M2,5x10 DIN 84                                                                     |                                                                                                 |

| 3      | Zylinderschraube M2,5x12 DIN 84                                                                     |                                                                                                 |

| 2      | Zylinderschraube mit Schaft<br>BM2,5x10/5 DIN 84                                                    |                                                                                                 |

| 5      | Federscheibe A2,7 DIN 137                                                                           |                                                                                                 |

| 1      | Federring B2,5 DIN 127                                                                              |                                                                                                 |

| 4      | Sechskantmutter M2,5 DIN 439                                                                        |                                                                                                 |

| 2      | Schraubensicherung, Kunststoff                                                                      | z.B. Intermas<br>Nr. 409-026 748                                                                |

## Bereitstellungsliste

| Stckz. | Benennung/Daten                                             | Bemerkung                       |

|--------|-------------------------------------------------------------|---------------------------------|

| 1      | Miniatur-Schiebeschalter 8polig DIL                         |                                 |

| 8      | Anreih-LED, rt, rechteckig 2,5 x 5 mm                       | z.B. CQX 10                     |

| 2      | Tantal-Elko 4,7 µF/35 V                                     | Tropfenform                     |

| 8      | Widerstand 220Ω                                             | Alle Widerstände<br>±5%, 0,25 W |

| 8      | Widerstand 4,7 kΩ                                           |                                 |

| 8      | Widerstand 10 kΩ                                            |                                 |

| 8      | Sperrsicht-FET BF 245 C                                     |                                 |

| 1      | IC 74 LS 04, Sechs Inverter                                 |                                 |

| 2      | IC 74 LS 85, 4-Bit-Vergleicher                              |                                 |

| 1      | IC 74 LS 373, 8-Bit-D-Flipflop                              |                                 |

| 2      | IC 4584, Sechs inv. Schmitt-Trigger                         | CMOS, oder 74 C 14              |

| 2      | IC ILQ 30, 4-fach Optokoppler                               | oder ILQ 74                     |

| 1      | IC-Fassung 20polig DIL                                      |                                 |

| 4      | IC-Fassung 16polig DIL                                      |                                 |

| 3      | IC-Fassung 14polig DIL                                      |                                 |

| 3      | Lötstift/Lötnagel für 1,3 mm Loch-Ø                         | als Meßpunkte                   |

| n.B.   | Lötdraht                                                    |                                 |

| n.B.   | Lötłack                                                     |                                 |

| n.B.   | Reinigungsmittel                                            | zum Entfetten der Frontplatte   |

| n.B.   | Beschriftungsmaterial, Abreibe-symbole oder Tuscheschreiber | zum Beschriften der Frontplatte |

| n.B.   | Plastik-Spray                                               | zum Besprühen der Frontplatte   |

Das zur Inbetriebnahme der Baugruppe erforderliche Material ist der Bereitstellungsliste zur Inbetriebnahme zu entnehmen.

## Bohrplan Leiterplatte

Alle nicht bemaßten Bohrungen  $\phi 0,8\text{ mm}$

Benötigte Bohrer:  $0,8 - 0,9 - 1,3 - 2,7\text{ mm}$

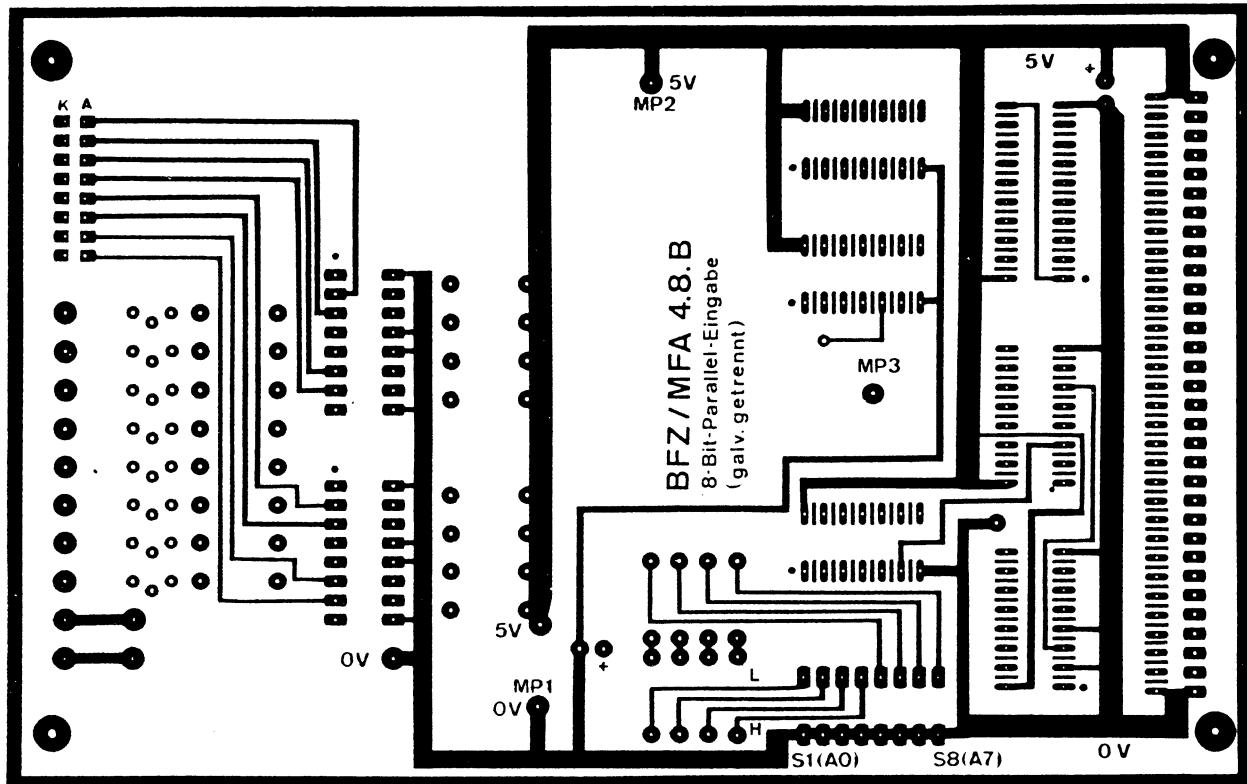

## Layout Bestückungsseite

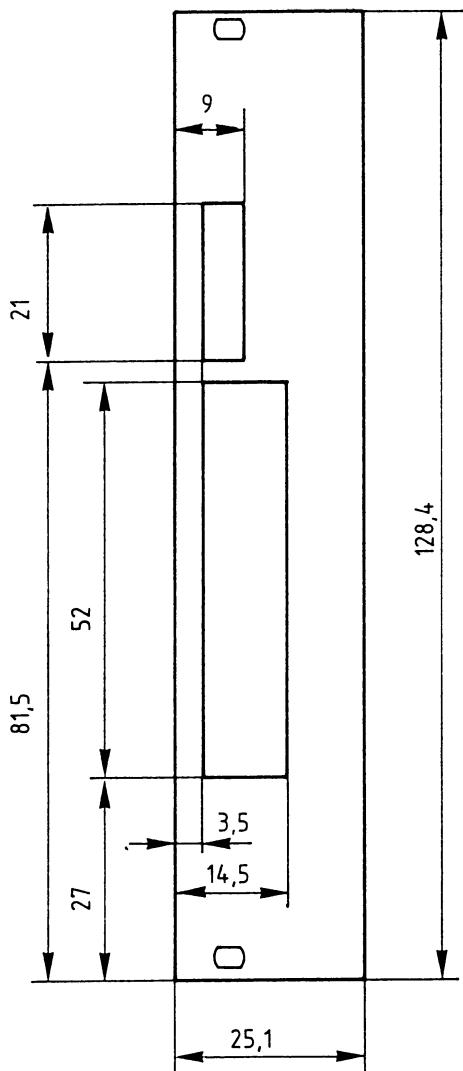

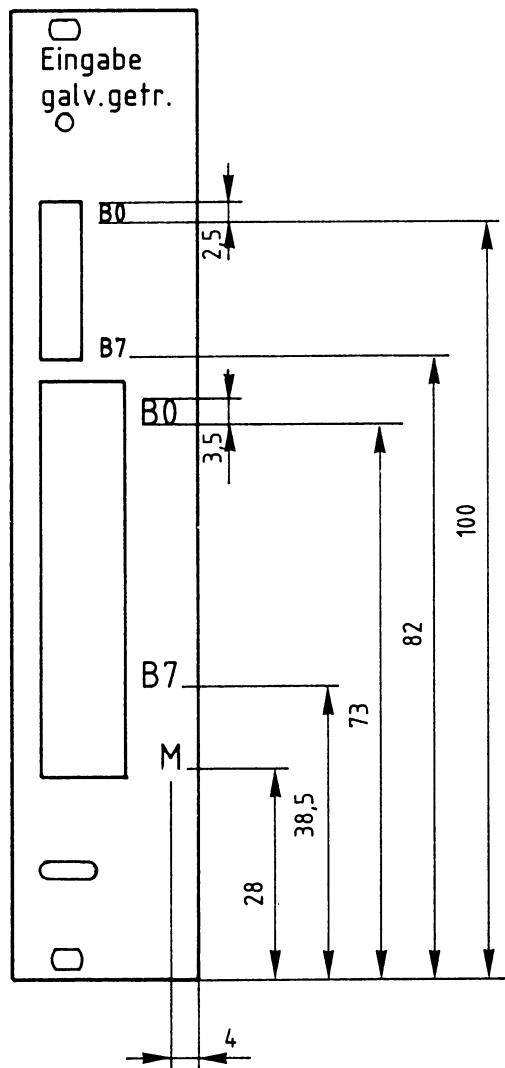

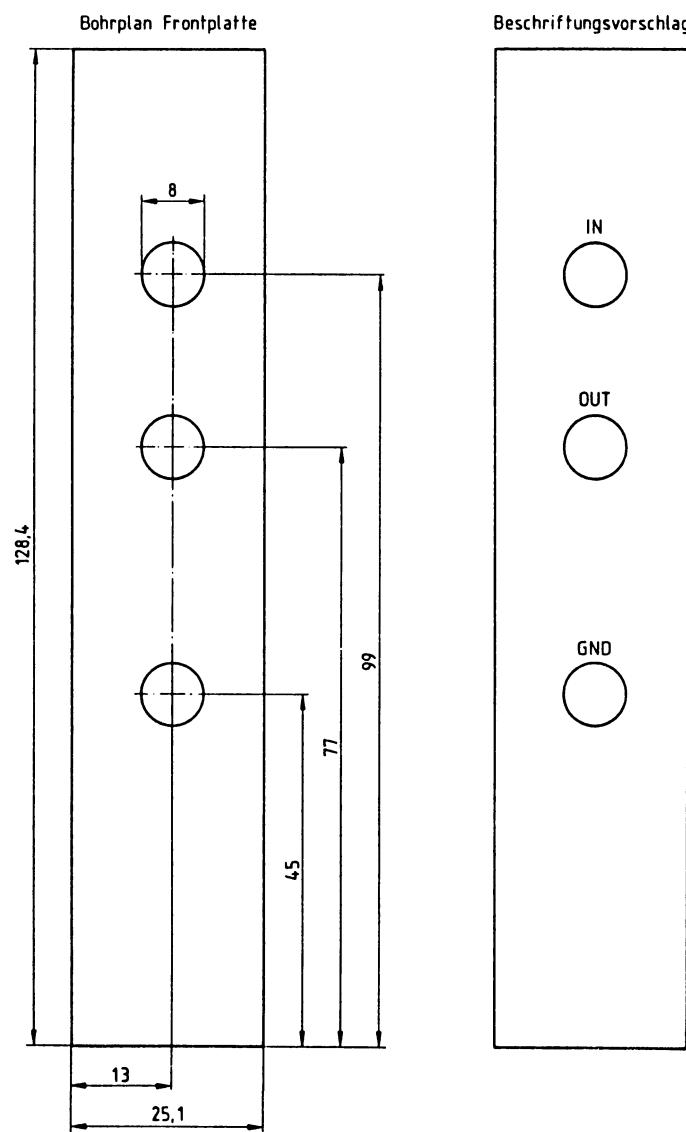

## Bohrplan Frontplatte

## Beschriftungsvorschlag

Material: Frontplatte L-C05

Alu 2mm

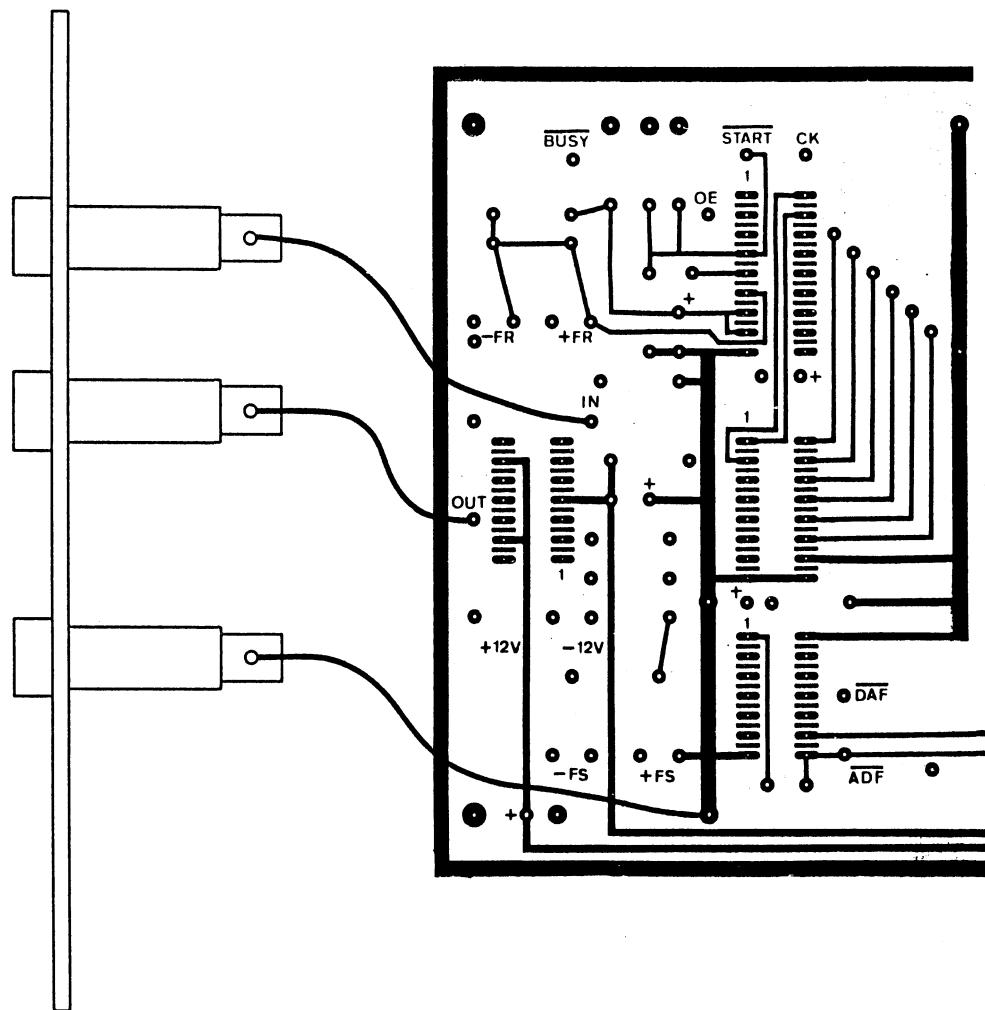

## Zusammenbau Baugruppe

## Stückliste für den Zusammenbau

| Pos. | Stckz. | Benennung/Daten                                   | Bemerkung         |

|------|--------|---------------------------------------------------|-------------------|

| 1    | 1      | Leiterplatte BFZ/MFA 4.8.                         | komplett bestückt |

| 2    | 1      | Griff komplett                                    |                   |

| 3    | 1      | Frontplatte                                       |                   |

| 4    | 1      | Frontverbinder                                    |                   |

| 5    | 1      | Messerleiste 64polig, DIN 41612                   |                   |

| 6    | 1      | Zylinderschraube M2,5x8 DIN 84                    |                   |

| 7    | 1      | Federring B2,5 DIN 127                            |                   |

| 8    | 3      | Zylinderschraube M2,5x12 DIN 84                   |                   |

| 9    | 5      | Federscheibe A2,7 DIN 137                         |                   |

| 10   | 4      | Sechskantmutter M2,5 DIN 439                      |                   |

| 11   | 2      | Zylinderschraube M2,5x10 DIN 84                   |                   |

| 12   | 2      | Zylinderschraube mit Schaft,<br>BM2,5x10/5 DIN 84 |                   |

| 13   | 2      | Schraubensicherung, Kunststoff                    |                   |

# FACHPRAKTISCHE ÜBUNG MIKROCOMPUTER-TECHNIK

8-Bit-Parallel-Ausgabe

(galv. getrennt)

BFZ/MFA 4.9.

---

Inhaltsverzeichnis

---

| Inhalt                                  | Seite |

|-----------------------------------------|-------|

| Hinweise                                | 1     |

| Blockschaltbild                         | 2     |

| Funktionsbeschreibung                   | 3     |

| Hinweise zum Anschluß von Lasten        | 4     |

| Technische Daten                        | 5     |

| Stromlaufplan                           | 6     |

| Bestückung Leiterplatte                 | 7     |

| Bereitstellungsliste zur Inbetriebnahme | 10    |

| Inbetriebnahme                          | 11    |

| Bereitstellungsliste                    | 14    |

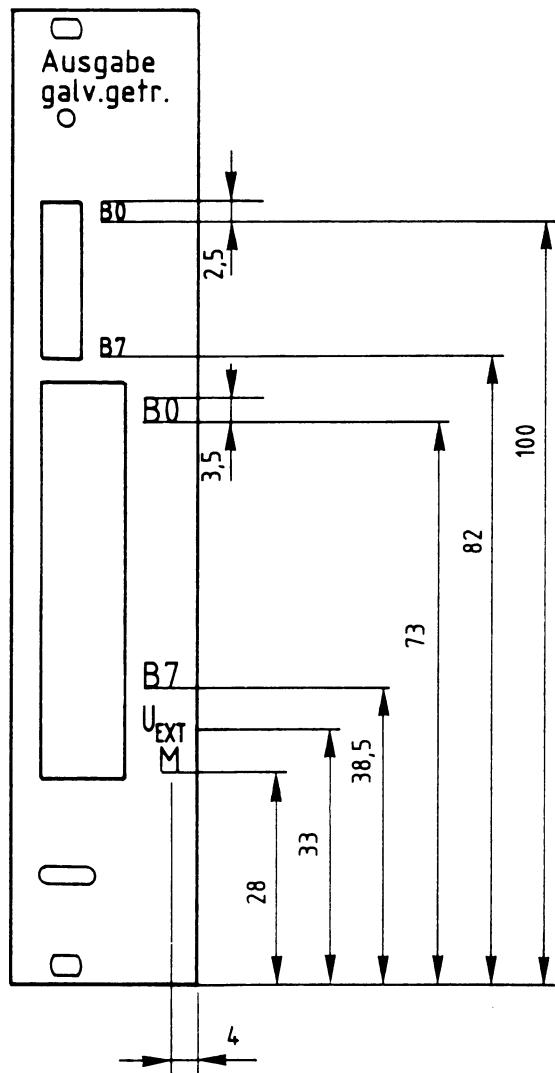

| Bohrplan Leiterplatte                   | 17    |

| Layout Bestückungsseite                 | 18    |

| Bohrplan Frontplatte                    | 19    |

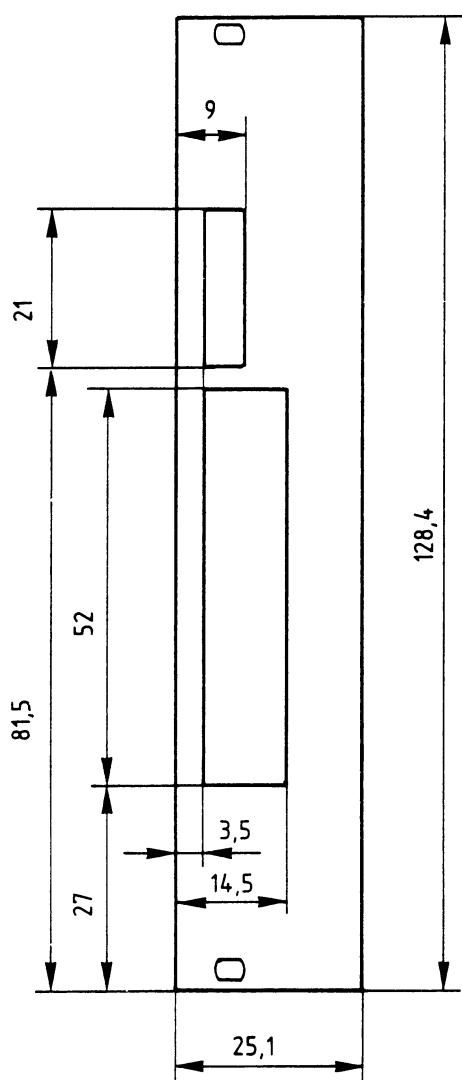

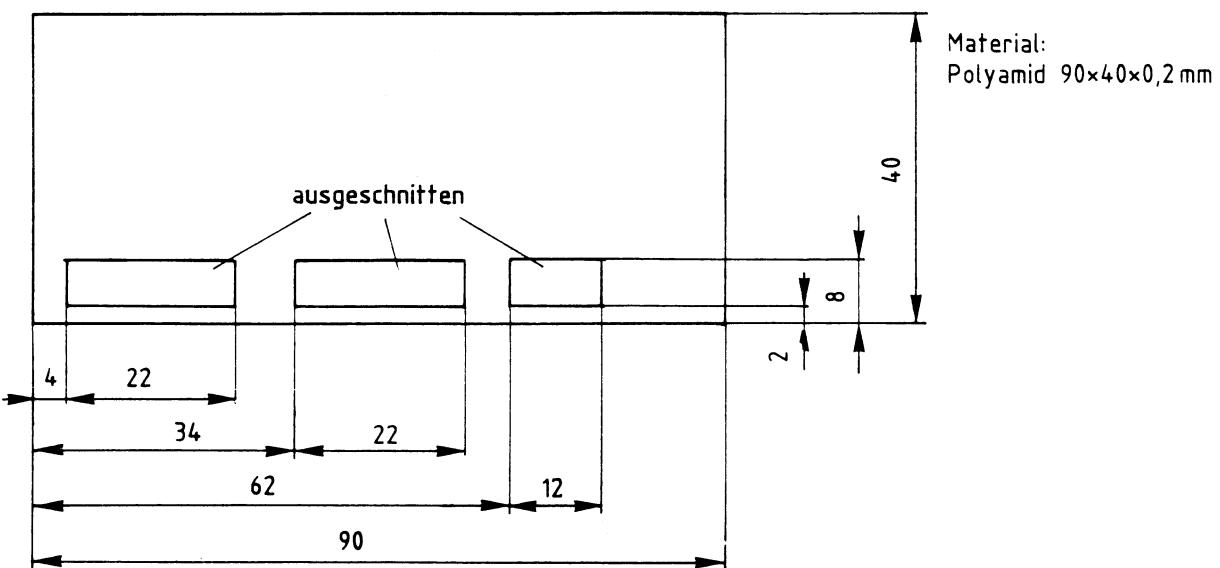

| Fertigung Kühlkörper                    | 20    |

| Zusammenbau Baugruppe                   | 21    |

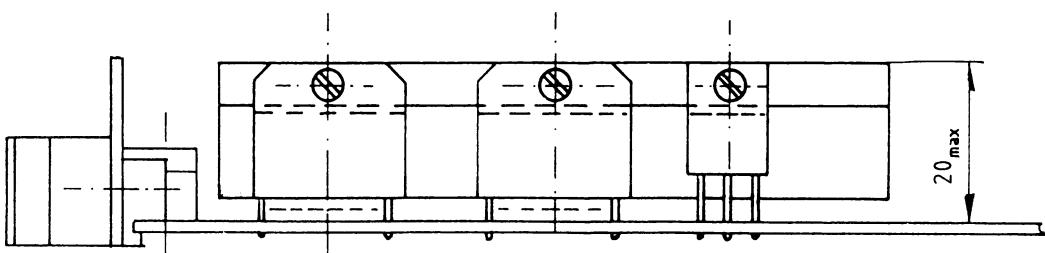

**Hinweise**

Die 8-Bit-Parallel-Ausgabe-Baugruppe mit galvanisch getrennten Ausgängen ist für die Ansteuerung von Gleichstrommotoren, Relais, Lampen und Wegeventilen durch den BFZ/MFA-Mikrocomputer vorgesehen.

Die extern an die Baugruppe anzuschließende Lastspannung kann Werte zwischen 7 V und 24 V besitzen (Gleichspannung). Der maximale Ausgangsstrom ist abhängig von der Anzahl der benutzten Ausgänge und liegt zwischen 0,5 A und 1 A (siehe "Technische Daten").

Alle Ausgänge sind Gegentaktausgänge, wodurch auch Brückenschaltungen z.B. zur Ansteuerung von Gleichstrommotoren mit Richtungsumkehr und Bremsbetrieb möglich werden. Außerdem können die Ausgänge im Taktbetrieb mit einstellbarem Impuls/Pausen-Verhältnis betrieben werden, wodurch sich unterschiedlich hohe Ausgangsspannungen bei nur einer externen Lastspannung erzielen lassen.

Die Baugruppe ist aufgrund ihrer technischen Daten auch für den Einsatz in SPS-Steuerungen geeignet. Der hierzu erforderliche SPS-Interpreter ist Bestandteil der "Software-Erweiterung SP 1" zum BFZ/MFA-Mikrocomputer. Er ist im Band "Fachtheoretische Übungen" beschrieben.

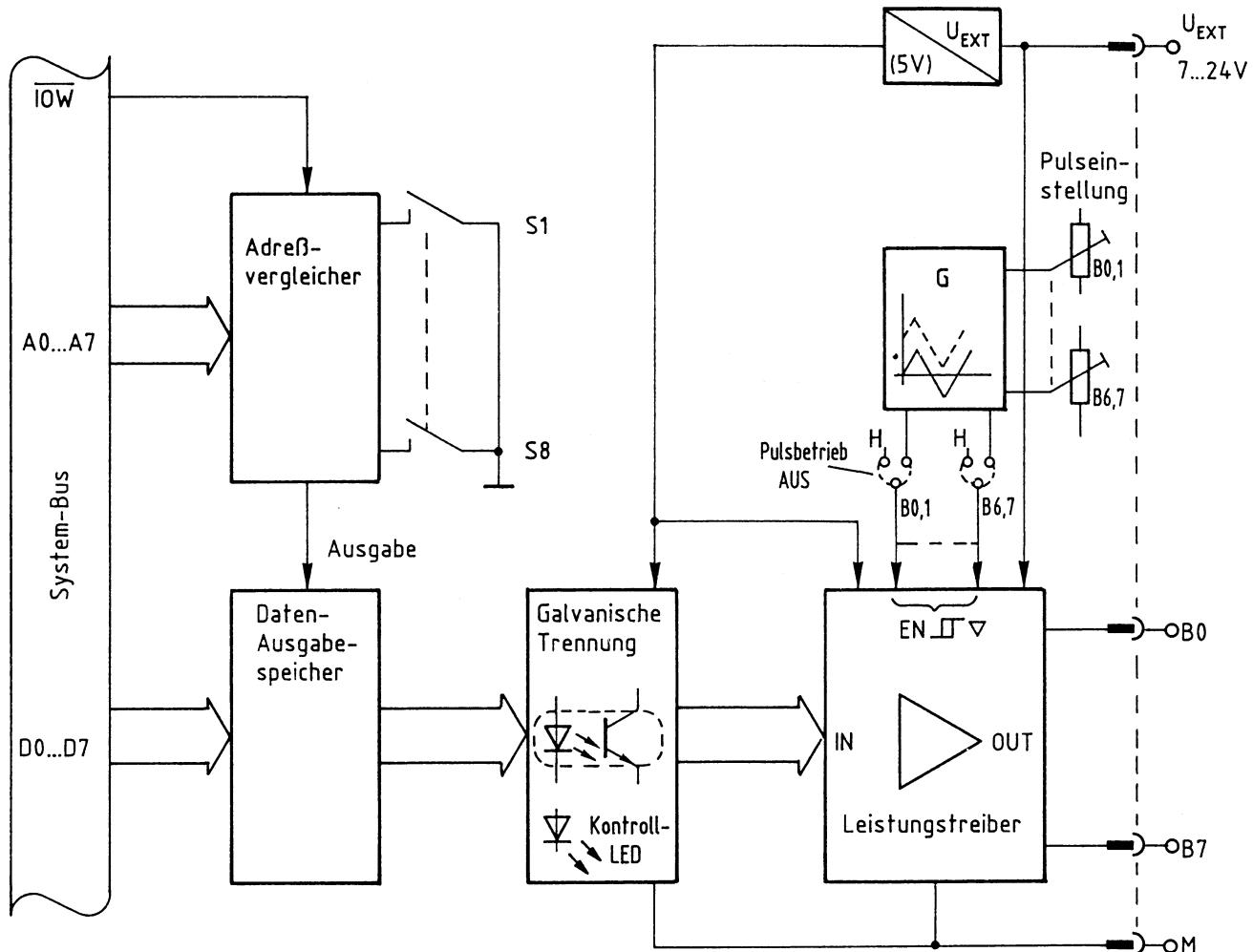

## Blockschaltbild

---

## Funktionsbeschreibung

---

Die Funktionsbeschreibung bezieht sich nur auf das Blockschaltbild und ist für den Ausbilder gedacht. Schaltungseinzelheiten werden nicht behandelt.

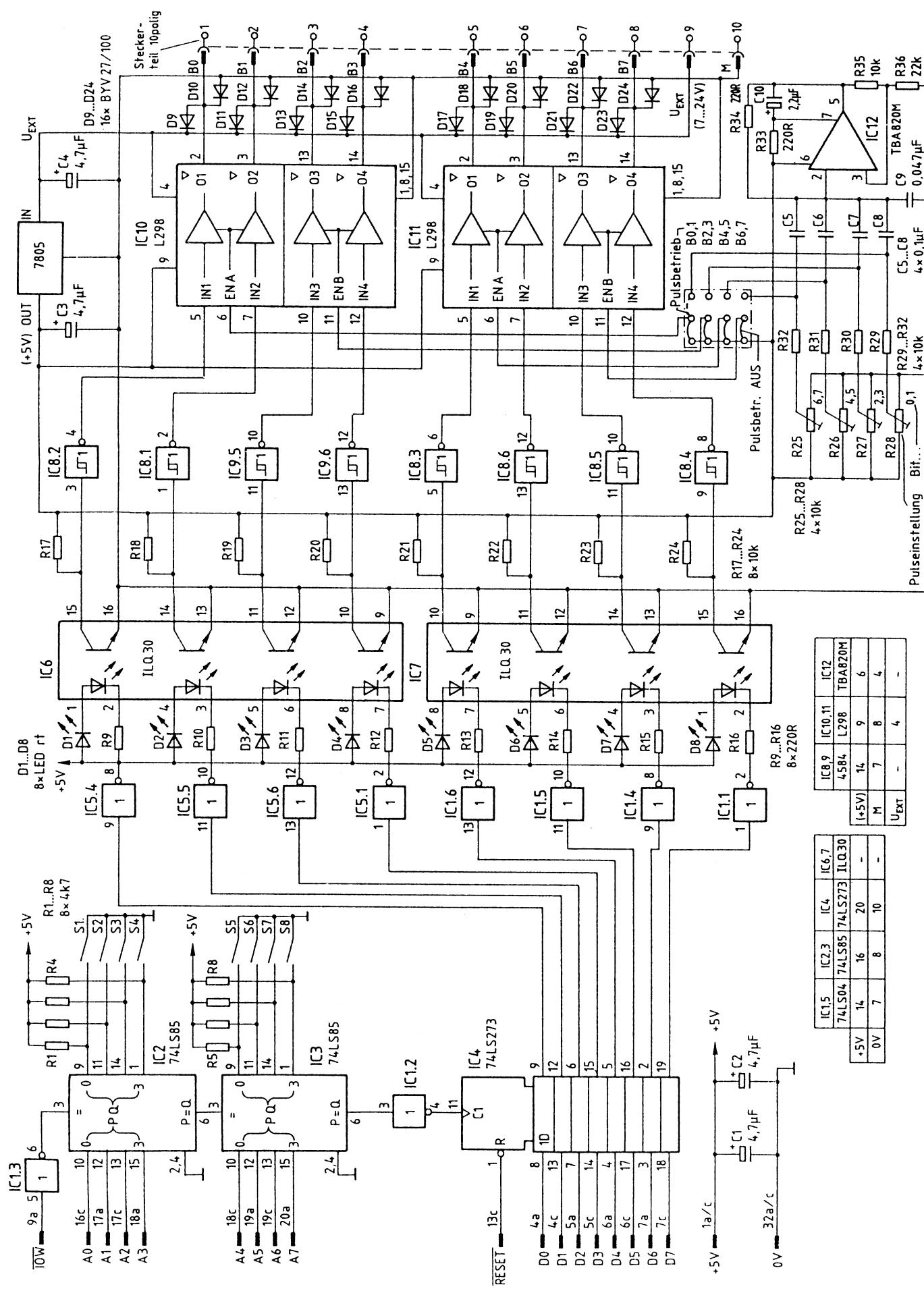

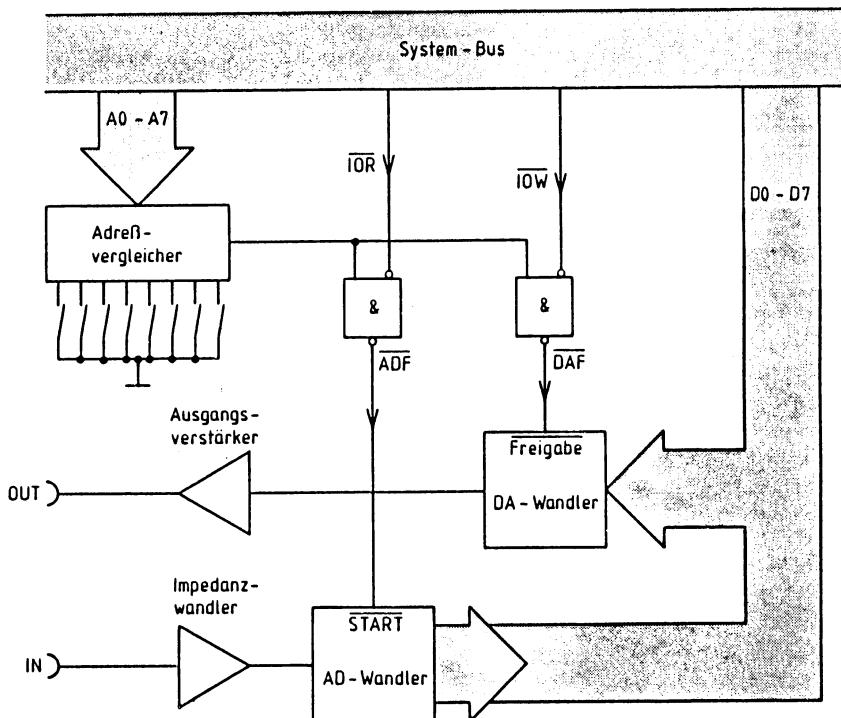

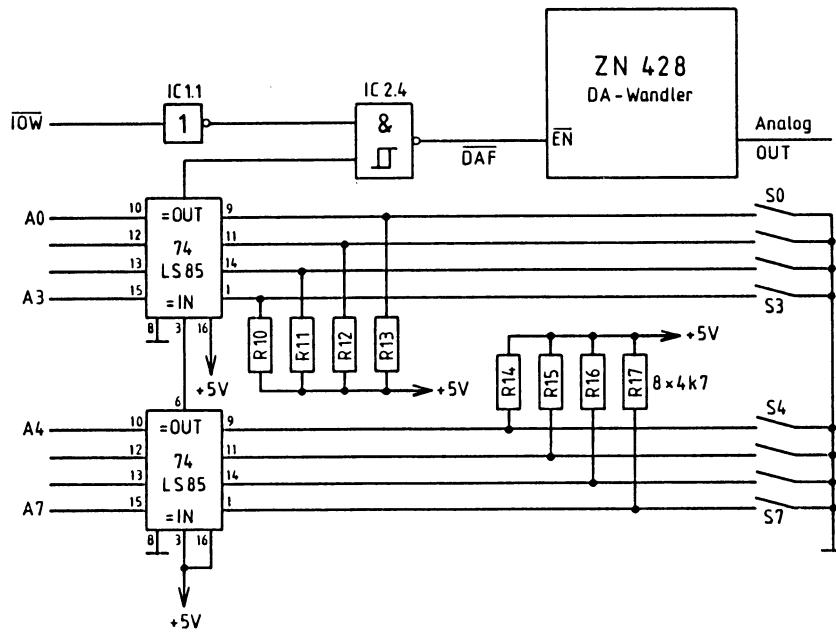

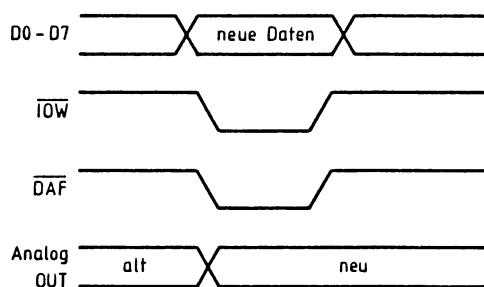

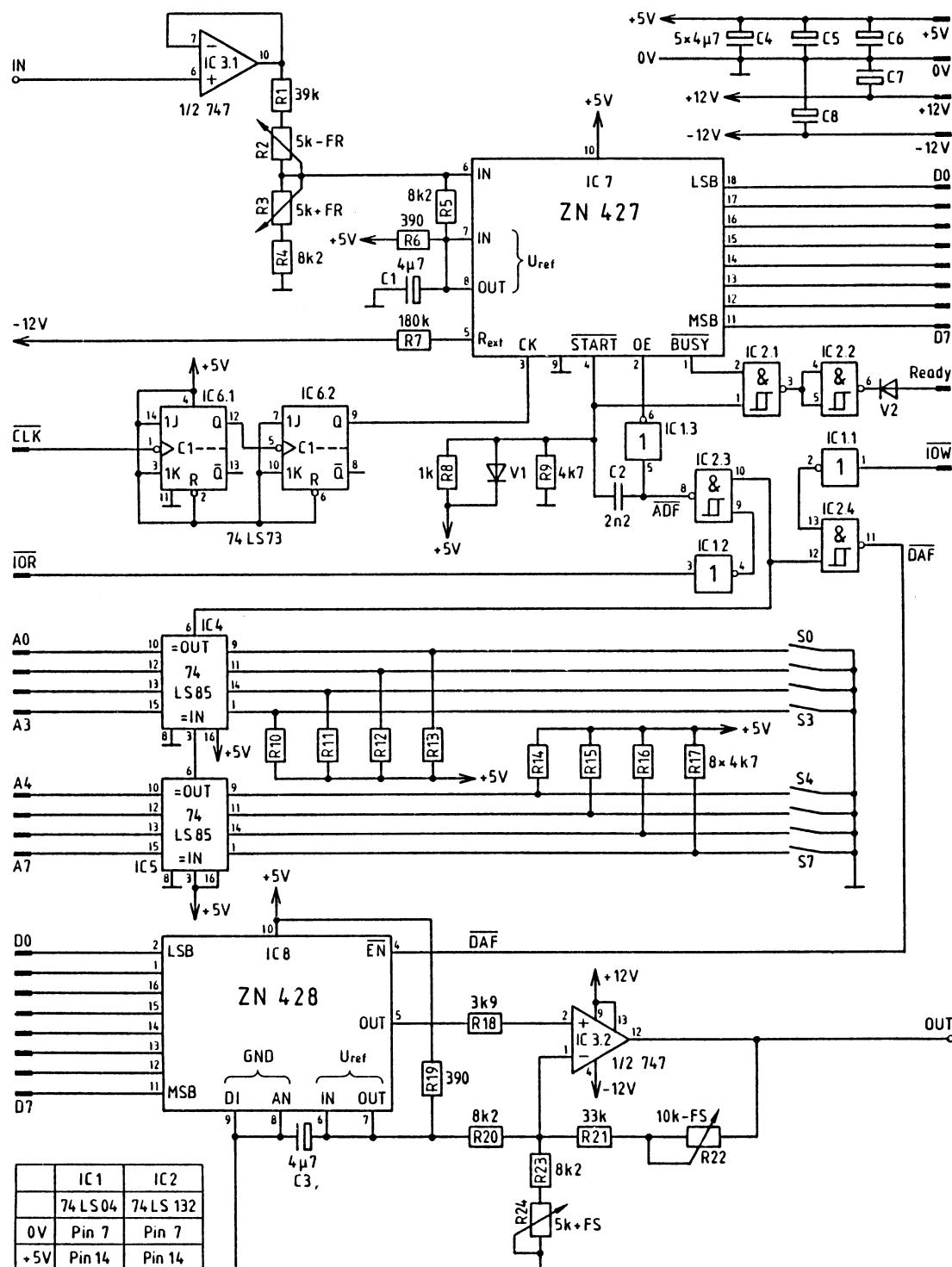

Die von der CPU an die Peripherie auszugebenden Daten gelangen über den Daten-Bus in den Daten-Ausgabespeicher, wenn der Adreßvergleicher vom Adreß-Bus die richtige Adresse erhält und außerdem das Steuersignal  $\overline{IOW}$  aktiv ist.

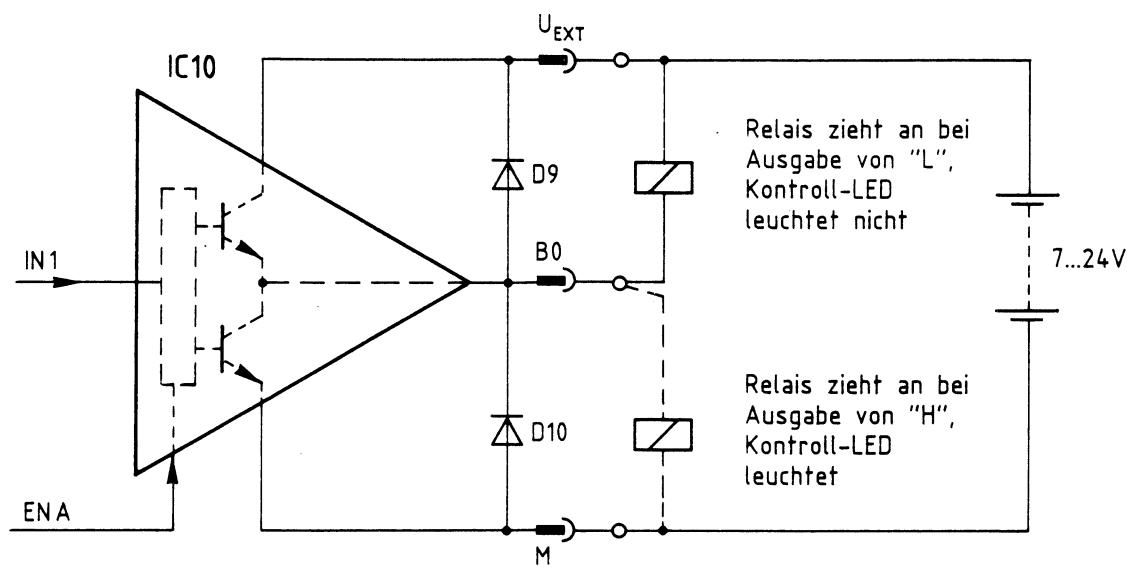

Jedes Bit steuert einen Optokoppler zur galvanischen Trennung von Steuer- und Lastkreis an und außerdem eine Kontroll-LED, die bei H-Pegel leuchtet.

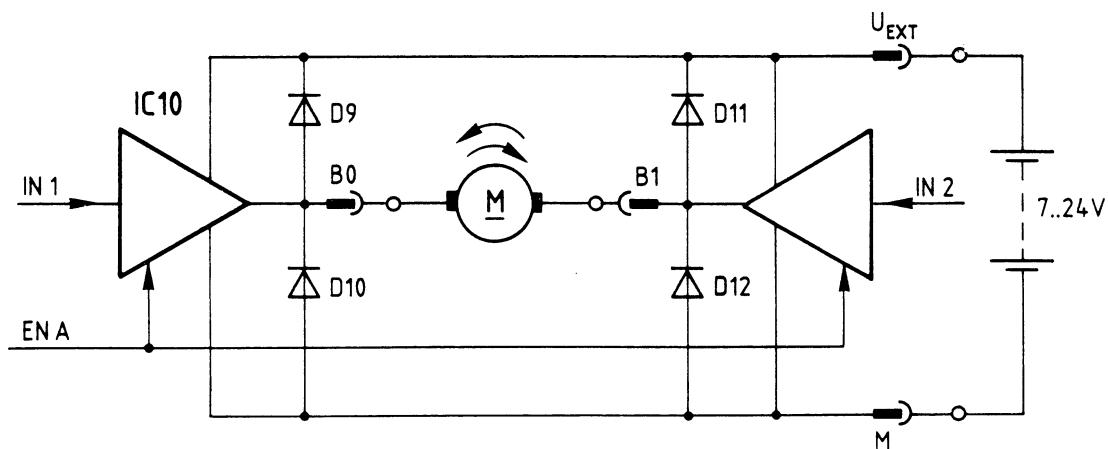

Die Fototransistoren der Optokoppler steuern die IN-Eingänge eines 8fach-Leistungstreibers an, dessen Ausgänge B0 bis B7 auf die Frontplatte der Baugruppe geführt sind. Die Lastspannung  $U_{EXT}$  (7 V bis 24 V) wird dem Leistungstreiber von außen zugeführt. Die erforderliche Spannungsquelle muß für den Laststrom aller angeschlossenen Verbraucher ausgelegt sein. Aus  $U_{EXT}$  wird außerdem eine 5-V-Versorgungsspannung gebildet, die gegenüber der 5-V-Versorgungsspannung des Mikrocomputers galvanisch getrennt ist.

Die Steuerung der Leistungstreiber erfolgt über Enable-Eingänge mit Schmitt-Trigger-Eigenschaften. Für jeweils zwei Bit des 8fach-Leistungstreibers (B0/B1, B2/B3, B3/B4, B5/B6) ist ein gemeinsamer Enable-Eingang vorhanden. Bei H-Pegel an den Enable-Eingängen arbeiten die Leistungstreiber, bei L-Pegel sind sie gesperrt (hochohmig).

Mit Hilfe von Steckbrücken können die Enable-Eingänge entweder auf H-Pegel ("Pulsbetrieb AUS") oder auf die Ausgänge eines Dreieckgenerators geschaltet werden ("Pulsbetrieb"). Da der Gleichspannungsanteil der Dreieckspannung mit Hilfe von Trimmerwiderständen veränderbar ist, erhalten die Enable-Eingänge im Pulsbetrieb nicht ständig H-Pegel, sondern nur in den Zeitabschnitten, in denen die Dreieckspannung Werte oberhalb der Schaltschwellen der Enable-Eingänge (Schmitt-Trigger) besitzt. Hierdurch wird die Ausgangsspannung bzw. der Ausgangsstrom der jeweiligen Ausgänge gepulst, was einer Mittelwertveränderung entspricht.

Die Höhe der Ausgangsspannung kann auf diese Weise jeweils für 2 Bit zwischen 0 und ca. 100% von  $U_{EXT}$  verändert werden, ohne die Spannung  $U_{EXT}$  selbst zu verändern. Es ist möglich, einige Ausgänge gepulst und andere statisch zu betreiben.

## Hinweise zum Anschluß von Lasten

Lastwiderstände (z.B. Lampen, Relais) können von einem Ausgang (z.B. B0) entweder gegen  $U_{EXT}$  oder gegen den Anschluß M angeschlossen werden. Die für induktive Lasten erforderlichen Freilaufdioden sind in der Ausgabe-Baugruppe bereits vorhanden (siehe auch im Stromlaufplan).

Gleichstrommotoren (max. 1 A im Dauerbetrieb) können in Brückenschaltung an zwei Bit (z.B. B0 und B1) angeschlossen werden. Bei H-Pegel an IN1 und L-Pegel an IN2 läuft der Motor in die eine, bei umgekehrten Pegeln in die andere Richtung. Führen IN1 und IN2 beide gleiche Pegel, wird der Motor kurzgeschlossen (Bremsbetrieb).

---

Technische Daten

---

- \* Acht Ausgänge, galvanisch getrennt (Optokoppler) mit gemeinsamem Bezugspotential

- \* Externe Versorgungsspannung: 7 V bis 24 V (Gleichspannung)

- \* Ausgangstrom: Abhängig von der Anzahl der benutzten Ausgänge

Die Ausgänge sind in die beiden Gruppen B0 bis B3 und B4 bis B7 eingeteilt.

Für jede Gruppe gilt:

- $I_{max} = 0,5 \text{ A}/\text{Bit}$ , wenn alle vier Ausgänge der Gruppe im Einzelbitbetrieb benutzt werden

- $I_{max} = 1 \text{ A}$  für 1 Bit und zusätzlich  $0,5 \text{ A}$  für ein weiteres Bit der Gruppe (Einzelbitbetrieb, 2 Bit der Gruppe unbeschaltet)

- $I_{max} = 1 \text{ A}$ , wenn zwei Bit einer Gruppe (B0/B1 oder B2/B3 bzw. B4/B5 oder B6/B7) in Vollbrückenschaltung betrieben werden und die anderen beiden Bit der Gruppe freibleiben

- \* Gegentaktausgänge ermöglichen ...

- Einzelbitausgabe (z.B. Relaisansteuerung)

- Ansteuerung von Gleichstrommotoren mit Richtungsumkehr und Bremsbetrieb

- \* Impulsbetrieb der Ausgänge mit einstellbarem Impuls/Pausen-Verhältnis zur Veränderung von Gleichstrom-Mittelwerten möglich

- \* Ausgangssignalanzeige für jedes Bit durch LED

- \* Einstellbare Portadresse

- \* Anwendungsbeispiele: Ansteuerung von Relais, Lampen, Schrittmotoren, Modell-Motoren, Wegeventilen usw. mit eigener Versorgungsspannung

## Stromlaufplan

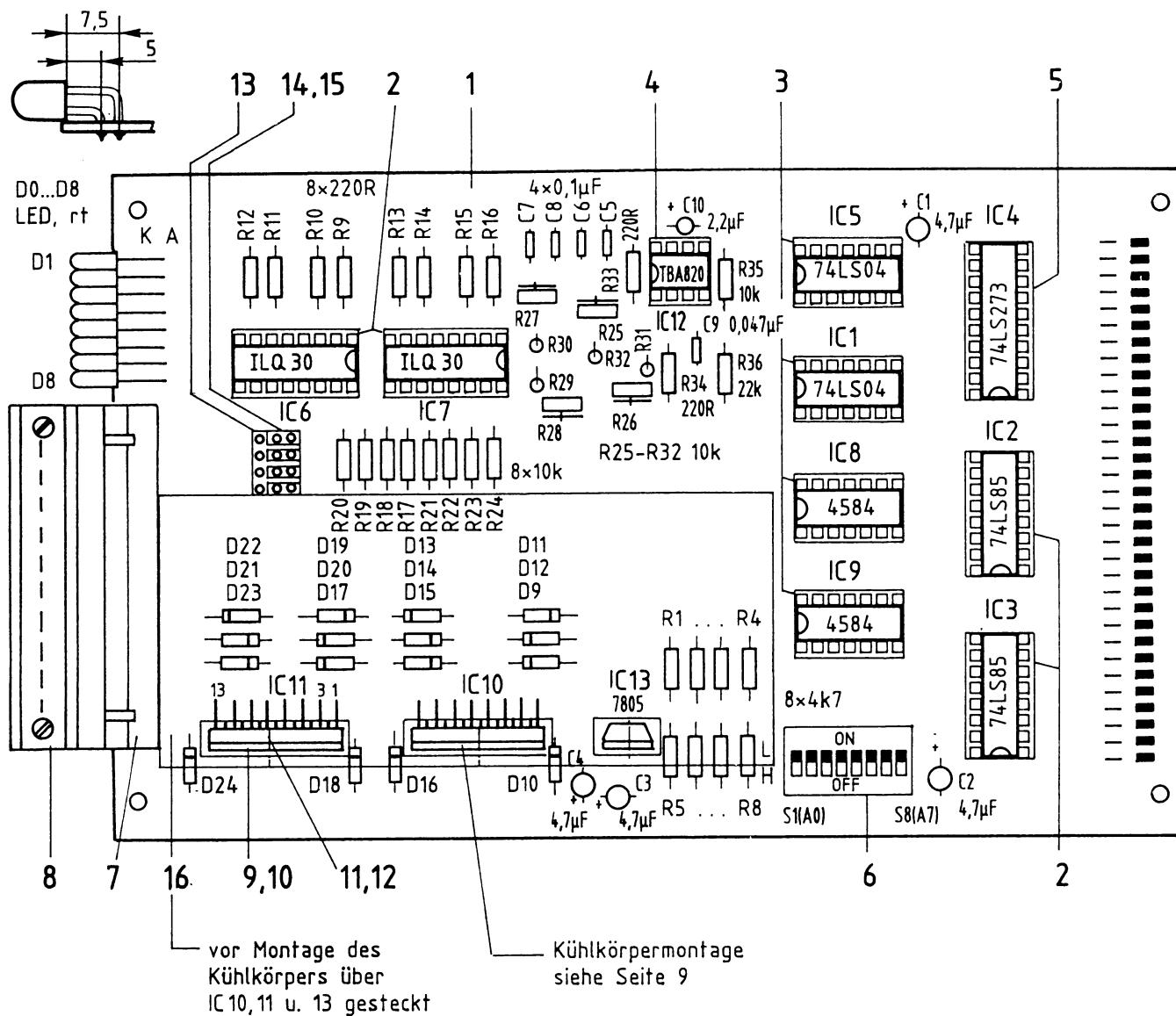

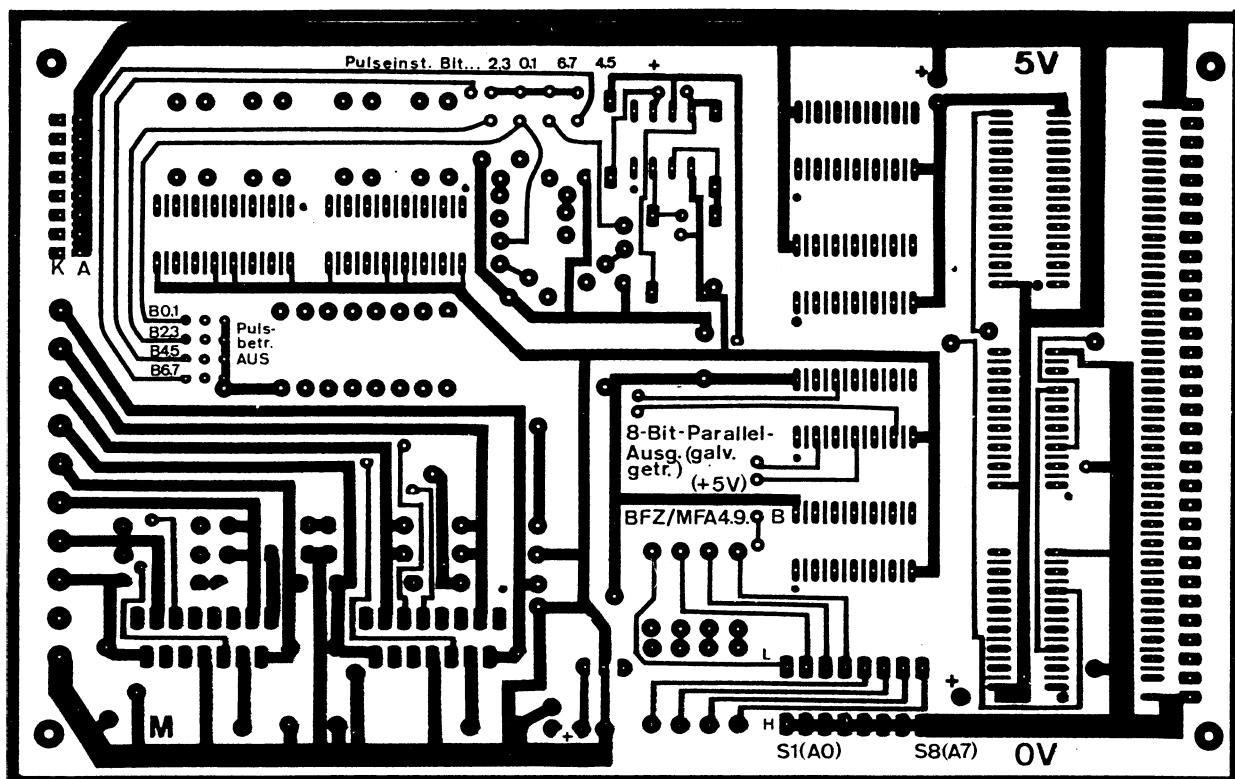

## Bestückung Leiterplatte

Stückliste Leiterplatte BFZ/MFA 4.9.

| Pos. | Stckz. | Benennung/Daten                | Bemerkung |

|------|--------|--------------------------------|-----------|

| 1    | 1      | Leiterplatte BFZ/MFA 4.9.      |           |

| 2    | 4      | IC-Fassung 16polig             |           |

| 3    | 4      | IC-Fassung 14polig             |           |

| 4    | 1      | IC-Fassung 8polig              |           |

| 5    | 1      | IC-Fassung 20polig             |           |

| 6    | 1      | Miniaturschiebeschalter 8polig |           |

| 7    | 1      | Grundgehäuse 10polig           |           |

| 8    | 1      | Steckerteil 10polig            |           |

## Bestückung Leiterplatte

| Pos. | Stckz. | Benennung/Daten                | Bemerkung                                                     |

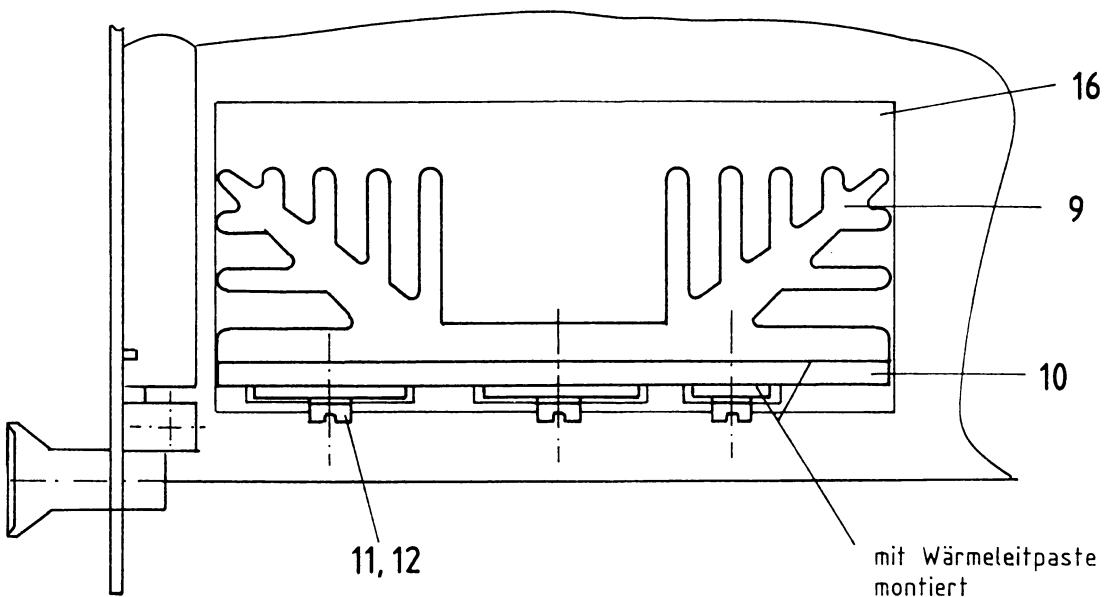

|------|--------|--------------------------------|---------------------------------------------------------------|

| 9    | 1      | Kühlkörper                     | mit Wärmeleitpaste mont.                                      |

| 10   | 1      | Wärmeleitblech                 | mit Wärmeleitpaste mont.                                      |

| 11   | 3      | Federscheibe A3,2 DIN 137      |                                                               |

| 12   | 3      | Zylinderschraube M3x10 DIN 84  |                                                               |

| 13   | 1      | Stiftleiste einreihig, 4polig  |                                                               |

| 14   | 1      | Stiftleiste zweireihig, 4polig |                                                               |

| 15   | 4      | Kurzschlußbrücke RM 2,54       |                                                               |

| 16   | 1      | Isolierplatte Polyamid         | vor Montage des Kühlkörpers über IC10, IC11 und IC13 gesteckt |

## Bauteilliste Leiterplatte BFZ/MFA 4.9.

| Kennz.    | Benennung/Daten                 | Bemerkung                               |

|-----------|---------------------------------|-----------------------------------------|

| R1...R8   | Widerstand 4,7 k                | Alle Widerstände<br><u>±5%</u> , 0,25 W |

| R9...R16  | Widerstand 220                  |                                         |

| R17...R24 | Widerstand 10 k                 |                                         |

| R25...R28 | Trimmerwiderstand 10 k /0,1 W   | stehend, RM 5 x 2,5                     |

| R29...R32 | Widerstand 10 k                 |                                         |

| R33, R34  | Widerstand 220                  |                                         |

| R35       | Widerstand 10 k                 |                                         |

| R36       | Widerstand 22 k                 |                                         |

| C1...C4   | Tantal-Elko 4,7 F/35 V          | Tropfenform                             |

| C5...C8   | Keramikkondensator 0,1 F/50 V   |                                         |

| C9        | Keramikkondensator 0,047 F/50 V | RM 5                                    |

| C10       | Tantal-Elko 2,2 F/35 V          | Tropfenform                             |

## Bestückung Leiterplatte

| Kennz.     | Benennung/Daten                   | Bemerkung            |

|------------|-----------------------------------|----------------------|

| IC1, IC5   | Sechs Inverter 74 LS 04           |                      |

| IC2, IC3   | 4-Bit-Vergleicher 74 LS 85        |                      |

| IC4        | 8-Bit-D-Flipflop 74 LS 273        |                      |

| IC6, IC7   | 4-fach Optokoppler ILQ 30         | oder ILQ 74          |

| IC8, IC9   | 6 Inv. Schmitt-Trigger 4584       | oder 74 C 14         |

| IC10, IC11 | Zweifach-Voll-Brückentreiber L298 |                      |

| IC12       | NF-Verstärker TBA 820M            |                      |

| IC13       | Positiv-Festspannungsregler 7805  | 5 V/1 A, TO 220      |

| D1...D8    | LED, rot, anreihbar               | abgewinkelt montiert |

| D9...D24   | Si-Diode BYV 27/100               |                      |

Montage des Kühlkörpers:

Bereitstellungsliste zur Inbetriebnahme

Zur Inbetriebnahme bzw. Prüfung der Baugruppe "8-Bit-Parallel-Ausgabe (galv. getrennt)" wird folgendes Material benötigt:

| Stckz. | Benennung/Daten                                                  | Bemerkung                                              |

|--------|------------------------------------------------------------------|--------------------------------------------------------|

| 1      | Baugruppenträger mit Busverdrahtung<br>BFZ/MFA 0.1.              | Alle Baugruppen<br>komplett aufge-<br>baut und geprüft |

| 1      | Bus-Abschluß BFZ/MFA 0.2.                                        |                                                        |

| 1      | Trafo-Einschub BFZ/MFA 1.1.                                      |                                                        |

| 1      | Spannungsregelung BFZ/MFA 1.2.                                   |                                                        |

| 1      | Bus-Signalgeber BFZ/MFA 5.1.                                     |                                                        |

| 1      | Bus-Signalanzeige BFZ/MFA 5.2.                                   |                                                        |

| 1      | Prozessor 8085 BFZ/MFA 2.1.                                      |                                                        |

| 1      | Adapterkarte 64polig BFZ/MFA 5.3.                                |                                                        |

| 1      | Gleichspannungs-Netzgerät, Spannung<br>einstellbar 0...15 V, 1 A |                                                        |

| 2      | Vielfachmeßinstrument                                            | mögl. Digital-Multimeter                               |

| 1      | Drahtwiderstand 10Ω /10 W                                        | Lastwiderstand                                         |

---

## Inbetriebnahme

---

### 1. Sichtkontrolle

Die Sichtkontrolle wird anhand von Stromlauf- und Bestückungsplan sowie Stück- und Bauteilliste durchgeführt.

- Sind alle Lötstellen ordnungsgemäß verlötet?

- Sind alle Elektrolytkondensatoren richtig gepolt?

- Sind alle ICs richtig eingesteckt?

- Sind alle Schrauben festgezogen?

### 2. Funktionsprüfung

#### 2.1. Reset-Steuerung, Adreßvergleicher und Datenübernahme

- DIL-Schalter S1 bis S8 der 8-Bit-Parallel-Ausgabe (galv. getrennt) in Stellung "ON" geschaltet (Port-Adresse 00)

- Baugruppe "8-Bit-Parallel-Ausgabe (galv. getrennt)" über 64polige Adapterkarte in den Baugruppenträger eingesteckt, alle Ausgänge frei

Nach dem Einschalten der Betriebsspannung leuchten i.A. einige der Kontroll-LEDs auf.

- Baugruppe "Prozessor 8085" (BFZ/MFA 2.1.) zusätzlich eingesteckt

Nach dem Einschalten der Betriebsspannung leuchtet jetzt keine Kontroll-LED, da das RESET-Signal der CPU-Baugruppe den Daten-Ausgabespeicher löscht.

- Bus-Signalgeber in den Baugruppenträger eingesteckt, Einstellungen:

Schalter "ON/OFF" in Stellung "ON", ADDRESS = 0000, DATA = 55

Bus-Signalanzeige eingesteckt (beliebige Stellung der Schalter)

## Inbetriebnahme

- Messung des logischen Pegels an Pin 11 von IC4 (74 LS 273) gegen 0 V, Beobachtung der Kontroll-LEDs auf der 8-Bit-Parallel-Ausgabe (galv. getrennt):

1. Nach dem Einschalten leuchtet keine Kontroll-LED (RESET)

2. Keine Steuertaste des Bus-Signalgebers betätigt: H-Pegel an Pin 11 von IC4

2. Steuertaste "IOW" des Bus-Signalgebers betätigt: L-Pegel an Pin 11 von IC4, nach dem Loslassen der IOW-Taste Anzeige des Datenwertes 55 durch die Kontroll-LEDs

- Ausgabe der Datenwerte AA, FF und 00 an die Ausgabe-Baugruppe und Kontrolle, ob die entsprechenden Kontroll-LEDs aufleuchten

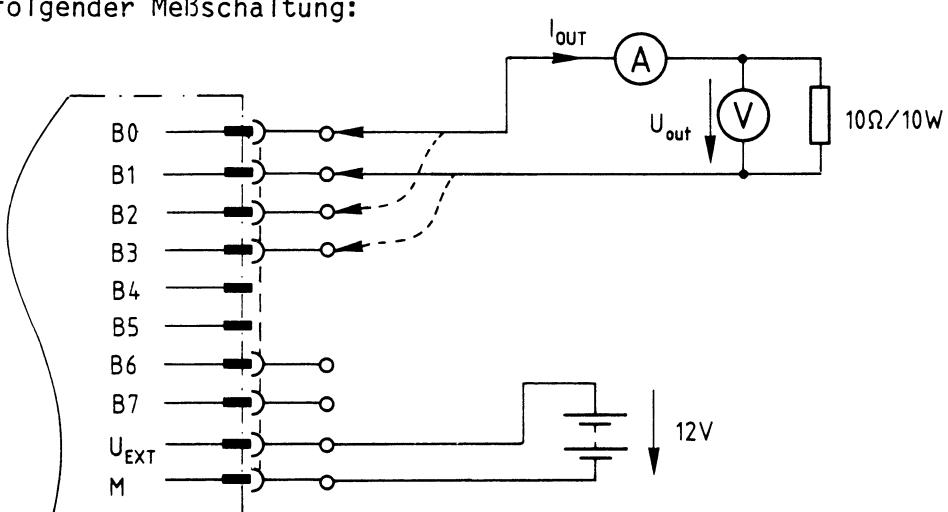

**2.3. Prüfen der Leistungstreiber im statischen Betrieb**

- Alle 4 Steckbrücken (zur Umschaltung der Leistungstreiber auf Impulsbetrieb) in Stellung "Pulsbetrieb AUS"

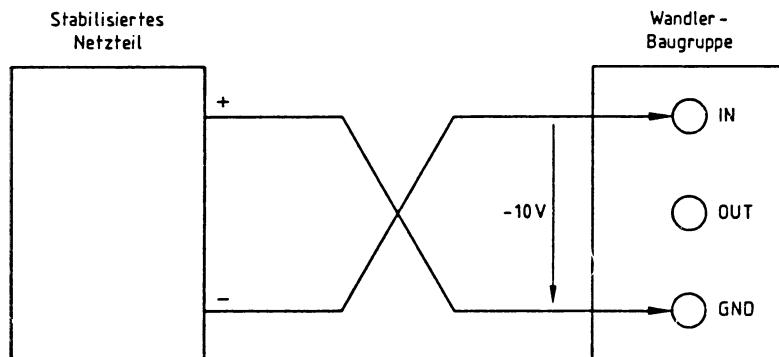

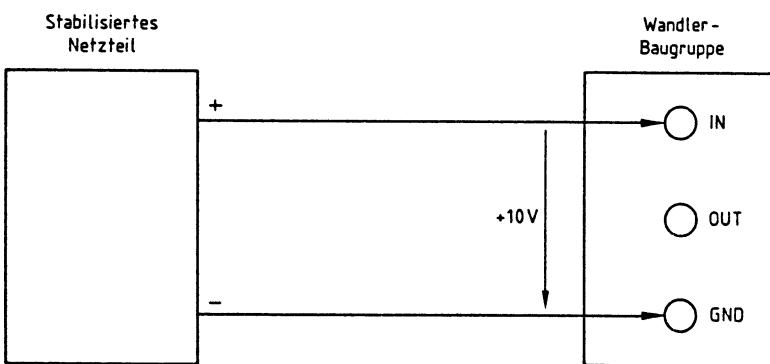

- Anschluß eines Gleichspannungsnetzgerätes (12 V, 1 A) an die Anschlüsse  $U_{EXT}$  (Pluspol) und M (Minuspol) der Ausgabe-Baugruppe

- Kontrolle der galvanisch vom System-Bus getrennten Spannung "(5 V)": Spannung zwischen Ausgang des 5-V-Spannungsreglers und Anschluß M gemessen, Sollwert zwischen 4,75 V und 5,25 V

- Aufbau folgender Meßschaltung:

---

Inbetriebnahme

---

- Ausgabe des Datenwertes 55 (Bus-Signalgeber, IOW); Messung des Ausgangsstromes  $I_{OUT}$  und der Ausgangsspannung  $U_{OUT}$  für B0 und B1. Zu erwartende Werte:  $U_{OUT}$  ca. 9,5 V,  $I_{OUT}$  ca. 0,9 A

- Ausgabe des Datenwertes 00; zu erwartende Meßwerte:  $U_{OUT}$  kleiner 0,1 V,  $I_{OUT}$  kleiner 1 mA (evtl. andere Polarität)

- Ausgabe des Datenwertes AA; zu erwartende Meßwerte:  $U_{OUT}$  ca. 9,5 V,  $I_{OUT}$  ca. 0,9 A (andere Polarität als bei der ersten Messung)

- Anschluß der Meßschaltung an B2 und B3 und Wiederholung der Messungen; ebenso mit B4 und B5 sowie B6 und B7

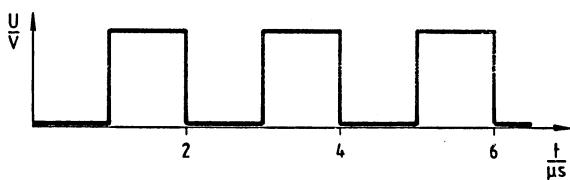

#### 2.4. Prüfen der Leistungstreiber im Pulsbetrieb

- Alle 4 Steckbrücken (zur Umschaltung der Leistungstreiber auf Impulsbetrieb) in Stellung "Pulsbetrieb EIN"; alle 4 Trimmerwiderstände zur Impulseinstellung in Mittelstellung

- Anschluß der Meßschaltung an B0 und B1 und Ausgabe des Datenwertes 55

- Einstellbereich der Ausgangsspannung zwischen 0 V und ca. 10 V überprüfen (Trimmerwiderstand "Bit 0,1"); Spannung anschließend auf 5 V einstellen

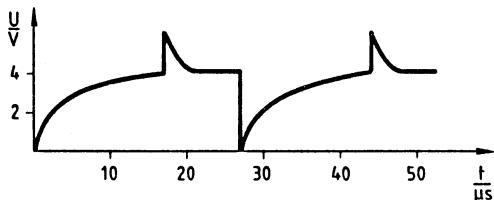

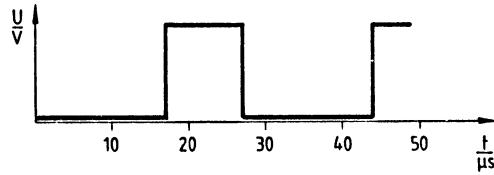

Die mit dem Trimmerwiderstand eingestellte Spannung ist eine Rechteckspannung mit einem Spitzenwert von ca. 10 V. Das Impuls/Pausen-Verhältnis ist einstellbar und beträgt bei  $U_{OUT} = 5$  V ca. 1.

- Wiederholung der Messungen/Einstellungen bei Anschluß der Meßschaltung an B2 und B3, B4 und B5 sowie B6 und B7

- Anschließend sollen die Steckbrücken wieder in Position "Pulsbetrieb AUS" gesteckt werden.

Damit ist die Inbetriebnahme beendet.

## Bereitstellungsliste

| Stckz. | Benennung/Daten                                                                                     | Bemerkung                                                                                       |

|--------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| 1      | Leiterplatte, BFZ/MFA 4.9                                                                           |                                                                                                 |

| 1      | Frontplatte, Teilung L-C 05<br>Alu, 2 mm dick, Breite: 25,1 mm                                      | z.B. Intermas<br>Nr. 409-017 665                                                                |

| 1      | Griff komplett mit Abdeckung T03                                                                    | z.B. Intermas<br>Nr. 409-017 927                                                                |

| 1      | Frontverbinder 1,6 FEE                                                                              | z.B. Intermas<br>Nr. 409-024 830                                                                |

| 1      | Messerleiste 64polig, DIN 41612                                                                     | z.B. Erni STV-P-364 a/c<br>Nr. 9722.333.401                                                     |

| 1      | Combicon-Grundgehäuse 10polig, Einbauraster 5,08 mm, 90°-abgewinkelte Montage, ohne seitliche Wände | Phoenix-Contact<br>Typ MSTB 1,5/10-G-5,08<br>Best. Nr. 175 9091<br>(Postf. 1341, 4933 Blomberg) |

| 1      | Combicon-Steckerteil 10polig, Draht einföhrung in Steckrichtung                                     | Phoenix-Contact<br>Typ MSTB 1,5/10-ST-5,08<br>Best. Nr. 175 7093                                |

| 3      | Zylinderschraube M3x10 DIN 84                                                                       |                                                                                                 |

| 1      | Zylinderschraube M2,5x8 DIN 84                                                                      |                                                                                                 |

| 2      | Zylinderschraube M2,5x10 DIN 84                                                                     |                                                                                                 |

| 3      | Zylinderschraube M2,5x12 DIN 84                                                                     |                                                                                                 |

| 2      | Zylinderschraube mit Schaft<br>BM2,5x10/5 DIN 84                                                    |                                                                                                 |

| 3      | Federscheibe A3,2 DIN 137                                                                           |                                                                                                 |

| 5      | Federscheibe A2,7 DIN 137                                                                           |                                                                                                 |

| 1      | Federring B2,5 DIN 127                                                                              |                                                                                                 |

| 4      | Sechskantmutter M2,5 DIN 439                                                                        |                                                                                                 |

## Bereitstellungsliste

| Stckz. | Benennung/Daten                                                                                                                                      | Bemerkung                                                        |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| 2      | Schraubensicherung, Kunststoff                                                                                                                       | z.B. Intermas<br>Nr. 409-026 748                                 |

| 1      | Alublech 88 x 6 x 3 mm                                                                                                                               | zur Herstellung eines<br>Wärmeleitblechs                         |

| 1      | Profilkühlkörper Typ KL-138, 17 mm lang                                                                                                              | z.B. Seifert Typ KL-138;<br>zur Herstellung eines<br>Kühlkörpers |

| 1      | Isolierplatte 90 x 40 x 0,2 mm                                                                                                                       | Polyamid                                                         |

| 1      | Miniatur-Schiebeschalter 8polig, DIL                                                                                                                 |                                                                  |

| 1      | Stiftleiste 4polig, einreihig mit ge-<br>raden Stiften 0,6 x 0,6 mm im Raster<br>2,54 mm, Stiftlänge Lötseite ca. 3 mm,<br>Steck/Wrapseite ca. 6 mm  |                                                                  |

| 1      | Stiftleiste 4polig, zweireihig mit ge-<br>raden Stiften 0,6 x 0,6 mm im Raster<br>2,54 mm, Stiftlänge Lötseite ca. 3 mm,<br>Steck/Wrapseite ca. 6 mm |                                                                  |

| 4      | Kurzschlußbrücke RM 2,54                                                                                                                             | zum Aufstecken auf die<br>Stiftleiste                            |

| 1      | Keramikkondensator 0,047 µF/50 V                                                                                                                     | RM 5                                                             |

| 4      | Keramikkondensator 0,1 µF/50 V                                                                                                                       | RM 5                                                             |

| 1      | Tantal-Elko 2,2 µF/35 V                                                                                                                              | Tropfenform                                                      |

| 4      | Tantal-Elko 4,7 µF/35 V                                                                                                                              | Tropfenform                                                      |

| 4      | Trimmerwiderstand 10 k /0,1 W, stehend                                                                                                               | RM 2,5 x 5                                                       |

| 10     | Widerstand 220 Ω                                                                                                                                     | Alle Widerstände<br>±5%, 0,25 W                                  |

| 8      | Widerstand 4,7 kΩ                                                                                                                                    |                                                                  |

| 13     | Widerstand 10 kΩ                                                                                                                                     |                                                                  |

| 1      | Widerstand 22 kΩ                                                                                                                                     |                                                                  |

| 8      | Anreih-LED, rt, rechteckig 2,5 x 5 mm                                                                                                                | z.B. CQX 10                                                      |

| 16     | Si-Diode BYV 27/100, t <sub>rr</sub> < 25 ns                                                                                                         | z.B. Valvo                                                       |

## Bereitstellungsliste

| Stckz. | Benennung/Daten                                             | Bemerkung                                                         |

|--------|-------------------------------------------------------------|-------------------------------------------------------------------|

| 2      | IC ILQ 30, 4-fach Optokoppler                               | oder ILQ 74                                                       |

| 2      | Zweifach-Voll-Brückentreiber-IC L298                        | SGS Ates, Fa. Weisbauer-Elektronik, Heiliger Weg 1, 4600 Dortmund |

| 1      | NF-Verstärker TBA 820M                                      | 8pol. DIP                                                         |

| 1      | Positiv-Festspannungsregler 7805                            | 5 V/1 A, TO 220                                                   |

| 2      | IC 74 LS 04, Sechs Inverter                                 |                                                                   |

| 2      | IC 74 LS 85, 4-Bit-Vergleicher                              |                                                                   |

| 1      | IC 74 LS 273, 8-Bit-D-Flipflop                              |                                                                   |

| 2      | IC 4584, Sechs inv. Schmitt-Trigger                         | CMOS, oder 74 C 14                                                |

| 1      | IC-Fassung 8polig DIL                                       |                                                                   |

| 4      | IC-Fassung 14polig DIL                                      |                                                                   |

| 4      | IC-Fassung 16polig DIL                                      |                                                                   |

| 1      | IC-Fassung 20polig DIL                                      |                                                                   |

| n.B.   | Wärmeleitpaste                                              |                                                                   |

| n.B.   | Lötdraht                                                    |                                                                   |

| n.B.   | Lötłack                                                     |                                                                   |

| n.B.   | Reinigungsmittel                                            | zum Entfetten der Frontplatte                                     |

| n.B.   | Beschriftungsmaterial, Abreibe-symbole oder Tuscheschreiber | zum Beschriften der Frontplatte                                   |

| n.B.   | Plastik-Spray                                               | zum Besprühen der Frontplatte                                     |

Das zur Inbetriebnahme der Baugruppe erforderliche Material ist der Bereitstellungsliste zur Inbetriebnahme zu entnehmen.

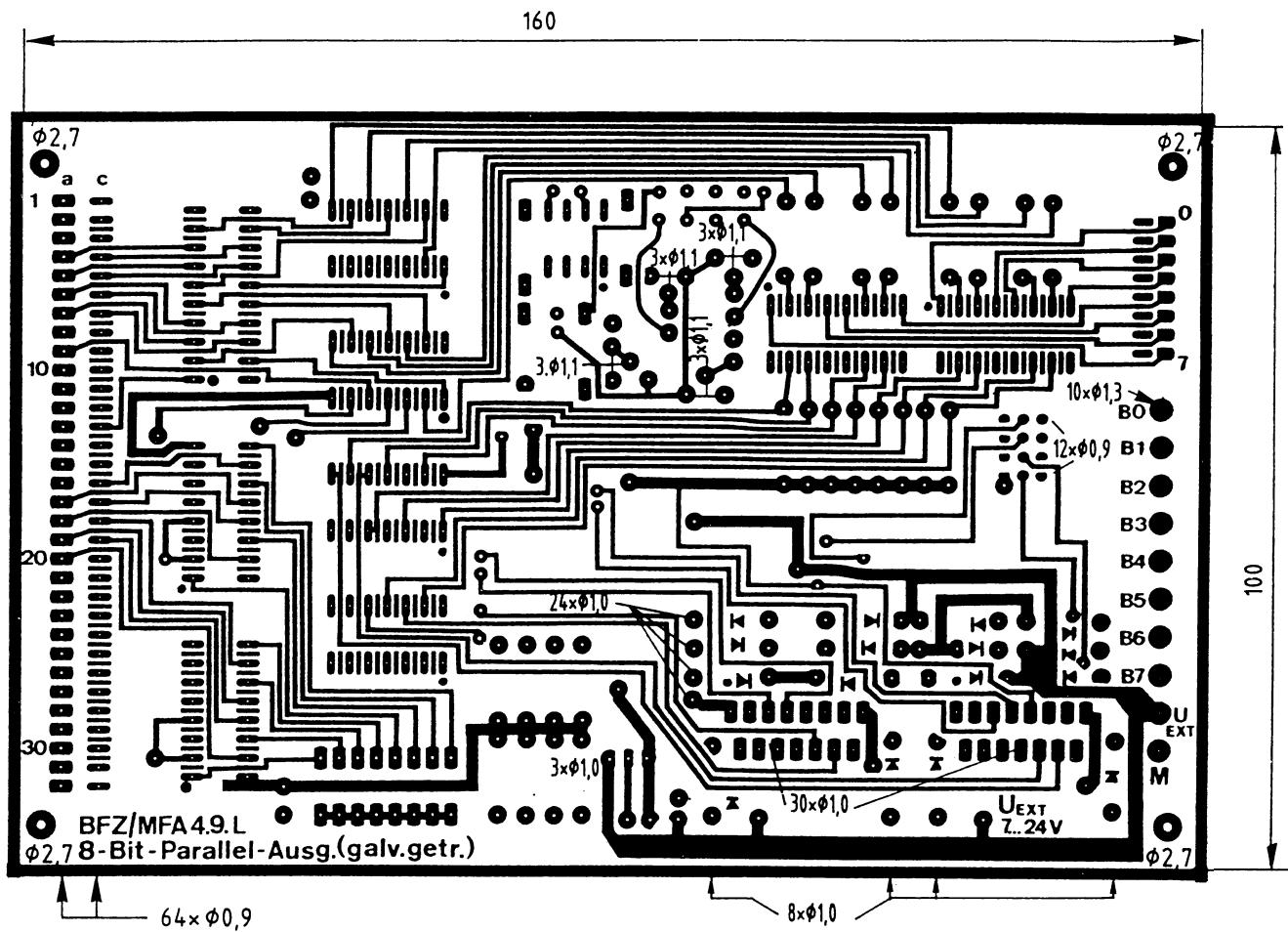

## Bohrplan Leiterplatte

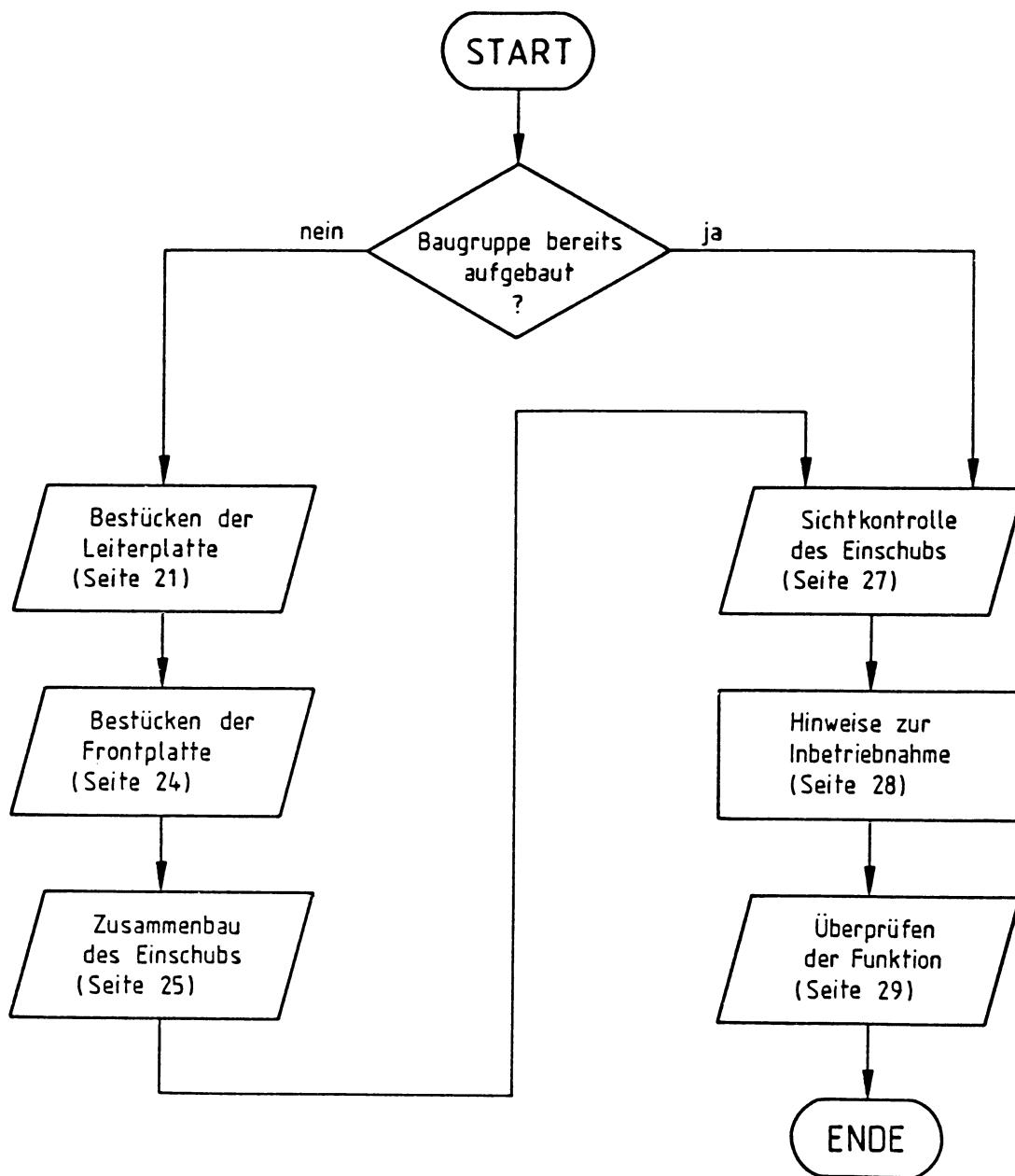

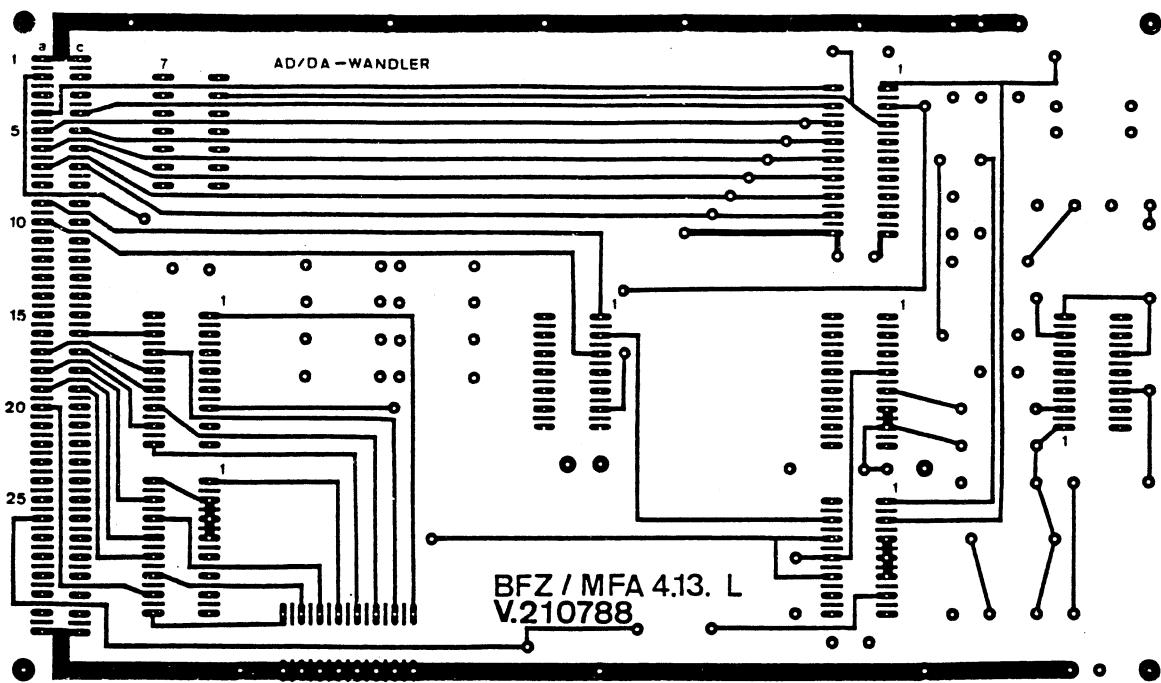

Alle nicht bemaßten Bohrungen  $\phi 0,8$  mm