## Folgen Sie diesem Zeichen!

Der Computermarkt wird immer unübersichtlicher. Wir wollen Ihnen mit unserem jk Qualitätszeichen den besten Weg durch diesen Markt weisen.

Produkte, die unser Zeichen tragen, zeichnen sich durch hervorragende Qualität und Verarbeitung aus. Sie sind durch Forschung und Entwicklung unserer Ingenieure ausgereift

und entsprechen durch laufende Weiterentwicklung immer dem aktuellen Stand der Technik.

Einen Querschnitt durch unser Angebotsspektrum und unsere Programmübersicht sehen Sie auf den folgenden Seiten. Nähere Informationen senden wir Ihnen gerne zu. Für Ihre speziellen Fragen und Probleme haben wir immer ein offenes Ohr.

Wir fertigen und entwickeln für Sie ECB-kompatible Europakarten: CPU-Platinen mit Z80 Prozessor, Intel 80186 Prozessor, Motorola 68000 Prozessor, Floppy-Controller-Platinen, I/O-Platinen, Eprom-Programmierer und Komplettsysteme.

Natürlich liefern wir auch Monitore, Tastaturen, Laufwerke und die gesamte Software zu unseren Systemen.

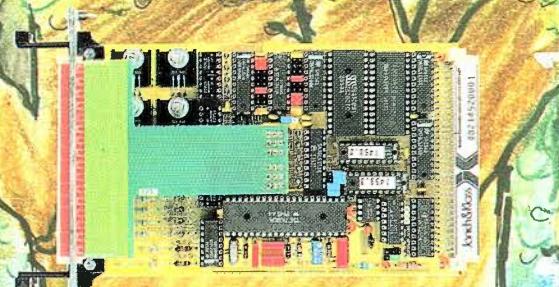

### jk82 CPU-1801

CPU HD64180 mit 6,144 MHz Prozessortakt [Z80 Code-kompatibel] Die CPU arbeitet ohne Wartezyklen im internen RAM. Durch den kürzeren Opcode Fetch und den programmierbaren Refresh-Generator kann eine um 20-25 % höhere Verarbeitungsgeschwindigkeit gegenüber einer Z80B-CPU erreicht werden. Die integrierte MMU erweitert den internen Adressraum auf 1MByte. Über den Bus können weitere 768KByte linear adressiert werden. 1MByte DRAM mit Parity Check Intern stehen 1MByte DRAM mit einem Parity Bit zur Verfügung. Beim Auftreten eines Parity Fehlers wird ein Interrupt ausgelöst.

32KByte abschaltbares Boot-Eeprom Ein Eeprom 27C256 erlaubt Boot-Betrieb. Das Eeprom ist durch I/O-Befehle abschaltbar. Freier I/O Adressraum Durch eine spezielle Hardware-Beschaltung ist es möglich, zusätzlich zu den Karteninternen I/O-Ports weitere 256 I/O-Adressen über den Bus anzusprechen. • Zwei serielle und eine Centronics-Schnittstelle

Auf einer Pfostenleiste stehen zwei serielle Schnittstellen zur Verfügung. Die Baudrate ist programmierbar zwischen 50Baud und 38400Baud. Die Centronics-Schnittstelle ist ebenfalls auf eine Pfostenleiste geführt. • Floppycontroller für max. 3x 5,25" und/oder 3,5" Laufwerke Der Floppycontroller µPD72065 erlaubt den direkten Anschluß von maximal drei 5,25" oder 3,5" Laufwerken. • Festplattencontroller für ein Laufwerk bis max. 72MByte Der Festplattencontroller µPD7261 mit PLL µPD9306 ist für den Anschluß einer Festplatte mit max. 72MByte formatierter Kapazität ausgelegt. • Akkugepufferte Echtzeituhr Die Uhr ist akkugepuffert und zeigt das Datum unter Berücksichtigung der Schaltjahre und Uhrzeit mit Sekunden an. • Betriebssystem CP/M Plus • Zum Lieferumfang gehört das Betriebssystem CP/M Plus. • Stromaufnahme 5V/1A.

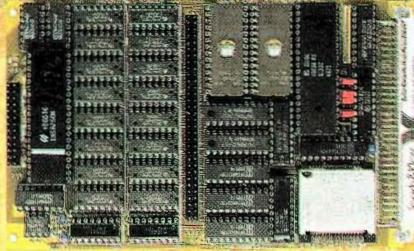

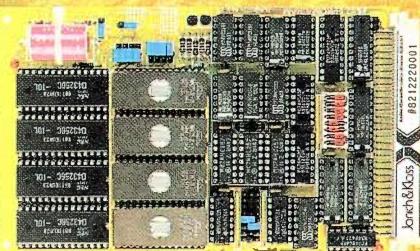

### jk82 SLAVE-186

16Bit Prozessor 80186 Die Karte ist mit dem Prozessor 80186 in der 8- oder 10MHz-Version bestückt. Alle Speicher auf der Karte arbeiten ohne WAIT-Zyklen. • Kommunikation über das Z8038-FIO und zwei weitere I/O-Ports Die Kommunikation der Systembus-CPU mit der Slave-CPU erfolgt über den Interface-Baustein Z8038-FIO. Der Datentransfer kann aber auch über die WAIT-Leitung der CPUs synchronisiert werden. Eine Kommunikation über vektorisierte Interrupts (IM2) ist auf der Z80-Seite ebenfalls möglich. • SpeichergröÙe 512KByte RAM und 64KByte EPROM Die Slave-CPU besitzt 512KByte DRAM sowie zwei 28polige Steckplätze für Eproms von 8KByte - 32KByte SpeichergroÙe (27C128, 27C256). Eine PC-kompatible serielle Schnittstelle nach RS323c Eine PC-kompatible serielle Schnittstelle, realisiert mit einem 8250, erlaubt die Verwendung von entsprechender Software. • 64poliger Erweiterungsstecker Ein 64poliger Stecker erlaubt das Aufstecken von Erweiterungsplatinen wie Monochrome Grafikplatinen, Farbgrafikplatinen oder Speichererweiterungen. • CP/M86-Emulation im EPROM Zum Lieferumfang gehört eine CP/M86-Emulation im EPROM. Der Benutzer arbeitet unter einem emulierten Betriebssystem CP/M86. • Selbsttest und Fehlerdiagnose im EPROM Nach einem RESET wird von dem Slave-186 ein Testprogramm gestartet, das unabhängig von der Z80-CPU läuft. Speicherfehler, EPROM-Prüfsummenfehler sowie defekte I/O-Ports werden erkannt. • Stromaufnahme: 5V/1200mA; 12V/80mA (ohne Erweiterung)

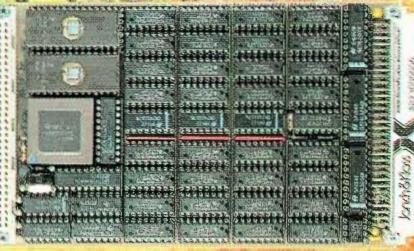

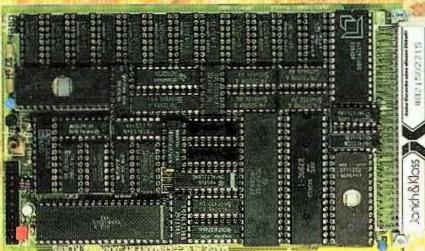

### jk82 CPU 68K

CPU 68000 CPU im PIN-GRID Gehäuse. CPU-Takt 12, 5MHz. • Speicher Auf der Karte befindet sich ein 1MByte dynamisches Ram, aufgeteilt in 2-Banks a 256K x 16 Bit. • I/O und ECB-Bus Interface Alle I/O Operationen werden über ein Z80-Businterface geführt. Das Interface emuliert eine Z80B CPU mit 6MHz Takt (8Bit Datenbreite) inklusive Interrupt-Mode 2 und RETI. • ECX-Erweiterungsbuss Der ECX-Erweiterungsbuss ist ein 16Bit Bus, der alle wesentlichen Signale für ein 68000-System enthält. Hierüber kann z. B. der Speicher des 68000 auf bis zu 9MByte erweitert werden. • Das jk82 68000-OS-9 Betriebssystem jk82 OS-9/68000 ist romfähig. Der gesamte Systemkern und die benutzten I/O-Treiber, wurde in die beiden 27256-EPROMs auf der CPU-Karte programmiert. Somit belegt der Systemkern kein RAM.

### jk82 HDC 5

Hard-Disk-Controller mit WD1010-05 und digitalem Datenseparator jk82 HDC 5 ist zum Betrieb von bis zu zwei 5,25"- oder 3,5"-Winchester-Laufwerken mit ST506-Schnittstelle geeignet. • Fast alle Laufwerke mit ST 506-Interface benutzbar An die Laufwerke werden folgende Anforderungen gestellt: maximal 8 Köpfe (Daten-Oberfläche); maximal 1024 Spuren pro Oberfläche; Step-Zeit zwischen 35 µs (Fast-Step-Mode) und 7,5 ms. Die Leitung „Reduced Current“ sollte am Laufwerk unbenutzt sein. • Sektorgröße programmierbar auf 128, 256 oder 1024Byte pro Sektor • Stromaufnahme: 5V/ca. 900mA.

### jk82 AD-OPTO-10

12Bit Ad-Wandler nach dem Dual-Slope-Verfahren Bei 12Bit Genauigkeit (+Vorzeichen) sind bis zu 6 Wandlungen pro Sekunde möglich. Die Wandlung kann von der CPU aus mit einem OUT-Befehl gestartet werden. Die Platine verfügt über eine eigene Referenzspannungsquelle. • 4 über Optokoppler potentialgetrennte Transistorschaltausgänge Jede Stufe kann einen Strom von max. 2A bei einer maximalen Spannung von 35V gegen die positive oder die negative Versorgungsspannung schalten. Die Transistoren verkraften Einschaltströme bis zu 4A. • Definierte Schaltzustände bei Ausfall der Rechnerstromversorgung Nach jedem RESET des Computers oder bei Stromausfall sperren alle Ausgangstransistoren. Die Transistoren werden erst durch den Rechner definiert freigegeben. • 8 vollständig potentialgetrennte Eingänge (24V) Jeder der 8 Eingänge ist mit einer Z-Diode gegen Überspannung geschützt. Jeder Eingang ist ein potentialfreier Zweipol. • Zwei Z80B-CTCs zur Ausführung von Zustandswechsel-Ereignis- oder Zähl-Interrupts Alle 8 Eingänge sind auf die Z80B-CTCs geführt. Damit können diese Eingänge Ereignis- oder Zählfunktionen ausführen und zur Auslösung von Interrupts benutzt werden. Die 8 Eingänge können mit einer Tiefpasscharakteristik zur Unterdrückung von Störimpulsen nachgerüstet werden. • Zustandsanzeige über LEDs Die Platine besitzt 16 LED-Anschlüsse zur Anzeige des Ein-/Ausgangszustandes. • Stromaufnahme: 5V/800mA; 12V/20mA.

### jk82 EPROM-Simulator 2

Mit dem jk82 EPROM-Simulator 2 lassen sich zwei völlig voneinander unabhängige EPROMs oder RAMs mit Kapazitäten zwischen 8 und 64KByte simulieren. • Vielseitig einsetzbar Aus dem folgenden Angebot lassen sich zwei EPROM-/RAM-Typen per Software beliebig einstellen: EPROMs 2764, 27128, 27256 und 27512. RAMs 6264, 43256. Ebenfalls durch Software steuerbar ist die Umschaltung zwischen Master- und Slavebetrieb. Die maximale Zugriffzeit (bedingt durch den Simulator) beträgt für alle Typen 150ns. • Schutz gegen Fehlbedienung Durch eine spezielle Schutzschaltung mit Kondensator und Serienwiderstand ist sichergestellt, daß auch bei Fehlbedienung keine Schäden auftreten können. • Störsichere Simulation Die EPROM-Adapterkabel sind so konstruiert, daß zwischen zwei Signalleitungen immer eine Masseleitung zu liegen kommt. Abschlußwiderstände auf der Masterseite verringern Reflexionen auf den Leitungen. • Ausführliche Software Die mitgelieferte Software „SIMU2“ läuft mit jedem CP/M-System und ermöglicht komfortables Arbeiten mit dem EPROM-Simulator 2. Mit „SIMU2“ können CP/M-Dateien unter Angabe der zu simulierenden EPROM-/RAM-Typen in den Speicher des Simulators geladen werden. Außerdem kann mit „SIMU2“ der Inhalt des Simulator-RAMs auf einfache Weise bearbeitet werden.

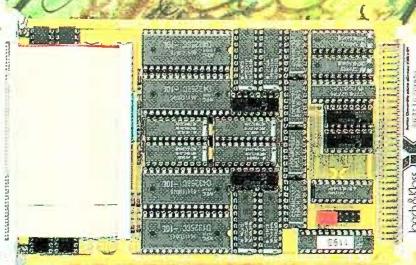

### jk82 EPROM/CRAM

Acht 28polige Memory-Sockel auf der Platine Die 8 Sockel sind in zwei Blöcke zu je 4 Steckplätzen organisiert. Die Bestückung eines Blocks kann wahlweise mit 32K x 8 CRAMs (43256), 32K x 8 EPROMs (27256) oder 64K x 8 EPROMs (27512) jeweils für alle vier Steckplätze gleich erfolgen. • Segmentierte Betriebsart für CPUs mit 64KByte Adreßraum Um den Einsatz in kleineren Rechnern mit nur 64KByte Adreßraum zu ermöglichen, wurde eine segmentierte Betriebsart realisiert, welche den gesamten Speicherraum der Karte in 32KByte große Kacheln zerlegt, die über einen I/O-Port selektiert werden können. • DESELECT-Erkennung zum Ausblenden kleinerer Speicherbereiche • Lithiumbatterie (80mAh) für Datensicherung von CRAMs • Automatischer Zugriffsenschutz bei POWER DOWN Bei einem Spannungsabfall unter 4,5V wird das CE-Signal für alle CRAMs gesperrt. Die CPU kann dann nicht mehr auf die Speicher zugreifen. • Stromaufnahme: ca. 5V/20mA (ohne Speicherbausteine) • Temperaturbereich von -40 Grad bis +72 Grad.

# Mit diesen Platinen sind wir richtungsweisend

## jk82 VIDEO I

Eigenes Subprocessorsystem mit Z80A-CPU und 6845 Video-Controller. Vom jk82-Bus wird die Video I-Platine als I/O-Port mit bidirektionalem Datenkanal und Statusport angesprochen. Durch diese Parallelschnittstelle mit Statusabfrage ergibt sich eine hohe Übertragungsgeschwindigkeit zwischen Video-Karte und Systemprozessor (durchschnittlich 4800 Zeichen pro Sekunde). Zugriff auf den Bildumlaufspeicher nur in den Austastlücken. Die interne Z80A-CPU greift nur in den Austastlücken (horizontal und vertikal) auf den Umlaufspeicher zu. Dadurch werden störende Flimmereffekte auf dem Bildschirm vermieden. Serielle und parallele Tastaturanschlußmöglichkeit. Monitoranschluß über Composite-Video (BAS)-Signal. Stromaufnahme: 5 V/1,1 A · 16 K x 11 Bit Bildwiederholspeicher im Alfa-Modus · 48 KByte Bildwiederholspeicher im Grafik-Modus.

## jk82 CPU I

Z80 (A/B)-CPU mit 2,5 MHz-, 4 MHz- oder 6 MHz-Systemtakt · 2 BYTEWIDE-Steckplätze für bis zu 32 K EPROM oder 8 K RAM pro Steckplatz. Mit Hilfe von 2 Jumperfeldern ist für jeden der beiden Sockel getrennt der Speichertyp einzustellen. Für den Steckplatz 2 kann die Startadresse in 4 K Schritten eingestellt werden, während der Steckplatz 1 immer auf Adresse 0 liegt. Die Speichergröße der beiden Sockel ist ebenfalls unabhängig voneinander in Schritten zu 4 K, 8 K, 16 K, 32 K einzustellen. 2 serielle Schnittstellen nach V 24 (handshake-fähig). Die seriellen Schnittstellen sind mit einem Z80 (A/B)-DART realisiert worden. Zur Baudratenerzeugung werden 2 Kanäle des Z80 (A/B)-CTC benutzt. Beide V 24-Schnittstellen sind handshake-fähig über RTS/CTS und DTR/DCD, 25-pol. · 2 getrennte Oszillatoren für die Baudratenerzeugung und den Systemtakt. Für die Baudratenerzeugung wird der CTC im Counter-Mode betrieben. Auch bei Wechsel der Systemtaktfrequenz ist keine Änderung der CTC-Initialisierung notwendig. Zur Initialisierung der Schnittstellen befinden sich in den Unterlagen einfache Beispielprogramme. Eine Centronics-Parallelschnittstelle. Die Centronics-Schnittstelle wird mit einer Z80 (A/B)-PIO realisiert. Die Datenausgänge sind gepuffert. Über Jumper einstellbare vollständige Dekodierung der I/O-Portadressen. Die CPU I belegt 16 I/O-Portadressen. Die Startadresse kann über Jumper eingestellt werden. Die Reihenfolge der Portadressen ist kompatibel mit der früheren HKM-CPU-Platine. Spannungsüberwachung der 5 V-Versorgungsspannung mit RESET-Generierung bei Unterspannung. Stromaufnahme: 5 V, 750 mA und 12 V, 60 mA bei 4 MHz Systemtakt.

## jk82 DA8

Ausgangsspannungsbereich: 0-10 V, 0-100 mA. Die Kurzschlußstrombegrenzung setzt bei ca. 150 mA ein. Der maximale Kurzschlußstrom überschreitet den Wert von 200 mA nicht. Die Ausgangstransistoren sind einzeln auf Kühlkörpern montiert um thermische Verkopplungen der einzelnen Endstufen zu vermeiden. Die Verstärkung jedes Kanals wird über ein 20-Gang Potentiometer eingestellt. Der Abgleichfehler ab Werk ist kleiner als 1/2 LSB. 8 schnelle DACs mit 8 Bit Auflösung. Die DACs des Typs ZN428-E wandeln ein binäres Wort innerhalb von max. 1,25 µs mit einem Fehler von max. 1/2 LSB. Die Wandlung geschieht ohne „Spikes“. Zwei I/O-Ports adressieren die Wandler. Stromaufnahme: 5 V/100 mA, +15 V/15 mA, -15 V/15 mA (ohne Last).

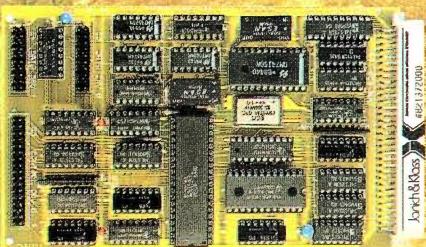

## jk82 Universal Programmer

Die Platine besitzt 24 voll programmierbare Analog-Ein- und Ausgänge (max. 26 V, 400 mA) mit einer Auflösung von 125 mV sowie 6 Digitalausgänge. Alle Bausteine, die mit positiven Spannungen bis max. 26 V bei einem maximalen Strom von 400 mA programmiert werden und in einen der beiden Sockel passen, sind mit dieser Karte und der entsprechenden Software programmierbar. Zum Lieferumfang gehören folgende Softwarepakete: MMIPAL: programmiert PALs von MONOLITHIC MEMORIES INC sowie einige Typen von NATIONAL SEMICONDUCTOR · INTEPRO: programmiert EPROMs (50ms, CMOS 25ms) sowie die INTEL-Typen im „Fast Mode“ · TEXASPRO: programmiert PROMs von TEXAS INSTRUMENTS

## jk82 P/SIO:

Vier serielle Schnittstellen nach V.24 (Teilmenge) mit Treibern und Empfängern nach V.28 (kompatibel zur jk82 DPS-IO). Die vier seriellen Schnittstellen sind mit RTS/CTS- und DTR/DCD-Handshake-Möglichkeit ausgestattet. Sie wurden mit zwei Z80B-SIO/O und einem Z80B-CTC zur Baudrateneinstellung realisiert. Die Baudaten der jeweiligen B-Kanäle der beiden SIO-Bausteine lassen sich unabhängig voneinander programmieren, während die beiden A-Kanäle immer nur auf dieselbe Baudrate programmiert werden können. Die Centronics-Schnittstelle wird über eine Z80B-PIO betrieben. Die Datenausgänge sind gepuffert. Über einen DIL-Schalter einstellbare vollständige Dekodierung der I/O-Portadressen. Die jk82 P/SIO belegt 16 I/O-Adressen. Die Startadresse kann über einen DIL-Schalter eingestellt werden. Die Reihenfolge der Portadressen ist kompatibel zu allen jk82/CPU-Platinen.

### jk82 CPU III

Effektive Speicherverwaltung von max. 1MByte Adreßraum Die CPU III erzeugt vier zusätzliche Adressen (A16-A19), die den Adreßraum auf 1MByte erweitern. Es wird eine Umrechnung vom logischen Adreßraum in den physikalischen Adreßraum vorgenommen · 64KByte oder 256KByte Speicher auf der Karte Je nach Bestückung finden 64KByte (4164) oder 256KByte (41256) dynamisches RAM auf der Platine Platz. Ein unter Software-Kontrolle ausblendbares EPROM von 2KByte bis 16KByte Größe ermöglicht BOOT-Betrieb · Z80A-DMA für schnellen Datentransfer Auf der Karte befindet sich ein Z80A-DMA Baustein, der einen schnellen Inter-Bank-Move ausführen kann. Auch schnelle I/O-Bausteine können mit dem DMA bedient werden · Echtzeituhr mit Akkupufferung Eine Echtzeituhr hat ebenfalls Platz gefunden. Die Uhr zeigt das Jahr, das Datum, den Wochentag sowie die Zeit in Stunden, Minuten und Sekunden. Über einen Kanal des Z80-CTC kann die Uhr auch Interrupts auslösen · Stromaufnahme typisch: 5 V, 1,2 A.

### jk82 CPU IV:

Drei Versionen mit Stromaufnahmen von 10 mA bis 550 mA erhältlich Die Karte ist in drei Versionen erhältlich. Die Version TIJ-Z-1152 ist mit den 2,5 MHz Z80-Bausteinen der Firma Sharp ausgerüstet. Diese haben einen besonders stromsparenden Standby-Modus. Die Version TIJ-Z-1153 ist mit den 4 MHz Z80-Bausteinen der Firma Toshiba ausgerüstet. Trotz der hohen Taktfrequenz liegt die Stromaufnahme dieser Version nur bei ca. 50 mA. Für kostenempfindliche Anwendungen ist die Version TIJ-Z-1154 (4 MHz) vorgesehen. Sie ist konventionell in LS/ALS-Technik bestückt. Natürgemäß liegt die Stromaufnahme dieser Version wesentlich höher · Max. 32KByte EPROM und 32KByte RAM auf der Karte möglich Auf der Karte befinden sich fünf 28polige BYTEWIDE-Sockel, die teilweise mit EPROMs, EEPROMs, SRAMs oder DRAMs bestückt werden können. Maximal finden 32KByte EPROM und 32KByte RAM Platz · Zwei Z80-PIOs und ein Z80-CTC auf Pfostenstecker geführt Zwei Z80-PIO Bausteine stellen 32 parallele voll programmierbare Input/Output-Leitungen, sowie 8 Steuerleitungen auf zwei 26poligen Pfostenleisten zur Verfügung. 16 Leitungen sind mit Pull-Up-Widerständen beschaltet um bei offenen Eingängen definierte Zustände sicherzustellen. Ein Z80-CTC realisiert 4 programmierbare 8Bit-Zähler · Akkugepufferte Echtzeituhr Eine akkugepufferte Echtzeituhr wird über 8 Leitungen einer PIO bedient. Die Uhr kann auch als Stopuhr mit Interrupts für Sekunden, Minuten und Stunden programmiert werden.

### jk82 AD12

Beide Typen von Multiplexern haben einen Eingangsüberspannungsschutz bis 35 V. Der Arbeitsbereich beträgt  $\pm 10$  V. Um eine Übertragungsgenaugigkeit von 0,01% (1/4 LSB) zu erreichen, darf der Quellwiderstand der angeschlossenen Signalquellen 10K nicht überschreiten · Präzisionsinstrumentenverstärker mit einstellbarer Verstärkung Der Instrumentenverstärker INA101 ist ein Präzisionsverstärker mit sehr geringem Temperaturkoeffizient und Verstärkungsfehler. Durch einen externen Widerstand ist die Verstärkung einstellbar. Im Auslieferzustand beträgt die Verstärkung  $G = 1$  · Schneller Sample & Hold Verstärker ermöglicht die Erfassung von Wechselspannungen bis 75 KHz · 12Bit ADC mit Prozessorinterface Der AD-Wandler arbeitet nach dem Verfahren der sukzessiven Approximation, wodurch eine Wandlungszeit bei 12Bit von max. 30ys erreicht wird · Stromaufnahme: 5 V/200 mA, +15 V/27 mA, -15 V/36 mA.

### jk82 FDC III

Floppy-Disk-Controller mit  $\mu$ PD765 und  $\mu$ PD9201 jk82 FDC III ist zum gleichzeitigen Betrieb von bis zu drei 3,5"/5,25"- und bis zu vier 8"-Floppylaufwerken geeignet. Die Umschaltung erfolgt unter Softwarekontrolle. · SCSI-Interface Das SCSI (SASI)-Interface dient zum Anschluß von Magnetplattenlaufwerken, Streamern oder optischen Platten mit integriertem SCSI-Controller. · Z80B-PIO und Z80-B CTC PIO und CTC werden als Systeminterface für den Floppy- und Winchester-Teil benutzt. Dies ermöglicht einen echten Interruptbetrieb der Massenspeichercontroller. · Uhren-IC MEM E050 mit Akkupufferung · Stromaufnahme: 5V/1A bei 6MHz Systemtakt.

### jk82 DPS-IO:

Vier serielle Schnittstellen nach V.24 (Teilmenge) mit Treibern und Empfängern nach V.28 (kompatibel zur jk82 P/SIO) Die vier seriellen Schnittstellen sind mit RTS/CTS-Handshake-Möglichkeit ausgestattet. Sie wurden mit zwei Z80B-SIO/O und einem Z80B-CTC zur Baudrateneinstellung realisiert. Die Baudraten der jeweiligen B-Kanäle der beiden SIO-Bausteine lassen sich unabhängig voneinander programmieren, während die beiden A-Kanäle immer nur auf dieselbe Baudrate programmiert werden können. Eine Centronics-Parallelschnittstelle Die Centronics-Schnittstelle wird über eine Z80B-PIO betrieben. Die Datenausgänge sind gepuffert. Floppy-Disk-Controller für bis zu 3 Mini-/Micro-Laufwerke Das Floppy-Disk-Interface ist mit dem NEC µPD765-Controller und digitalem Datenseparator ausgeführt worden. Der Controller ist für bis zu drei 5,25" oder 3,5"-Laufwerke doppelseitig oder einseitig mit 40 oder 80 Spuren pro Seite geeignet. Über ein PAL einstellbare vollständige Dekodierung der I/O-Portadressen Die jk82 DPS-IO belegt 20 I/O-Adressen. Die Adressen sind standardmäßig kompatibel zur jk82 P/SIO und jk82 FDC5 eingestellt. Damit kann die Platine problemlos unter jk82 CP/M PLUS betrieben werden. Stromaufnahme: 5 V, ca. 500 mA und 12 V, ca. 80 mA.

### jk82 GPIB

General-Purpose-Interface-Bus nach IEC625 / IEEE 488 - Buskontroller NEC µPD 7210 interruptfähig über Z80A CTC (2 Kanäle) - Open-Kollektor-IEEE-Bustreiber 75160/75161. Die jk82 GPIB-Baugruppe ist in der Lage, folgende IEEE-Funktionen durchzuführen:

SH1 - Source Handshake

AH1 - Acceptor Handshake

T5 - Talker

TE5 - Extended Talker

L3 - Listener

LE3 - Extended Listener

SR1 - Service Request

RL1 - Remote Local

PP1 - Parallel Poll Remote

PP2 - Parallel Poll Local

DC1 - Device Clear

DT1 - Device Trigger

C1-C5 - Controller (alle Funktionen). Eine Centronics-Parallelschnittstelle Die Centronics-Schnittstelle wird mit einer Z80A-PIO realisiert. Die Datenausgänge sind gepuffert. Ein Centronics-Stecker kann über die 34pol. Pfostenreihe 1:1 angequetscht werden.

### jk82 SLAVE-CPU II

Kommunikation über das Z8038-FIO und zwei weitere I/O-Ports Die Kommunikation der Systembus-CPU mit der Slave-CPU erfolgt über den Interface-Baustein Z8038-FIO. Der Baustein besitzt ein 128Byte tiefes FIFO-RAM, das von zwei Seiten aus asynchron ansprechbar ist. Der Datentransfer kann aber auch über die WAIT-Leitungen der CPUs synchronisiert werden. Eine Kommunikation über vektorisierte Interrupts (IM2) ist ebenfalls in beiden Richtungen möglich. Speichergröße 64KByte Die Slave-CPU besitzt 64KByte RAM sowie einen 28poligen Steckplatz für ein EPROM von 2KB-16KB Speichergröße (2716, 2732, 2764, 27128). Das EPROM kann mittels eines OUT-Befehls ein- oder ausgeblendet werden. Zwei serielle Schnittstellen nach V24 oder RS232C Zwei RS232C gepufferte serielle Schnittstellen, realisiert mit einer Z80B-SIO, ermöglichen den Anschluß von Terminal, seriellem Drucker oder einem weiteren Computer. Zwei parallele Schnittstellen mit Centronics-Belegung Zwei nach CENTRONICS beschaltete Parallelports, realisiert durch zwei Z 80B-PIOs, erlauben den Anschluß von zwei Druckern. Einer der beiden Ports kann auch allgemein als bidirektionaler Parallelport genutzt werden. Standard-Version 6 MHz Die Stromaufnahme beträgt typisch 5 V, 850 mA und 12 V, 60 mA.

# Programmübersicht

## Zentral-Baugruppen

|                | CPU     | Takt max. | EPROM max. | SRAM max. | DRAM max. | Adressbereich        | Serielle E/A | Parallele E/A | Timer frei | Uhr | I [mA] +5V | I [mA] +12V | Bemerkung                                                  |

|----------------|---------|-----------|------------|-----------|-----------|----------------------|--------------|---------------|------------|-----|------------|-------------|------------------------------------------------------------|

| * ik82 CPU1    | Z80A/B  | 4/5/6 MHz | 32KB       | 8KB       | -         | 64KB                 | 2xRS232c     | Centronics    | 2          | -   | 800        | 60          | Kleinere Steuerungssysteme, Einplatinen-Anwendungen        |

| ik82 CPU2      | Z80A    | 4 MHz     | 8KB        | -         | 64KB      | 1MB                  | 2xRS232c     | Centronics    | 2          | -   | 1000       | 50          | CP/M PLUS-Systeme                                          |

| ik82 CPU2-256  | Z80A/B  | 4/5/6 MHz | 16KB       | -         | 256KB     | 1MB                  | 2xRS232c     | Centronics    | 2          | -   | 1000       | 50          | CP/M PLUS-Systeme                                          |

| * ik82 CPU3    | Z80A/B  | 4/5/6 MHz | 16KB       | -         | 256KB     | 1MB                  | -            | -             | 4          | ja  | 1200       | -           | CP/M PLUS-Systeme, Z80-DMA, Vektor-Ram mit Adreßumsetzung. |

| * ik82 CPU4    | Z80A/C  | 2,5/4 MHz | 32KB       | 32KB      | -         | 64KB                 | -            | 2xZ80-PIO     | 4          | ja  | 35         | -           | CMOS-Version                                               |

| * ik82 CPU68K  | 68000   | 12,5 MHz  | 128KB      | -         | 1MB       | 9MB                  | -            | -             | -          | -   | 1600       | -           | OS-9 Systeme                                               |

| * ik82 CPU1801 | HD64180 | 6,144 MHz | 32KB       | -         | 1MB       | 1MB int.<br>768KBex. | 2xRS232c     | Centronics    | 2          | ja  | 1000       | -           | Einplatinencomputer, 5,25" FDC, 5,25" HD, CP/M PLUS        |

| ik82 EPC1.6    | Z80A/B  | 4/6 MHz   | 8KB        | -         | 256KB     | 512KB                | 2xRS232c     | Centronics    | 1          | -   | 1300       | 50          | Einplatinencomputer, 5,25" FDC und ZDOS oder CP/M PLUS     |

| ik82 EPC2      | Z80B    | 6 MHz     | 8KB        | -         | 128KB     | nur intern           | 2xRS232c     | Centronics    | -          | -   | 1500       | 100         | Einplatinencomputer, 8/5,25" FDC und Grafikteil (μPD7220)  |

## Speicher-Baugruppen

|                   | Takt max. | EPROM max. | SRAM max. | DRAM max. | Dekodierter Adreßbereich | Deselect Ein/Ausgang | Parity | I [mA] +5V | I [mA] +12V | Bemerkung                                                                                                            |

|-------------------|-----------|------------|-----------|-----------|--------------------------|----------------------|--------|------------|-------------|----------------------------------------------------------------------------------------------------------------------|

| ik82 BYTEWIDE     | 4 MHz     | 64KB       | 64KB      | -         | 1MB                      | Ausgang              | nein   | 220        | -           | Beliebige Mischung von EPROMs 1K x 8 bis 8K x 8 und SRAMS 2K x 8 bis 8K x 8 möglich.                                 |

| * ik82 EPROM CRAM | 6 MHz     | 512KB      | 256KB     | -         | 1MB über E/A unbegrenzt  | Eingang              | nein   | 20         | -           | Lithiumbatterie, Zugriffsschutz bei „Power Down“, Mischbestückung EPROM/CRAM möglich, segmentierter Betrieb möglich. |

| ik82 SMB          | 6 MHz     | -          | -         | 1MB       | 1MB, über E/A bis 4MB    | Eingang              | nein   | 1000       | -           | ik82 CP/M PLUS unterstützt bis zu drei 1MB-Karten                                                                    |

| ik82 RAE          | 4 MHz     | -          | -         | 1MB       | 1MB                      | Eingang              | nein   | 1250       | -           | Z80-DMA und Adreßerzeugung (A16-A19).                                                                                |

## Floppy/Winchester-Controller

|             | Takt max. | Floppy/Hard Disk | Laufwerke | Bestückung | I [mA] +5V                         | I [mA] +12V | Bemerkung |                                                                     |                           |

|-------------|-----------|------------------|-----------|------------|------------------------------------|-------------|-----------|---------------------------------------------------------------------|---------------------------|

| ik82 DPS-IO | 6 MHz     | 3,5/5,25"        | 8"        | HD SASI    | μPD765, CTC, PIO und zwei SIOs     | 800         | 60        | E/A Karte zur CPU3 mit 4xRS232c und einer Centronics Schnittstelle. |                           |

| ik82 FDC8/5 | 4 MHz     | 3 o.             | 3         | -          | μPD765, Z80-DMA                    | 900         | -         | Digitaler Datenseparator 9216                                       |                           |

| ik82 FDC2   | 6 MHz     | 3 u.             | 4         | -          | μPD765, CTC, PIO<br>64KB DRAM, Uhr | 1000        | -         | Für CP/M PLUS-Anwendungen mit CPU2 oder CPU3                        |                           |

| * ik82 FDC3 | 6 MHz     | 3 u.             | 4         | -          | μPD765, CTC, PIO<br>Uhr            | 900         | -         | Für CP/M PLUS-Anwendung mit CPU2-256 oder CPU3                      |                           |

| * ik82 HDC5 | 6 MHz     | -                | -         | 2          | -                                  | WD1010-05   | 900       | -                                                                   | Für CP/M PLUS-Anwendungen |

## SLAVE-CPU-Baugruppen

|                 | Takt max. | Funktion                                                            | Bestückung                        | I [mA] +5V | I [mA] +12V | Bemerkung                                                               |

|-----------------|-----------|---------------------------------------------------------------------|-----------------------------------|------------|-------------|-------------------------------------------------------------------------|

| ik82 SLAVE1     | 6 MHz     | Z80-Slave-CPU mit einem Z8038-FIO<br>64KB DRAM, EPROM und Wrap-Feld | CPU, FIO, DRAM                    | 500        | -           | Asynchrone Koppelung mit der Bus-CPU ermöglicht intelligente Peripherie |

| * ik82 SLAVE2   | 6 MHz     | Wie SLAVE1, jedoch statt Wrap-Feld<br>2xRS232c, 2xCentronics        | CPU, FIO, DRAM<br>2xPIO, CTC, SIO | 850        | 60          | Intelligente Druckssteller, serieller Datenkonzentrator etc.            |

| * ik82 SLAVE186 | 10 MHz    | iAPX186-Slave-CPU mit Z8038-FIO<br>512KB DRAM, EPROM, 1xRS232c      | CPU, FIO, DRAM<br>8250            | 1100       | 60          | CP/M-86 Emulator im EPROM, Optional DOS PLUS mit PC-Mode möglich        |

## Sonstige Peripherie-Baugruppen

|                             | Takt max. | Funktion                                                                            | Bestückung                   | I [mA] +5V | I [mA] +12V | Bemerkung                                                                              |

|-----------------------------|-----------|-------------------------------------------------------------------------------------|------------------------------|------------|-------------|----------------------------------------------------------------------------------------|

| * ik82 UNIVERSAL PROGRAMMER | 6 MHz     | Programmiert EPROMs, PALs bipolare PROMs sowie Single Chips μPs                     | 23 DA Kanäle<br>6 TTL Kanäle | 350        | 50          | Für PROMs, PALs und EPROMs sind die Sockel auf der Frontplatte.                        |

| ik82 (E)PROM-PROGRAMMER     | 4 MHz     | Programmiert 2516-2764 sowie die TBP-Serie mit dem BPE                              | TTL                          | 370        | 300         | „Low Cost“-Programmer                                                                  |

| ik82 BPE                    | 4 MHz     | Zusatztischgerät zum (E)PROM-Programmer für TBP-PROMs                               | TTL                          | 500        | -           | Vier TEXTOOL-Sockel für alle TBP-Proms Wird an den (E)PROM PRG. angeschlossen          |

| ik82 BAW                    | 6 MHz     | Busabschluß, Arithmetikprozessor, Watchdog.                                         | Z80-CTC opt. AMD9511/12      | 1000       | 500         | Ohne AMD9511/12 als aktiver Busabschluß mit Watchdog-Schaltung.                        |

| * ik82 EPROM-SIMULATOR2     | 6 MHz     | Simuliert bis zu 2 EPROMs oder RAMs von 8K x 8 bis 64K x 8 in einer fremden Platine | 128 KB RAM                   | 300        | -           | Der interne Speicher liegt im E/A-Adreßraum (4 Ports). Bediensoftware im Lieferumfang. |

\* Platine ist in diesem Prospekt beschrieben

## Ein/Ausgabe-Baugruppen

|                   | Takt max. | Parallel Ein | Parallel Aus            | Serielle E/A             | Analoge Ein    | Analoge Aus      | Sonstige E/A      | Stromaufnahme I [mA] |      |      |      | Bemerkung                                                               |

|-------------------|-----------|--------------|-------------------------|--------------------------|----------------|------------------|-------------------|----------------------|------|------|------|-------------------------------------------------------------------------|

|                   |           |              |                         |                          |                |                  |                   | +5V                  | +12V | +15V | -15V |                                                                         |

| jk82 OPTO IN      | 6 MHz     | 16           | -                       | -                        | -              | -                | -                 | 500                  | -    | -    | -    | 4 Kanäle Interrupt-fähig (Z80-CTC)<br>Option: Frontplatte mit LEDs      |

| jk82 OPTO OUT     | 6 MHz     | -            | 16                      | -                        | -              | -                | -                 | 650                  | -    | -    | -    | max. 50V, 2 A potentialgetrennt pro Kanal, Option:Frontplatte mit LEDs  |

| * jk82 AD12       | 6 MHz     | -            | -                       | -                        | 16/32<br>12Bit | -                | -                 | 200                  | -    | 27   | 36   | 16 diff. oder 32 unipol. Eingänge<br>Option: Frontplatte mit VG-Leiste  |

| * jk82 DA8        | 6 MHz     | -            | -                       | -                        | -              | 8<br>8Bit        | -                 | 100                  | -    | 800  | 100  | Ausgänge für 10V, 100 mA ausgelegt<br>Option: Frontplatte mit VG-Leiste |

| * jk82 AD-OPTO-IO | 6 MHz     | 8            | 4                       | -                        | 2<br>12 Bit    | -                | -                 | 800                  | 20   | -    | -    | 8 Eing. Interrupt-fähig (2x Z80-CTC)<br>Option: Frontplatte mit LED's   |

| * jk82 GPIB       | 6 MHz     | Centronics   | -                       | -                        | -              | -                | IEC625<br>IEEE488 | 700                  | -    | -    | -    | IEC-Buscontroller μPD7210 über Z80-CTC Interrupt-fähig.                 |

| * jk82 P/SIO      | 6 MHz     | Centronics   | 4 x RS232c<br>1 x 20 mA | -                        | -              | -                | -                 | 500                  | 100  | -    | -    | Eine PIO, Zwei SIOs mit Z80-CTC als Baudratengenerator.                 |

| jk82 SIO          | 6 MHz     | -            | -                       | 4 x RS232c<br>4 x RS 422 | -              | -                | -                 | 500                  | 100  | -    | -    | Zwei SIOs mit 8254 als Baudratengenerator, 2 Kanäle auch 20 mA          |

| * jk82 DPS-IO     | 6 MHz     | Centronics   | 4 x RS232c              | -                        | -              | 3 x FDC<br>5,25" | 700               | 100                  | -    | -    | -    | E/A Karte besonders zum Einsatz unter CP/M PLUS geeignet.               |

| jk82 PIO-WRAP     | 6 MHz     | 32           | 32                      | -                        | -              | -                | -                 | 310                  | -    | -    | -    | Vier Z80-PIOs und ein Wrap-Feld                                         |

| jk82 UNI-WRAP     | 6 MHz     | -            | -                       | -                        | -              | -                | -                 | 320                  | -    | -    | -    | Universelles ECB-Interface mit großem Wrap-Feld                         |

## Video/Grafik-Baugruppen

|               | Takt max. | Funktion                                                           | Bestückung                 | I [mA]<br>+5V | I [mA]<br>+12V | Bemerkung                                                                |

|---------------|-----------|--------------------------------------------------------------------|----------------------------|---------------|----------------|--------------------------------------------------------------------------|

| * jk82 VIDEO1 | 6 MHz     | Universelles Videointerface mit hochauflösender Grafik (768 x 512) | 64K x 11 DRAM<br>MC6845    | 1100          | -              | max. 25 x 132 Zeichen, kleinere Formate z. B. 12 x 40 ebenfalls möglich. |

| jk82 TERM1    | -         | Terminalplatine ADM3A-kompatibel                                   | 2K x 8 SRAM, SIO<br>MC6845 | 1000          | 60             | Bildformat 24 x 80, über seriellen E/A ansteuerbar                       |

| jk82 GRAFIK2  | 6 MHz     | Universelle 8 Farben Grafik mit z. B. 608 x 431, „non interlaced“  | μPD7220<br>16K x 48 DRAM   | 1100          | -              | Koaxialstecker für R, G, B, Sync „Composite sync einstellbar“            |

\* Platine ist in diesem Prospekt beschrieben