Vorläufige Anwenderinformationen

---

Diese Ausgabe 1.0 des Handbuchs beschreibt die Leiterplatte mit dem Revisionscode 146 - 8526.

# CPU85SC

Die CPU85SC ist eine Z80 CPU-Baugruppe für alle Anwendungsbereiche, besonders jedoch für große und komfortable Geräte, z.B. als CPU für Floppy/Harddisk-Computer oder als Master-CPU bei aufwendigen Automatisierungsaufgaben.

Sie beinhaltet:

- Z80 CPU mit bis zu 64 KByte EPROM oder 32 KByte Eeprom und 8 KByte RAM.

- Adressraumerweiterung auf 1 MByte (Bankadreßerzeugung).

- Echtzeituhr und 128 Byte CMOS-Permanentspeicher

- Zwei serielle Schnittstellen, komplett RS232 getrieben

- 20 Bit Parallelport mit drei 16-Bit-Zählern

# ELZET 80

Mikocomputer GmbH & Co. KG

Wilhelm-Mellies-Straße 88

D-4930 Detmold 18

Tel. 05232 - 8131 · Tx. 931473 elzet d

5.11.85

---

# ELZET 80

---

## Vorläufige Anwenderinformationen

---

1

### INHALTSVERZEICHNIS

#### 3 HARDWARE

|       |                                            |

|-------|--------------------------------------------|

| 3.1   | Blockschaltbild.....                       |

| 3.2   | Funktion.....                              |

| 3.3   | Anschlüsse.....                            |

| 3.4   | Einstellmöglichkeiten.....                 |

| 3.4.1 | Steck- und Lötbrücken.....                 |

| 3.4.2 | Einstellmögl. durch Betriebssoftware.....  |

| 3.4.3 | Einstellmögl. durch Bauelementewechsel.... |

#### 4 SOFTWARE

|     |                      |

|-----|----------------------|

| 4.1 | Allgemeines.....     |

| 4.2 | Initialisierung..... |

#### 6 TECHNISCHE UNTERLAGEN

|     |                             |

|-----|-----------------------------|

| 6.1 | Schaltungsbeschreibung..... |

| 6.2 | Technische Daten.....       |

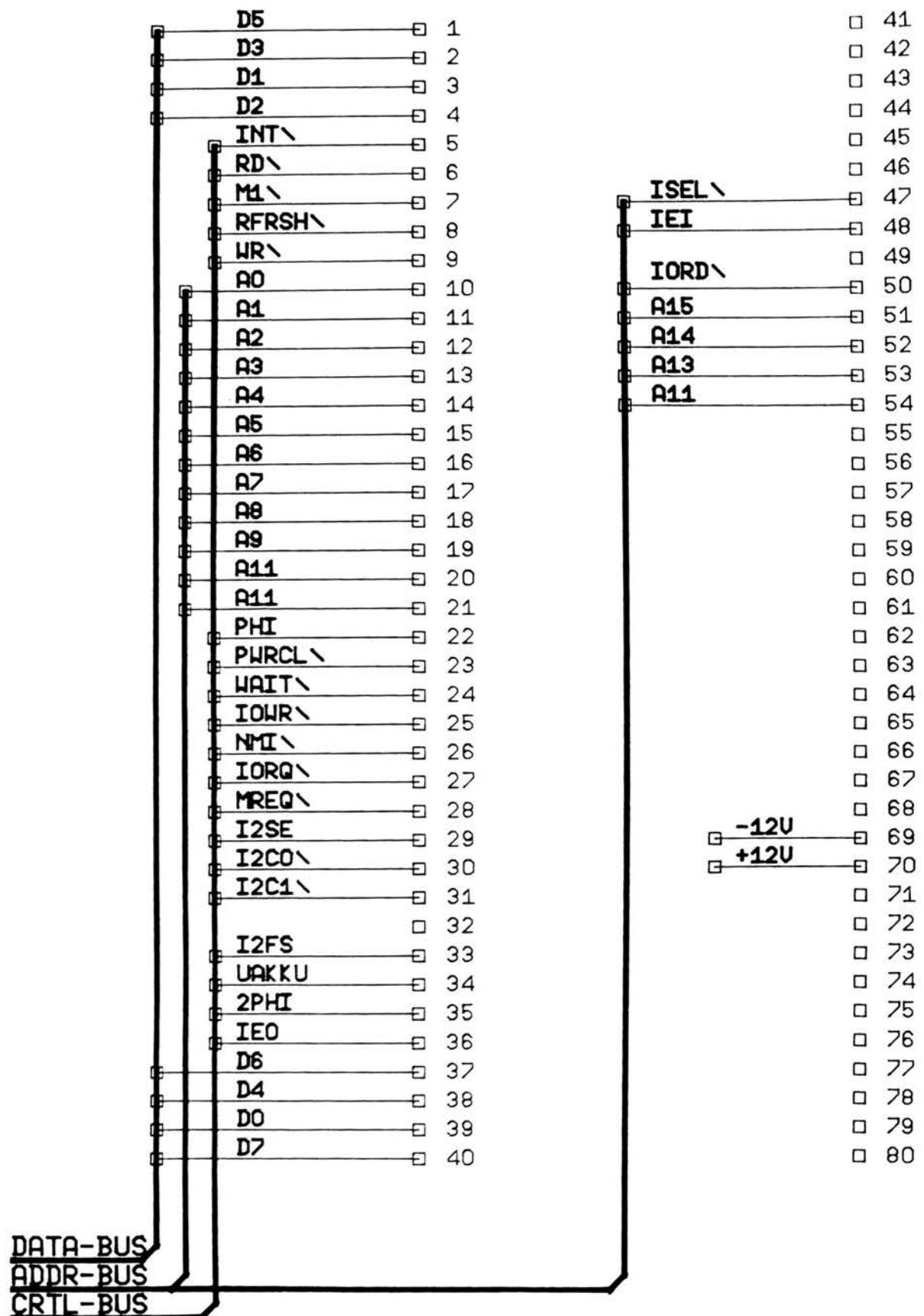

| 6.3 | Busteckerbelegung.....      |

| 6.4 | Stückliste.....             |

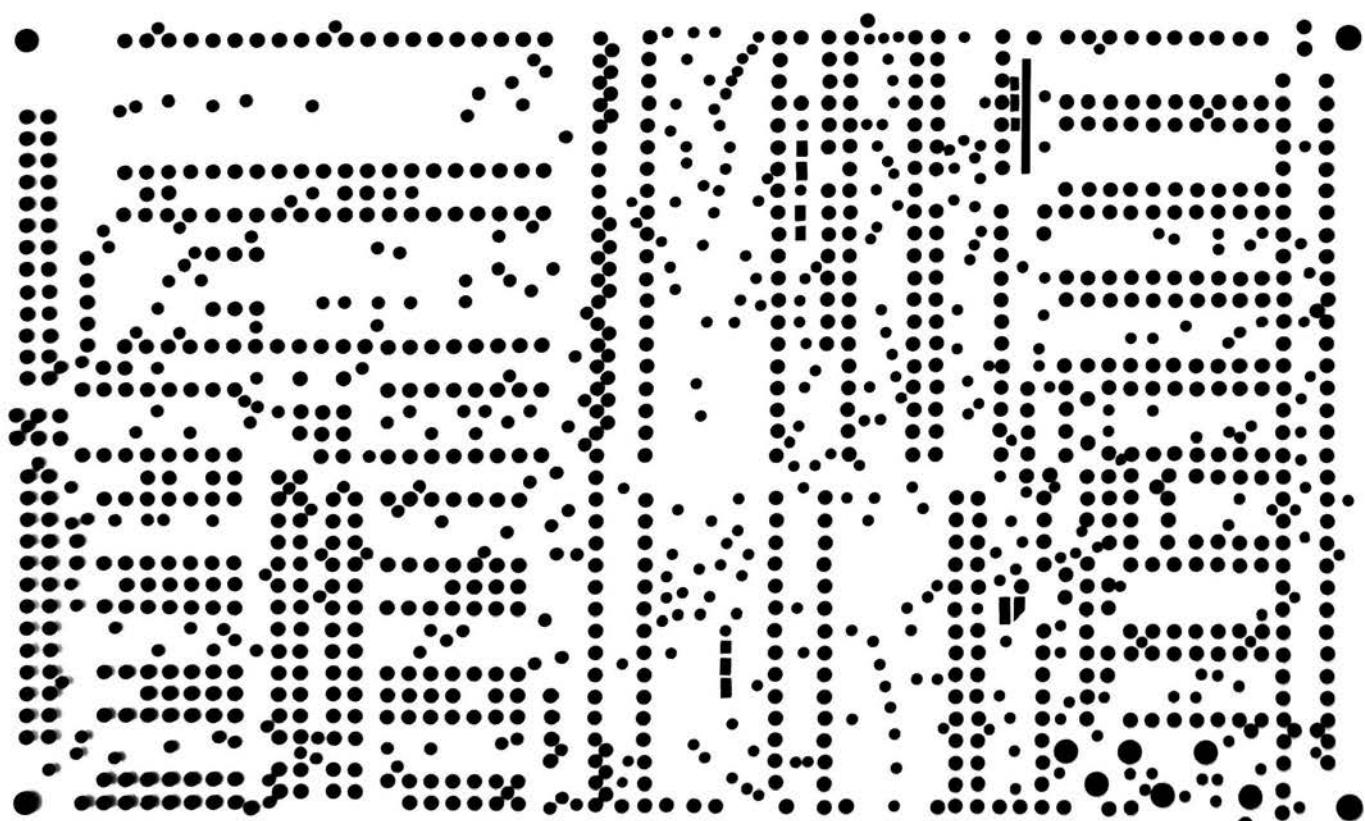

| 6.5 | Bestückungsplan.....        |

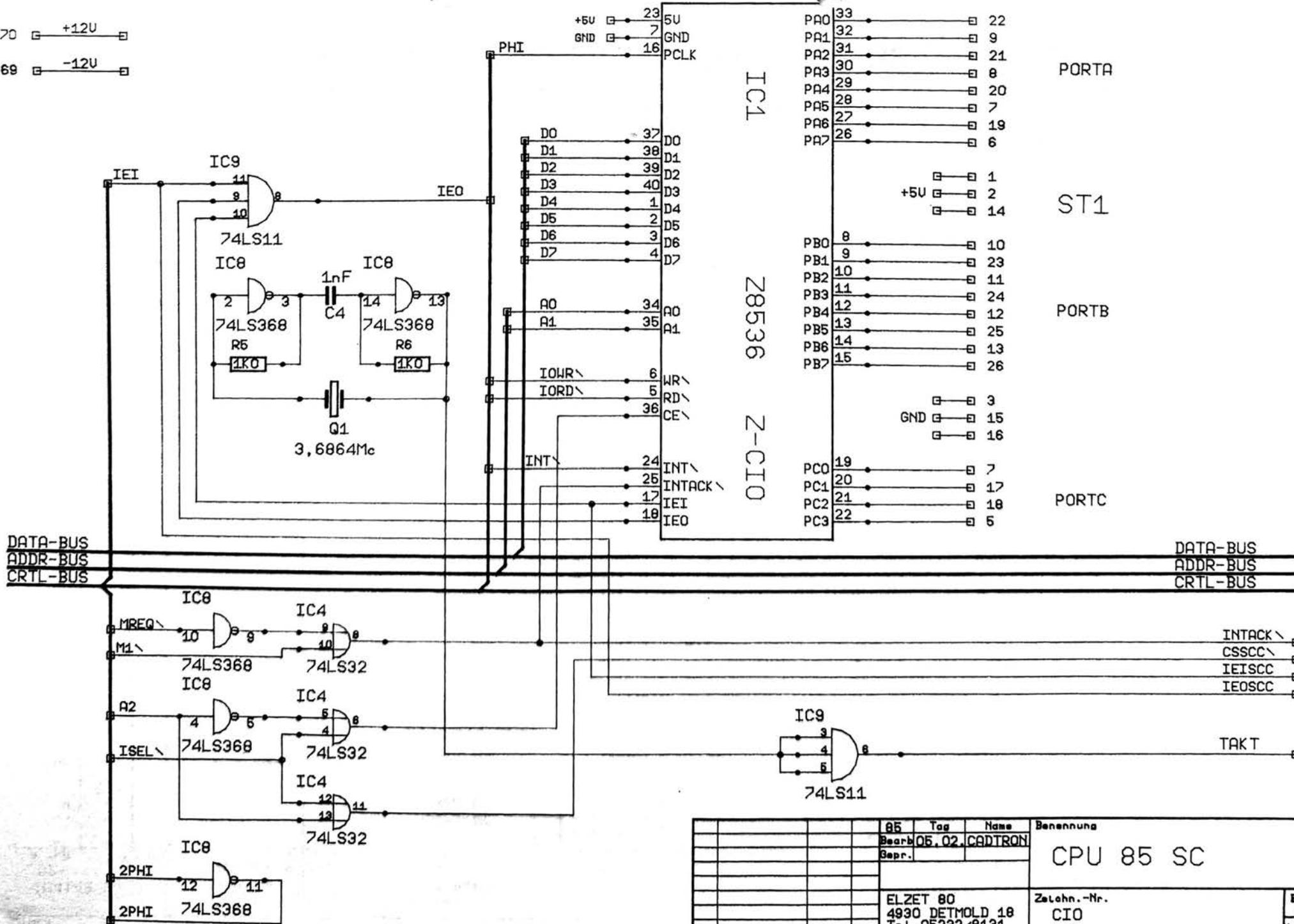

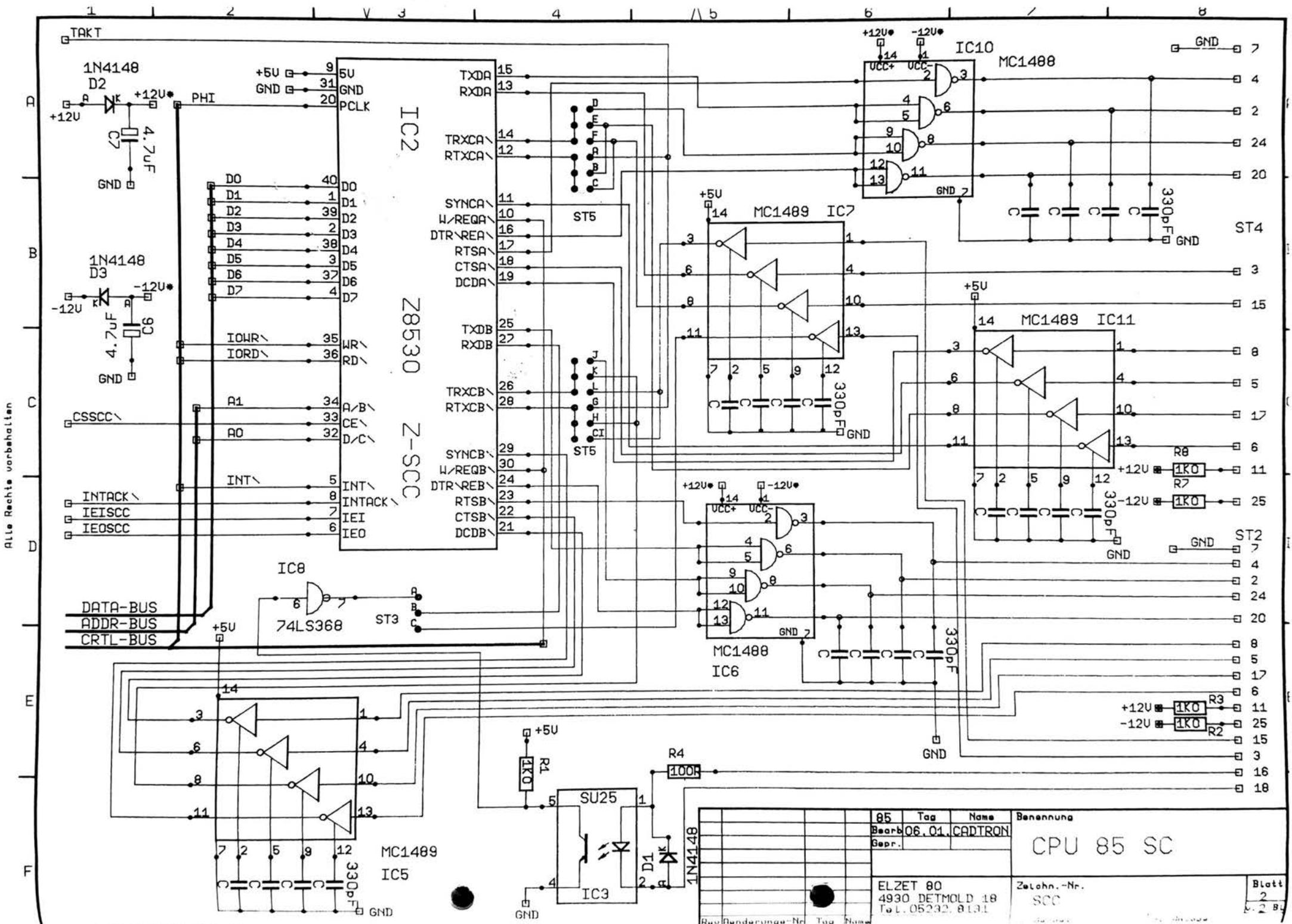

| 6.7 | Schaltbild.....             |

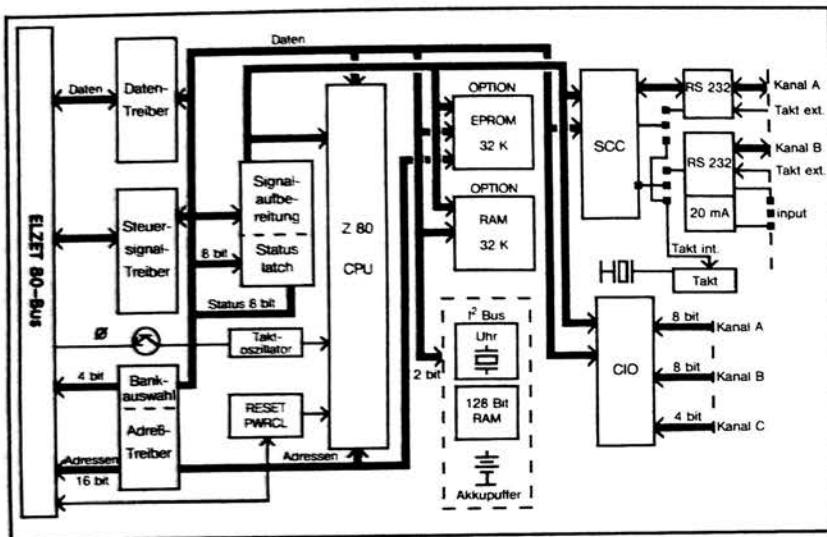

### 3.1 Blockschaltbild

=====

### 3.2 Funktion

=====

Die CPU85SC ist in zwei Teile geteilt, dem Hauptteil mit CPU, Speicher, Bankadressierung und I2C-Peripherie sowie dem E/A-Teil mit der Z8536 CIO (Parallelport/Zähler) und den zwei seriellen Schnittstellen RS232 (Z8530 SCC).

Die beiden Teillayouts beginnen in der Bezeichnung der Bauteile jeweils bei IC1, ST1 usw. Im Text wird zur Unterscheidung ein H für den Hauptteil und ein E für den E/A-Teil angehängt, also z.B. ST3E- A/B oder ST1H.

### 3.2 Funktion

---

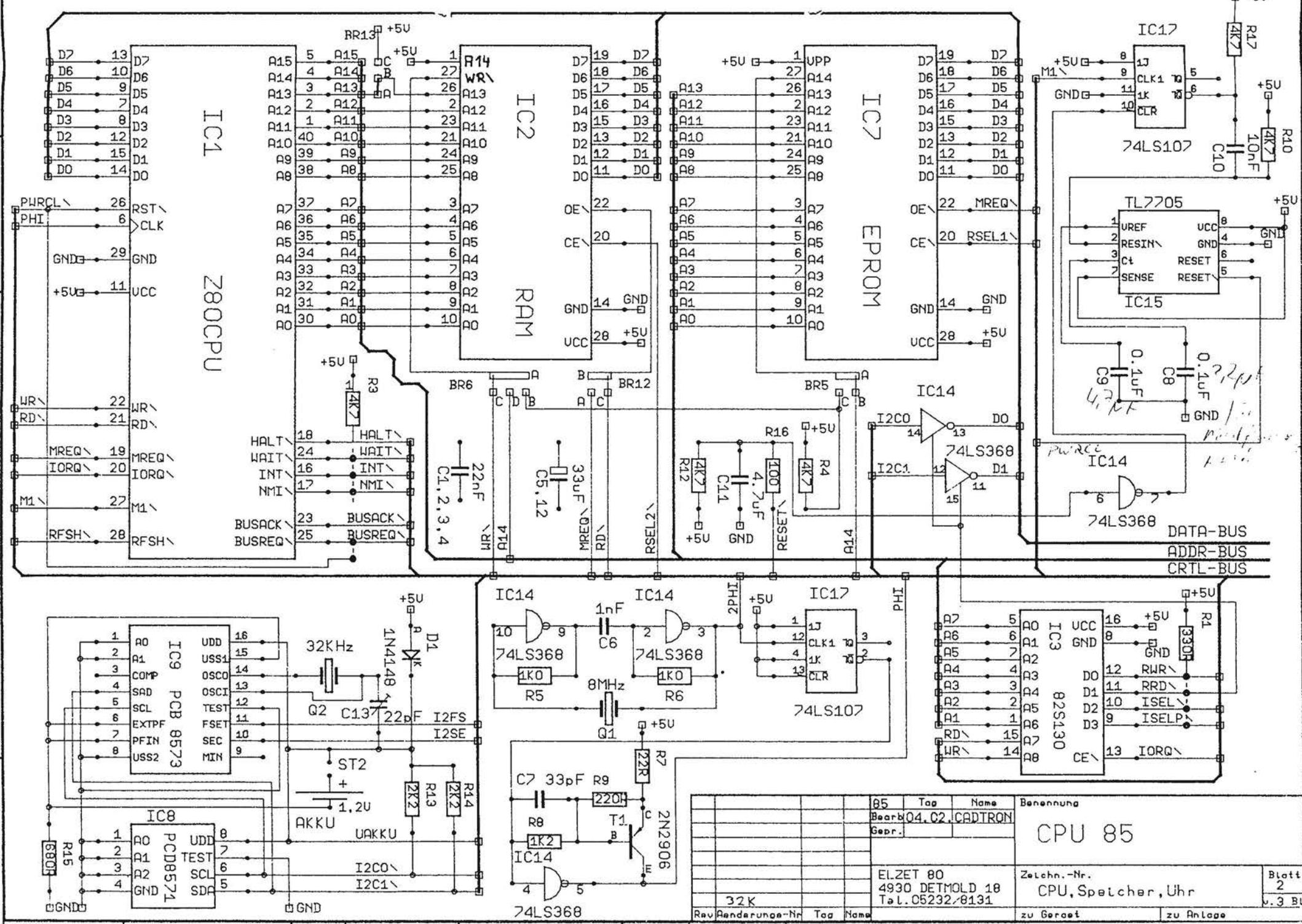

Dominierendes Element der CPU85SC ist selbstverständlich die Z80 CPU, die in verschiedenen Ausführungen bis 6 MHz Taktfrequenz betrieben werden kann. Standard ist die Z80A CPU für Frequenzen bis 4 MHz.

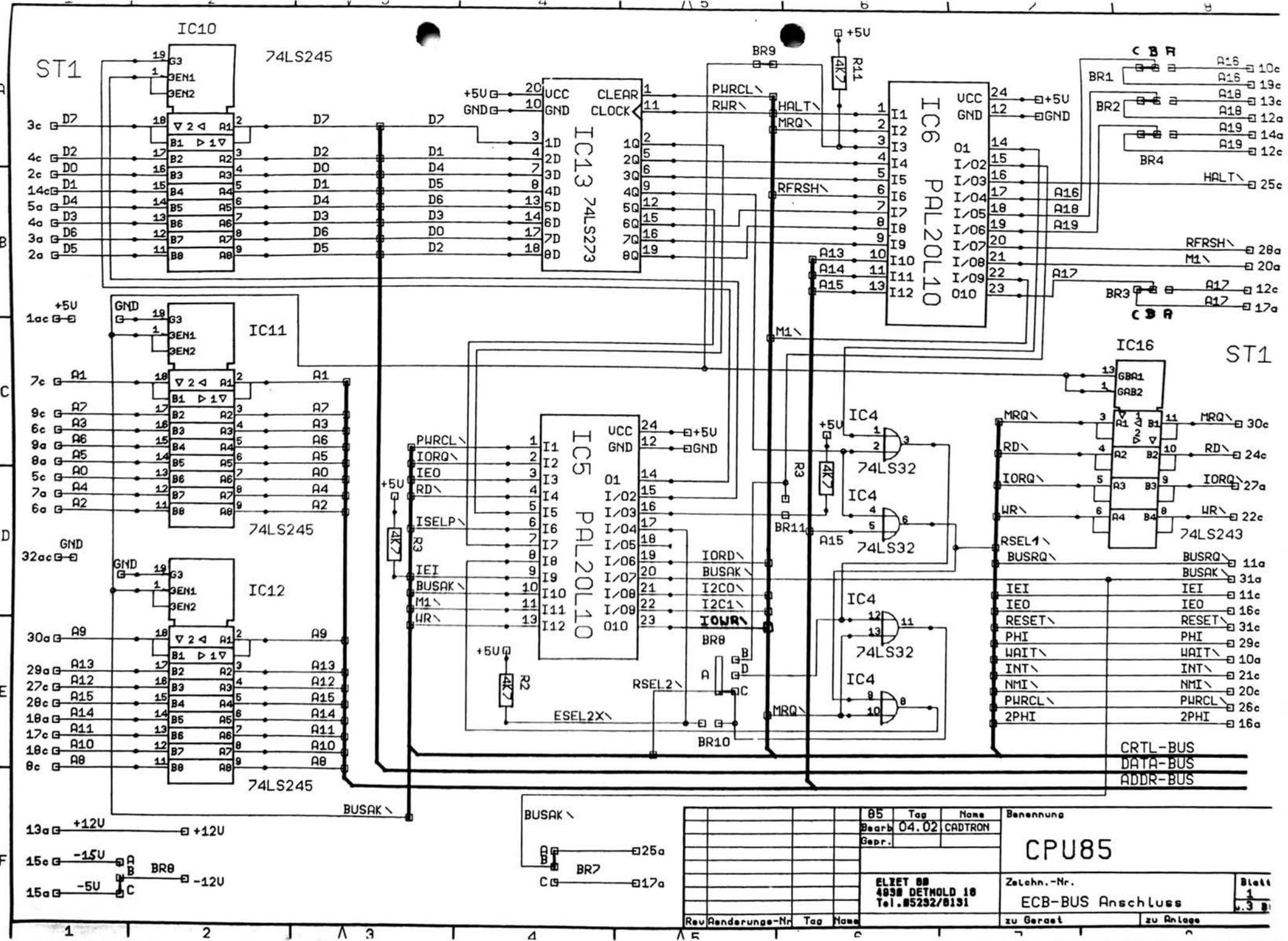

#### Buspufferung

Alle Adressen, Daten und Steuersignale werden über Treiber auf den Busanschluß geführt, die mit Lasten von über 40 LS-TTL-Einheiten beaufschlagt werden können.

#### Bussteuerung

Die Bussteuerung wird über ein hochintegriertes PAL vorgenommen. Die Richtung des Datenbustreibers wird darin abhängig gemacht vom Zustand der Interruptkette, der Art des Speicherzugriffs, intern oder extern, der Auswahl der internen E/A-Bausteine und natürlich der Steuersignale der CPU. Bei Freigabe eines externen Masters, also z.B. einer DMA, die auf dem Bus durch /BUSAK angezeigt wird, werden alle Treiber hochohmig geschaltet. Lediglich die Bankadressen können durch Öffnen von Jumper BR9 ständig freigegeben bleiben, wenn die DMA nur 16 Adressen bedient.

Auf das interne RAM und die internen E/As kann über eine DMA zugegriffen werden.

### 3.2 Funktion

---

#### Taktoszillator

Der CPU-Takt wird aus einem mit doppelter Taktfrequenz schwingendem Oszillator gewonnen. Die Grundfrequenz geht als 2PHI auf den Bus und kann dort z.B. von der Speicher-karte 1M zu Synchronisationszwecken verwandt werden. Die Nutzfrequenz wird in einer Treiberschaltung so aufbereitet, daß die Pegel NMOS-kompatibel sind.

#### Spannungsüberwachung

Die verwendeten NMOS- und LSTTL-Bausteine sind spezifiziert für eine Betriebsspannung von 5V  $\pm 5\%$ . Spannungen außerhalb dieser Toleranz führen zu undefinierten Betriebszuständen. Aus diesem Grund wird eine spezielle Spannungsüberwachungsschaltung eingesetzt, die bei einem Abfallen der Spannung unter die Toleranzgrenze RESET auslöst. RESET wird dann gehalten, bis die Sensorschaltung selbst in undefinierten Zustand geht, was bei max. 3V geschieht. 3V ist unkritisch, da bei dieser Spannung die Speicherschutzschaltungen z.B. auf der 16KCE oder der 64KCE bereits Schreibzugriffe gesperrt haben. Wenn die Spannung wieder über 3V ansteigt, wird zunächst RESET erzeugt. Bei Wiedereintritt der Betriebsspannung in den spezifizierten Bereich über 4,7V wird aus Sicherheitsgründen für eine Zeit von 1ms RESET beibehalten. Auch der RESET-Eingang vom Bus bzw. Taster wird über eine M1-Verknüpfung auf den Überwachungsbaustein geführt, so daß ein RESET-Signal definierter Länge erzeugt wird.

### 3.2 Funktion

---

#### E/A-Auswahl

Die Auswahl der internen E/A-Bausteine wird durch ein PROM vorgenommen. Die Startadresse des SCC auf 00, der CIO auf 04 und die Adresse des Universalregisters (0CH bis 0FH) sind daher festgelegt, wenn auch durch Bausteinwechsel änderbar.

#### Bank-Adreßerweiterung

Das Universalregister, das mit einer beliebigen der o.g. Adressen angesprochen wird, ist ein 8-Bit-Register, welches in 4 Bit die gewünschte Bank-Adresse speichert, zwei Bit für die Abschaltung der internen Speichersockel unter Programmsteuerung und die restlichen zwei Bit für das I2C-Interface benutzt. Die Bank-Adresse kann 16 Zustände annehmen (4 hoch 2), so daß der Z80 CPU 16 verschiedene Speicherbereiche zu 64K vorgelegt werden können, wodurch sich der Adreßbereich auf 1 MByte erhöht. Da die CPU nichts von der Bankadresse "merkt", muß dafür gesorgt werden, daß die Interrupttabelle bzw. die Sprungadressen für NMI oder Restart in einem Speicherbereich liegen, der für alle Banks gleich ist. Ein solcher Bereich wird Common-Bereich genannt, da der gefragte Speicher allen Banks gemeinsam ist.

Für die Arbeit mit dem CP/M-Betriebssystem unter Vektor-interrupt bietet es sich beispielsweise an, die oberen 4K aller Banks so zu behandeln, daß die CPU immer im Bereich F000H bis FFFFH der Bank 0 "landet". Dort kann man dann

### 3.2 Funktion

---

gefährlos die Vektortabelle und die Einsprünge der Interruptserviceroutinen ablegen. Solche Common-Bereiche sind vorhanden bei den Baugruppen FDC3, 256K, 1M und 64KCE.

#### I2C-Bus

Der I2C-Bus ist ein Zweidrahtsystem mit Takt und seriellen Daten, das senderseitig über zwei Bit des Universalregisters angesprochen wird. Empfangsseitig wird ein Bustreiber auf gleicher Adresse eingelesen.

Über den I2C-Bus werden die Uhr und das CMOS-RAM bedient. Die I2C-Leitungen können an der Übergabepunktreihe zum E/A-Teil abgegriffen werden, um evtuell weitere I2C-Bausteine - wie LCD-Treiber, A/D-Wandler uvm. - anzuschließen.

#### Speicher

Auf der CPU85SC kann für "kleine" Anwendungen der benötigte Speicher direkt untergebracht werden. Dazu stehen Sockel für ein Eprom bis 32KByte und für ein weiteres Eprom oder ein RAM bis 8 KByte zur Verfügung. Beide Sockel sind zusammen über eine Brücke oder über das Universalregister abschaltbar.

## 3.2 Funktion

---

### Internes Eprom

Der Sockel IC 7 nimmt Eproms zwischen 27128 und 27256 auf, entsprechend einer Kapazität von 16 bis 32 KByte. Das Eprom kann durch D5 des Universalregisters abgeschaltet werden. Startadresse des Eproms ist 0, so daß das Programm in diesem Eprom bei RESET oder Einschalten angesprochen wird.

Neben der Programmspeicher-Funktion für Geräte ohne weitere Speicherbaugruppen ist das Eprom auch als Bootlader verwendbar. Dazu wird das interne Eprom bei RESET angesprochen, während Speicher am Bus bis 7FFFH gesperrt sind. Nach der Initialisierungsfunktion kann das Eprom durch Software abgeschaltet werden. Diese Funktion erlaubt es insbesondere, ein Betriebssystem von Floppy oder über eine serielle Schnittstelle zu laden und dennoch nach dem Ladevorgang einen ab Adresse 0 startenden RAM-Bereich zur Verfügung zu stellen. Dazu muß einfach eine RAM-Baugruppe auf 0 adressiert werden. Zum Abschalten des Eproms wird beim Universalregister das für internen Speicher zugewiesene Bit auf High gesetzt. Ein Rücksetzen erfolgt durch Einschreiben eines Low oder automatisch durch RESET.

Soll im internen RAM oder EPROM Serviceroutinen für Vektor-interrupts untergebracht werden, die mit RETI beendet werden, so ist ein spezielles PAL einzusetzen. Mit dem "RETI"-PAL schickt die Bussteuerung nämlich die aus dem internen Eprom gelesenen Daten auf den Bus, bei gleichzeitiger Aktivierung von /RD. Dies dient der RETI-Erkennung durch die externen Z80 Peripheriebausteine.

### 3.2 Funktion

---

Mit dem Standard-PAL muß die RETI-Anweisung in externem Speicher stehen.

#### Internes Ram

In den Sockel IC2 paßt ein 8KByte-RAM des Typs 6264, 5565 o.ä. Dieses Ram läßt sich auf den Adressen 8000H - 9FFFH ansprechen und dient vor allem als Datenspeicher für kleine bis mittlere Steuerungsprogramme. Für dieses RAM werden die Bankadressen nicht dekodiert. Es ist auch möglich, hier ein 16K oder 32K Eprom einzusetzen, der praktische Nutzen scheint jedoch fraglich.

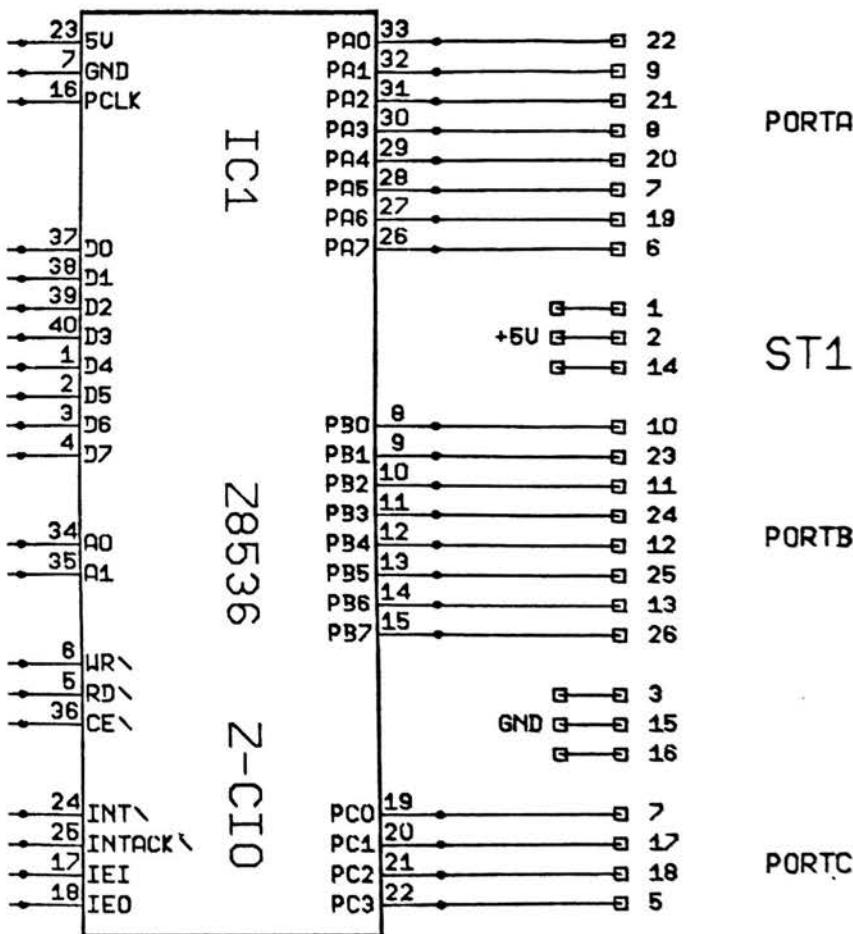

#### E/A-Bereich

Der E/A-Bereich ist ein separates Layout, welches an den CPU-Hauptteil über eine Signalpunktreihe etwa in Kartenmitte angebunden ist. Die CPU85SC ist bestückt mit den Z8000-Bausteinen SCC und CIO.

#### Serielle Schnittstellen

Für die zwei seriellen Schnittstellen wird die Z85 SCC (Serial Communications Controller Z8530) eingesetzt. Die SCC hat eine ähnliche Struktur wie die bekannte SIO (Z8440), ist jedoch erweitert um zwei programmierbare Baudratengeneratoren, eine Autoecho-Betriebsart, PLL für

### 3.2 Funktion

---

die Taktgewinnung und NRZ, NRZI bzw. FM-Codierung. Die SCC erlaubt Datenraten bis 1 MBit, die allerdings wegen der Limitierung der RS232-Spezifikation nicht ausgenutzt werden können.

Ansonsten findet man die bekannten Eigenschaften der SIO wieder:

3-Byte-Empfangs-FIFO, 1-Byte-Sende-FIFO, /WAIT- oder DMA-Synchronisation, 5 Quittungsleitungen (Modem) pro Kanal. Vier verschiedene bedingte Interruptvektoren können pro Kanal erzeugt werden. Die SCC verarbeitet in der asynchronen Betriebsart Zeichenlängen von 5 bis 8 Bit mit 1-2 Stopbits, beinhaltet Paritäts- und Rahmenprüfung, einen Taktvorteiler :1 bis :64 und schließlich Break-Erzeugung und -Erkennung.

Als synchrone Betriebsarten beherrscht die SCC Monosync, Bisync und SDLC. Die SCC übernimmt die gesamte Blockübertragung mit Erzeugung bzw. Erkennung von Sync/Flag-Bytes, CRC, Einfüge-Nullen und Sekundäradresse.

Die SCC ist in die Interrupt-Priorisierungskette des ELZET 80 Bus einzufügen, die CPU-Funktion ist unabhängig von der Plazierung. Kanal A hat die höhere Anforderungspriorität. Für Blocktransfers kann die WAIT-Synchronisation der SCC verwendet werden, da die W/REQ-Ausgänge entsprechend mit dem /WAIT-Eingang der CPU verbunden sind.

Weitere Eigenschaften und Programmierhinweise finden Sie im technischen Handbuch der SCC.

### 3.2 Funktion

---

#### Taktoszillator

Auf der CPU85SC wird der interne Quarzoszillator der SCC nicht ausgenutzt, da beim CPU-Taktoszillator noch eine Hälfte "abfiel" und die so gewonnenen Pins für Steuerleitungen und externe Takteingänge benutzt werden sollten.

Der externe Quarzoszillator arbeitet mit einer Frequenz von 3,6864 MHz. Diese Frequenz ermöglicht bei einem SCC-internen Teilerfaktor von 16 eine höchste Baudrate von 38400 Baud durch Programmierung des Teilerfaktors 1.

#### Schnittstellentreiber

Für die Pufferung der Schnittstellen werden Treiber der Typen 1488 und 1489 eingesetzt, die der CCITT-Spezifikation V28 und der EIA-Norm RS232C entsprechen. Für alle Treiber wird die Begrenzung der Anstiegszeit des Ausgangssignals mit externen Kondensatoren vorgenommen, alle Empfänger sind zur Störunterdrückung ebenfalls mit Kondensatoren ausgestattet. Alle an der SCC verfügbaren Modemsteuerleitungen werden getrieben herein- bzw. herausgeführt, also die Signale RTS, CTS, DTR, DCD und SYNC. Sowohl Sende- als auch Empfangstakt können von der Schnittstelle geliefert werden, auch kann der Ausgang des Baudratengenerators getrieben auf der Schnittstelle abgegriffen werden. Die verschiedenen Taktmöglichkeiten werden über ST5 eingestellt.

### 3.2 Funktion

---

Alle Schnittstellensignale sind an je einem 26-poligen Pfostenstecker pro Kanal abgreifbar. Dieser Pfostenstecker ist so verdrahtet, daß mit einem 25-poligen Flachkabel eine Normbuchse (ISO 2110, DB25S) korrekt angequetscht werden kann.

Für eventuell nötige Vorgabeeinstellungen an den Steuerleitungen oder für die Versorgung eines externen Treibers sind die Schnittstellen-Hilfsspannungen an der Steckerleiste über 1 KOhm Vorwiderstände abgreifbar.

Der Dateneingang des Kanal B ist umsteckbar (ST3 A/B) auf Optokoppler-Eingabe (20mA TTY). Diese dient vornehmlich als Eingang für die Tastatur ELZET 80 DIN-TAST.

#### Interruptbearbeitung

Die CPU85SC ist eingerichtet für den Z80-spezifischen Vektorinterrupt. Der Datenbus wird während der Interruptbestätigung (INTACK) so gesteuert, daß die CPU einen von der Peripherie abgegebenen Vektor einlesen kann. Die SCC hat gegenüber der CIO Vorrang bei der Interruptbedienung. Der Durchlauf durch die IEI/IEO-Kette wird über ein Gatter beschleunigt. IEI ist mit einem Pullup-Widerstand beschaltet.

#### Spannungsversorgung

Neben der Standard-Systemspannung von +5V benötigt die Baugruppe für die seriellen Schnittstellen noch die Hilfsspannungen +12V und -12V.

### 3.2 Funktion

---

Erfahrungsgemäß kommt ein RS232-Empfänger bei kurzen Kabeln auch mit -5V statt -12V aus. Daher wird die Verdrahtung werksseitig über den Busstift 15a eingestellt (-5V). Wenn -15V vorhanden ist, kann auch diese Spannung durch Umlöten einer Brücke auf der Leiterplattenunterseite verwendet werden.

### 3.3 Anschlüsse

#### 3.3 Anschlüsse

Die CPU85SC hat drei Peripherieanschlüsse, ST1E, ST2E und ST4E. Sie dienen der Verbindung externer Einheiten mit den beiden seriellen Schnittstellen der SCC und den Portanschlüssen der CIO.

ST1E ist der Anschluß für die CIO:

### 3.3 Anschlüsse

---

ST4E ist der Anschluß für Kanal A, ST2E für Kanal B. Die beiden Anschlüsse sind identisch bis auf die Zusatzanschlüsse für den Optokoppler bei ST2E.

Die Stiftnumerierung weicht ab von der üblichen Markierung bei Pfostenstekkern, um Übereinstimmung mit den Schnittstellen-Normverbindern zu erreichen. Auf der Folgeseite sind die Anschlüsse mit den entsprechenden SCC-Anschlußbezeichnungen versehen. Die Schnittstellentreiber dazwischen bleiben unbeachtet und müssen ggf. dem Schaltbild entnommen werden.

Bei einigen Anschlüssen sind Bezeichnungen wie ST5 b+e angegeben. Dies bedeutet, daß die Verbindung zur SCC über das Einstellfeld ST5 vorgenommen wird. Die Leitungen sind parallel an b und e geführt und können dort nach RTxC (b) bzw. TRxC (e) gebrückt werden. Die in der Steckerbelegung in Klammern stehenden Kleinbuchstaben beziehen sich auf die ST5-Einstellung für den Kanal B.

### 3.3 Anschlüsse

---

Steckerbelegung in der Adernreihenfolge des Flachkabels:

| DB25S     | 26p. Pfosten                              |

|-----------|-------------------------------------------|

|           | (o 26) nicht anschließbar-----            |

| 13 o----- | unbeschaltet-----                         |

|           | o 25----negative Hilfsspannung-----       |

| 12 o----- | unbeschaltet-----                         |

|           | o 24----ST5 d (TRxC) Ausgang-----         |

| 11 o----- | positive Hilfsspannung-----               |

|           | o 23----unbeschaltet-----                 |

| 10 o----- | unbeschaltet-----                         |

|           | o 22----unbeschaltet-----                 |

| 9 o-----  | unbeschaltet-----                         |

|           | o 21----unbeschaltet-----                 |

| 8 o-----  | DCD-Eingang-----                          |

|           | o 20----DTR-Ausgang-----                  |

| 7 o-----  | Signalmasse-----                          |

|           | o 19----unbeschaltet-----                 |

| 6 o-----  | SYNC-Eingang (DSR)-----                   |

|           | o 18----nur ST2E:-20mA-Eingang-----       |

| 5 o-----  | CTS-Eingang-----                          |

|           | o 17----ST5 b+e(h+k) Takteingang-----     |

| 4 o-----  | RTS-Ausgang-----                          |

|           | o 16----nur ST2E:+20mA-Eingang-----       |

| 3 o-----  | RxD-Dateneingang (bei ST2E über ST3)----- |

|           | o 15----ST5 c+f(i+1) Takteingang-----     |

| 2 o-----  | TxD-Datenausgang-----                     |

|           | o 14----unbeschaltet-----                 |

| 1 o-----  | unbeschaltet-----                         |

Sockel I (IC7)

27128 (EPROM 16K \* 8)

27256 (EPROM 32K \* 8)

BR5 AC

BR5 AB

Sockel II (IC2)

27128 (EPROM 16K \* 8)

BR6 - AB

BR8 - AD

BR10 - geschlossen

BR12 - AB

BR13 - AB

27256 (EPROM 32K \* 8)

BR6 - AD

BR8 - AD

BR10 - geschlossen

BR12 - AB

BR13 - AB

---

4364 (RAM 8K \* 8)

(internes RAM)

BR6 - AC

BR8 - AC

BR10 - geschlossen

BR12 - BC

BR13 - ~~AC~~

4364 (RAM 8K \* 8)

(Common Memory)

BR6 - AC

BR8 - AB BC

BR10 - geschlossen ✓

BR11 - geschlossen ✓

BR12 - BC ✓

BR13 - BC ✓

### 3.4 Einstellmöglichkeiten

---

#### 3.4 Einstellmöglichkeiten

---

Es folgt eine Übersicht über die Einstellmöglichkeiten bei der ELZET 80 CPU85SC. Stecker und Brücken im Hauptteil erhalten den Suffix H, entsprechend wird an Bezeichnungen im E/A-Teil ein E angehängt.

##### a) Steckbrücken

|      |                         |

|------|-------------------------|

| ST2H | Akku                    |

| ST3E | 20mA/RS232 für SCC RxDB |

| ST5E | Taktzuordnung SCC       |

##### b) Lötbrücken

|       |                                       |

|-------|---------------------------------------|

| BR1H  | A16                                   |

| BR2H  | A18                                   |

| BR3H  | A17                                   |

| BR4H  | A19                                   |

| BR5H  | Pin 27 (A14) Speichersockel I (IC7)   |

| BR6H  | Pin 27 (A14) Speichersockel II (IC2)  |

| BR7H  | BAO                                   |

| BR8H  | Auswahlsignal für Speichersockel II   |

| BR9H  | Bankadresse 3-State bei DMA           |

| BR10H | Speichersockel II aktivieren          |

| BR11H | Sockel II Common memory (zus.mit BR8) |

| BR12H | OE für Sockel II mit MREQ oder RD     |

| BR13H | Pin 26 Speichersockel II (A13/CS2)    |

| BR14  | Negative Hilfsspannung RS232 -5/-15V  |

### 3.4 Einstellmöglichkeiten

---

#### c) Software

00-03H      SCC Register

04-07H      CIO Register

0FH          Universalregister

#### d) Bausteinwechsel

IC6          PAL20L10 Adreßdekodierung interner Speicher

IC3          PROM512x4 Adreßdekodierung interner E/A

Q1H          8MHz/12MHz Taktfrequenz CPU

Q1E          3,6864 MHz Taktfrequenz SCC

### 3.4.1 Steck- und Lötbrücken

#### ST2H - Akku

Wenn ST2H gesteckt ist, ist der Akku eingeschaltet, Uhr und CMOS-Ram erhalten die Standby-Versorgung. ~~Stellen der Uhr geogen werden~~

#### ST3E - SCC RxDB

Mit ST3E wird ausgewählt, ob die serielle Schnittstelle Kanal B eingangsseitig von der 20mA Stromschleife getrieben wird oder von der normalen RS232-Leitung.

A-B entspricht 20mA      BC entspricht RS232

#### ST5E - Taktzuordnung für die SCC

Die SCC kann intern und extern getaktet werden, der interne Takt kann auch nach draußen abgegeben werden. Die Zuweisung erfolgt über ST5.

- a      RTxCA      3,6864 MHz von Taktoszillator

- b      RTxCA      Takt von ST4, Pin 17

- c      RTxCA      Takt von ST4, Pin 15

- d      TRxCA      Takt auf ST4, Pin 24

- e      TRxCA      Takt von ST4, Pin 17

- f      TRxCA      Takt von ST4, Pin 15

### 3.4 Einstellmöglichkeiten

---

Fortsetzung ST5E:

- g RTxCB 3,6864 MHz von Taktoszillator

- h RTxCB Takt von ST2, Pin 17

- i RTxCB Takt von ST2, Pin 15

- j TRxCB Takt auf ST2, Pin 24

- k TRxCB Takt von ST2, Pin 17

- l TRxCB Takt von ST2, Pin 15

#### Lötbrücken

BR1H - A16, BR2H - A18, BR3H - A17, BR4H - A19

Mit den Lötbrücken 1 bis 4 wird die Ausgabe der Bankadresse zwischen der Erweiterung des ECB-Bus nach ELZET 80 -Art und der nach KONTRON-Art umgeschaltet.

~~A-B verbunden KONTRON, B-C verbunden ELZET 80~~

Auslieferung mit der Voreinstellung für ELZET 80 -Bus.

BR5H - Pin 27 (A14) Speichersocket I (IC7)

Für 27128 wird ein Pullup an Pin 27 des Sockel I gelegt, für 27256 A14 des Prozessors.

A-B = 27256 , B-C = 27128

### 3.4 Einstellmöglichkeiten

---

BR6H Pin 27 (A14) Speichersockel II (IC2)

Für 27128 wird ein Pullup an Pin 27 des Sockel I gelegt, für 27256 A14 des Prozessors, für RAMs das Signal /WR.

A-B = 27128, A-C = RAM, A-D = 27256

BR7H - BAO

Mit der Lötbrücke 7 wird die Ausgabe des BAO-Signals (BUSAK) zwischen der Erweiterung des ECB-Bus nach ELZET 80 -Art und der nach KONTRON-Art umgeschaltet.

A-B = BAO auf 25a (ELZET 80), B-C = BAO auf 17a (KONTRON)

BR8H Auswahlsignal für Speichersockel II

BR8 ist einer der Zugriffsauswahljumper für Speichersockel II. Es kann gewählt werden zwischen internem Common Memory (arbeitet nicht zusammen mit VIDEO80, ist aber bei Einsatz von ELZET 80 -Speicherkarten auch unnötig), zwischen RAM und EPROM.

A-B Comm. Memory, A-C RAM, A-D Eprom

### 3.4 Einstellmöglichkeiten

---

#### Das Universalregister

Auf der Adresse 0F kann das Universalregister als Schreib- und Leseregister angesprochen werden.

Die einzelnen Bits haben folgende Funktion:

##### Schreiben:

|    |                                              |

|----|----------------------------------------------|

| D0 | Adreßerweiterung A16                         |

| D1 | Adreßerweiterung A17                         |

| D2 | Adreßerweiterung A18                         |

| D3 | Adreßerweiterung A19                         |

| D4 | Common Memory auswählen (0 = selektiert)     |

| D5 | Internen Speicher auswählen (0 = selektiert) |

| D6 | I2C Anschluß Daten                           |

| D7 | I2C Anschluß Takt                            |

##### Lesen:

|       |                    |

|-------|--------------------|

| D0    | I2C Anschluß Daten |

| D1    | I2C Anschluß Takt  |

| D2-D7 | nicht verwendet    |

Ansteuerprogramm fuer I2C Bus Peripherie auf der CPU855C /E

```

; +                               ; Adresse Systemlatch

SYSLAT      EQU      00FH

; Bitbelegung I2C Bus

CLOCK_BIT_I  EQU      0

DATA_BIT_I   EQU      1

CLOCK_BIT_O  EQU      7

DATA_BIT_O   EQU      6

; Adressbytes I2C Bus

I2CCLK      EQU      11010000B

I2CRAM      EQU      10100000B

; Subadressbytes I2C Bus

HOUR        EQU      00000000B

MINUTE      EQU      00000001B

DAY         EQU      00000010B

MONTH       EQU      00000011B

```

Ansteuerprogramm fuer I2C Bus Peripherie auf der CPU85SC /E

```

+-----+

| Unterprogramm: : UTILITY Funktionen I2C Bus

+-----+

| Funktion:      : Durchfuehren primitiver Operationen auf

|                   : dem I2C Bus.

+-----+

| Input:         :

|                   :

+-----+

| Output:        :

|                   :

+-----+

| Register:      :

|                   :

+-----+

```

```

;+-----+

; | Unterprogramm: | CLK/DAT 0/1

;+-----+

; | Funktion: | Setzen der CLK oder DAT

; | | Signale auf entsprechenden

; | | Pegel.

;+-----+

```

```

CLK0:    PUSH    AF

PUSH    HL

DI

LD      HL, (SYSPTR)

LD      A, (HL)

SET    CLOCK_BIT_0, A

OUT    (SYSLAT), A

LD      (HL), A

EI

POP    HL

POP    AF

RET

```

```

CLK1:    PUSH    AF

PUSH    HL

DI

LD      HL, (SYSPTR)

LD      A, (HL)

RES    CLOCK_BIT_0, A

OUT    (SYSLAT), A

LD      (HL), A

EI

```

Ansteuerprogramm fuer I2C Bus Peripherie auf der CPU85SC /E

```

CLK1_0:    IN     A, (SYSLAT)

BIT    CLOCK_BIT_I, A

JR    NZ, CLK1_0

POP   HL

POP   AF

RET

```

```

DATO:      PUSH AF

PUSH HL

DI

LD   HL, (SYSPTR)

LD   A, (HL)

SET  DATA_BIT_0_A

OUT  (SYSLAT), A

LD   (HL), A

EI

POP  HL

POP  AF

RET

```

```

DAT1:      PUSH AF

PUSH HL

DI

LD  HL, (SYSPTR)

LD  A, (HL)

RES DATA_BIT_0, A

OUT (SYSLAT), A

LD  (HL), A

EI

DAT1_0:    IN   A, (SYSLAT)

BIT DATA_BIT_1, A

JR  NZ, DAT1_0

POP HL

POP AF

RET

```

```

; +-----+

; | Unterprogramm: | I2CSTA

; +-----+

; | Funktion: | Generiere Startbedingung

; | | auf I2C Bus.

; +-----+

I2CSTA:  CALL    DAT1

CALL    CLK1

CALL    DAT0

CALL    CLK0

RET

```

```

; +-----+

; | Unterprogramm: | I2CSTO

; +-----+

; | Funktion: | Generiere Stopbedingung

; | | auf I2C Bus.

; +-----+

```

## Ansteuerprogramm fuer I2C Bus Peripherie auf der CPU85SC /E

```

CALL CLK1

CALL DAT1

RET

; +-----+

; : Unterprogramm: I2CSND

; : Funktion: Sende das im A-Register

; : uebergebene Datenbyte.

; +-----+

I2CSND: PUSH BC

LD B,B

RLCA

JP C,I2CSND_0

CALL DAT0

JR I2CSND_2

CALL DAT1

CALL CLK1

CALL CLK0

DJNZ I2CSND_1

POP BC

RET

; +-----+

; : Unterprogramm: I2CRCV

; : Funktion: Empfange ein Datenbyte vom

; : I2C Bus im A-Register.

; +-----+

I2CRCV: PUSH BC

PUSH HL

LD B,B

LD HL,(SYSPTR)

DI

LD A,(HL)

RES DATA_BIT_0,A

OUT (SYSLAT),A

LD (HL),A

EI

CALL CLK1

IN A,(SYSLAT)

BIT DATA_BIT_I,A

SCF

JR Z,I2CRCV_1

CCF

I2CRCV_1: RL C

CALL CLK0

DJNZ I2CRCV_0

LD A,C

POP HL

POP BC

RET

```

## Ansteuerprogramm fuer I2C Bus Peripherie auf der CPU85SC /E

```

; +-----+

; : Unterprogramm: I2CSAK

; : Funktion: Sende die ACK Bedingung

; : auf den I2C Bus.

; +-----+

I2CSAK: CALL DAT0

CALL CLK1

CALL CLK0

RET

; +-----+

; : Unterprogramm: I2CNAK

; : Funktion: Sende die I2C Bus NAK Be-

; : dingung.

; +-----+

I2CSNA: CALL DAT1

CALL CLK1

CALL CLK0

RET

; +-----+

; : Unterprogramm: I2CGAK

; : Funktion: Lese das ACK Signal vom

; : I2C Bus. Der Buspegel wird

; : im A-Register (0 = 00H und

; : 1 = OFFH) uebergeben.

; +-----+

I2CGAK: PUSH HL

LD HL,(SYSPTR)

DI

LD A,(HL)

RES DATA_BIT_0,A

OUT (SYSLAT),A

LD (HL),A

EI

PDP HL

CALL CLK1

IN A,(SYSLAT)

CALL CLK0

BIT DATA_BIT_I,A

LD A,0

RET NZ

DEC A

RET

```

## Ansteuerprogramm fuer I2C Bus Peripherie auf der CPU85SC /E

```

; +-----+

; : Unterprogramm: I2CWR

; : Funktion: Der I2C Bus wird auf der

; : Adresse H, Subadresse L

; : angesprochen und der In-

; : halt des A-Registers aus-

; : gegeben.

; +-----+

I2CWR: PUSH BC

PUSH DE

LD B,A

CALL I2CSTA

LD A,H

AND 1111110B

CALL I2CSND

CALL I2CGAK

AND A

JP NZ,I2CERR

LD A,L

CALL I2CSND

CALL I2CGAK

AND A

JP NZ,I2CERR

LD A,B

CALL I2CSND

CALL I2CGAK

AND A

JR NZ,I2CERR

CALL I2CSTO

POP DE

POP BC

RET

; +-----+

; : Unterprogramm: I2CRD

; : Funktion: Der I2C Bus wird auf der

; : Adresse H, Subadresse L

; : angesprochen. Der eingele-

; : sene Wert wird im A-Re-

; : gister uebergeben.

; +-----+

I2CRD: PUSH BC

PUSH DE

CALL I2CSTA

LD A,H

AND 1111110B

CALL I2CSND

CALL I2CGAK

AND A

JR NZ,I2CERR

LD A,L

CALL I2CSND

CALL I2CGAK

AND A

JR NZ,I2CERR

```

Ansteuerprogramm fuer I2C Bus Peripherie auf der CPU85SC /E

```

CALL  I2CSTA

LD   A,H

OR   00000001B

CALL  I2CSND

CALL  I2C8AK

AND  A

JR   NZ,I2CERR

CALL  I2CRCV

PUSH  AF

CALL  I2CSNA

CALL  I2CSTO

POP   AF

POP   DE

POP   BC

RET

; +-----+

; : Unterprogramm: I2CERR

; : Funktion: Der I2C Buszyklus wird ab-

; : gebrochen und das A-Re-

; : gister auf 0 gesetzt.

; +-----+

```

```

I2CERR: CALL  I2CSTO

POP   DE

POP   BC

XOR   A

RET

```

```

; +-----+

; : Unterprogramm: CLKSET

; : Funktion: Setzen der Echtzeituhr auf das uebergebene

; : Datum und die uebergebene Uhrzeit.

; : Input: TOS Zeiger auf Datums- und Uhrzeitfeld.

; : In diesem Feld sind die einzelnen

; : Felder BCD codiert. Je 2 BCD Ziffern

; : sind in einem Byte angeordnet.

; : MM/DD/HH/MM

; : (Monat, Tag, Stunde und Minute)

; : Output:

; : Register: Alle Registerinhalte ausser AF werden ge-

; : rettet.

; +-----+

```

```

CLKSET: PUSH  BC

PUSH  DE

PUSH  HL

LD   HL,B

ADD  HL,SP

LD   E,(HL)

INC   HL

LD   D,(HL)

```

Ansteuerprogramm fuer I2C Bus Peripherie auf der CPU85SC /E

```

; Schreibe Monat

LD   A,(DE)

INC  DE

LD   HL,MONTH + (I2CCLK SHL 8)

CALL  I2CWR

; Schreibe Tag

LD   A,(DE)

INC  DE

LD   HL,DAY + (I2CCLK SHL 8)

CALL  I2CWR

; Schreibe Stunde

LD   A,(DE)

INC  DE

LD   HL,HOUR + (I2CCLK SHL 8)

CALL  I2CWR

; Schreibe Minute

LD   A,(DE)

INC  DE

LD   HL,MINUTE + (I2CCLK SHL 8)

CALL  I2CWR

; Unterprogrammaussprung

POP  HL

POP  DE

POP  BC

RET

```

```

; +-----+

; : Unterprogramm: CLKGET

; : Funktion: Auslesen der Echtzeituhr in den ueberge-

; : benen Datums- und Uhrzeitblock.

; : Input: TOS Zeiger auf Parameterblock.

; : Output: TOS Zeiger auf Datums- und Uhrzeitfeld.

; : In diesem Feld sind die einzelnen

; : Felder BCD codiert. Je 2 BCD Ziffern

; : sind in einem Byte angeordnet.

; : MM/DD/HH/MM

; : (Monat, Tag, Stunde und Minute)

; : Register: Alle Registerinhalte ausser AF werden ge-

; : rettet.

; +-----+

```

```

CLKGET: PUSH  BC

PUSH  DE

PUSH  HL

LD   HL,B

ADD  HL,SP

LD   E,(HL)

```

Ansteuerprogramm fuer I2C Bus Peripherie auf der CPU85SC /E

```

LD   E,(HL)

INC  HL

LD   D,(HL)

; Lese Startadresse

LD   A,(DE)

LD   C,A

INC  DE

; Lese Byte laenge

LD   A,(DE)

LD   B,A

INC  DE

; Schreibe I2C Ram

LD   H,I2CRAM

LD   L,C

LD   A,(DE)

INC  DE

CALL  I2CWR

INC  L

DJNZ  RAMSET_0, RAMSET_0

; Unterprogrammaussprung

POP  HL

POP  DE

POP  BC

RET

```

```

; +-----+

; : Unterprogramm: RAMGET

; : Funktion: Auslesen des akkugepufferten I2C Rams in

; : den Parameterblock.

; : Input: TOS Zeiger auf Parameterblock. In den er-

; : sten beiden Bytes sind Startadresse

; : und Laenge im I2C Ram definiert. Es

; : folgt der Speicherplatz zum Auslesen

; : des I2C Rams.

; : Output: TOS+2 Ausgelesene Datenbytes des I2C Ram.

; : Register: Alle Registerinhalte ausser AF werden ge-

; : rettet.

; +-----+

```

```

RAMGET: PUSH  BC

PUSH  DE

PUSH  HL

LD   HL,B

ADD  HL,SP

LD   E,(HL)

INC  HL

LD   D,(HL)

```

(C) 1984 by ELZET 80 Mikrocomputer Detmold

(C) 1984 by ELZET 80 Mikrocomputer Detmold

(C) 1984 by ELZET 80 Mikrocomputer Detmold

Ansteuerprogramm fuer I2C Bus Peripherie auf der CPU855C /E

```

INC   HL

LD   D, (HL)

; Lese Monat

LD   HL, MONTH + (I2CCLK SHL 8)

CALL  I2CRD

LD   (DE), A

INC  DE

; Lese Tag

LD   HL, DAY + (I2CCLK SHL 8)

CALL  I2CRD

LD   (DE), A

INC  DE

; Lese Stunde

LD   HL, HOUR + (I2CCLK SHL 8)

CALL  I2CRD

LD   (DE), A

INC  DE

; Lese Minute

LD   HL, MINUTE + (I2CCLK SHL 8)

CALL  I2CRD

LD   (DE), A

INC  DE

; Unterprogrammaussprung

POP  HL

POP  DE

POP  BC

RET

```

```

; Unterprogramm: : RAMSET

; Funktion:   : Setzen des akkugepufferten RAM Bausteins

;               : mit einer Bytesequenz.

; Input:      : TOS Zeiger auf Parameterblock. In den er-

;               : sten beiden Bytes sind Startadresse

;               : und Laenge im I2C Ram definiert. Es

;               : folgt die festgelegte Anzahl an Da-

;               : tenbytes.

; Output:     :

; Register:   : Alle Registerinhalte ausser AF werden ge-

;               : rettet.

```

```

RAMSET:  PUSH  BC

PUSH  DE

PUSH  HL

LD    HL, 8

ADD   HL, SP

```

Ansteuerprogramm fuer I2C Bus Peripherie auf der CPU855C /E

```

; Lese Startadresse

LD   A, (DE)

LD   C, A

INC  DE

; Lese Bytelaenge

LD   A, (DE)

LD   B, A

INC  DE

; Lese I2C Ram

LD   H, I2CRAM

LD   L, C

CALL  I2CRD

LD   (DE), A

INC  DE

INC  L

DJNZ  RAMGET_0

; Unterprogrammaussprung

POP  HL

POP  DE

POP  BC

RET

```

```

; : Unterprogramm: : I2CINI

; : Funktion:   : Initialisieren des I2C Bus Softwareinter-

; :               : face.

; : Input:      : TOS Adresse eines Datenbytes, das den ak-

;               : tuellen Inhalt des Systemlatches

;               : angibt. (2 Byte)

; : Output:     :

; : Register:   : Alle Registerinhalte werden bewahrt.

```

```

I2CINI:  PUSH  HL

LD    HL, 4

ADD   HL, SP

LD    A, (HL)

INC   HL

LD    H, (HL)

LD    L, A

; HL-Register = Adresse Latchwert

LD    (SYSPTR), HL

; Unterprogrammende

POP  HL

RET

```

Ansteuerprogramm fuer I2C Bus Peripherie auf der CPU855C /E

```

; +-----+

; | Datenbereich

; +-----+

SYSPTR  DW  0

END

```

1 Stückliste 1. Auflage 80

1 Adress 1. Wittenberghäuser Str. 80

1 Stückliste 1. 1 Z80CPU

1 Lfd. 1 Nr. 1 Symbol 1/18 1 Typ

TELECOM GMBH & CO. KG

4730 DETHOLD 18

1 Bauteil

CPUPSSC/H

Seite 1 1

|   |    |       |                     |              |

|---|----|-------|---------------------|--------------|

| 1 | 1  | IC 1  | Z80CPU              | INT/BAUSTEIN |

| 1 | 2  | IC 2  | EPROM/RAM           | INT/BAUSTEIN |

| 1 | 3  | IC 3  | 82S130              | INT/BAUSTEIN |

| 1 | 4  | IC 4  | 74LS32              | INT/BAUSTEIN |

| 1 | 5  | IC 5  | P6L20L10            | INT/BAUSTEIN |

| 1 | 6  | IC 6  | P6L20L10            | INT/BAUSTEIN |

| 1 | 7  | IC 7  | EPROM               | INT/BAUSTEIN |

| 1 | 8  | IC 8  | PCB8571             | INT/BAUSTEIN |

| 1 | 9  | IC 9  | PCB8573             | INT/BAUSTEIN |

| 1 | 10 | IC 10 | 74LS245             | INT/BAUSTEIN |

| 1 | 11 | IC 11 | 74LS245             | INT/BAUSTEIN |

| 1 | 12 | IC 12 | 74LS245             | INT/BAUSTEIN |

| 1 | 13 | IC 13 | 74LS273             | INT/BAUSTEIN |

| 1 | 14 | IC 14 | 74LS368             | INT/BAUSTEIN |

| 1 | 15 | IC 15 | 7L7705              | INT/BAUSTEIN |

| 1 | 16 | IC 16 | 74LS243             | INT/BAUSTEIN |

| 1 | 17 | IC 17 | 74LS107             | INT/BAUSTEIN |

| 1 | 18 | T 1   | 2N2906              | TRANSISTOR   |

| 1 | 19 | P 1   | 1N4148              | DIODE        |

| 1 | 20 | R 1   | SIL-ARRAY 5x470 Ohm | WIDERSTAND   |

| 1 | 21 | R 2   | 4K7                 | WIDERSTAND   |

| 1 | 22 | R 3   | SIL-ARRAY 7x4K7     | WIDERSTAND   |

| 1 | 23 | R 4   | 4K7                 | WIDERSTAND   |

| 1 | 24 | R 5   | 1K0                 | WIDERSTAND   |

| 1 | 25 | R 6   | 1K0                 | WIDERSTAND   |

| 1 | 26 | R 7   | 22 OHM              | WIDERSTAND   |

| 1 | 27 | R 8   | 1K2                 | WIDERSTAND   |

| 1 | 28 | R 9   | 220 OHM             | WIDERSTAND   |

| 1 | 29 | R 10  | 4K7                 | WIDERSTAND   |

| 1 | 30 | R 11  | 4K7                 | WIDERSTAND   |

| 1 | 31 | R 12  | 4K7                 | WIDERSTAND   |

| 1 | 32 | R 13  | 2K2                 | WIDERSTAND   |

| 1 | 33 | R 14  | 2K2                 | WIDERSTAND   |

| 1 | 34 | R 15  | 680 OHM             | WIDERSTAND   |

| 1 | 35 | R 16  | 100 OHM             | WIDERSTAND   |

| 1 | 36 | C 1   | 22 nF Keram.        | KONDENSATOR  |

Firma : ELZET 80

F. Adr. : Wilhelm-Meillies-Str. 88

Stückliste f. : LZ80CPU

Lfd. f. Nr. f. Symbol/Nr. f. Typ

Mikrocomputer GmbH & Co.KG

4930 Detmold 18

f. Bauteil

CPUS5-SC/E

Seite f. 1

|   |    |       |                  |              |

|---|----|-------|------------------|--------------|

| 1 | 1  | IC 1  | Z85C10           | INT/BAUSTEIN |

| 1 | 2  | IC 2  | Z85SCC           | INT/BAUSTEIN |

| 1 | 3  | IC 3  | SU 25            | INT/BAUSTEIN |

| 1 | 4  | IC 4  | 74LS32           | INT/BAUSTEIN |

| 1 | 5  | IC 5  | 1489             | INT/BAUSTEIN |

| 1 | 6  | IC 6  | 1488             | INT/BAUSTEIN |

| 1 | 7  | IC 7  | 1489             | INT/BAUSTEIN |

| 1 | 8  | IC 8  | 47LS368          | INT/BAUSTEIN |

| 1 | 9  | IC 9  | 74LS11           | INT/BAUSTEIN |

| 1 | 10 | IC 10 | 1488             | INT/BAUSTEIN |

| 1 | 11 | IC 11 | 1489             | INT/BAUSTEIN |

| 1 | 12 | D 1   | 1N4148           | DIODE        |

| 1 | 13 | D 2   | 1N4148           | DIODE        |

| 1 | 14 | D 3   | 1N4148           | DIODE        |

| 1 | 15 | R 1   | 1K               | WIDERSTAND   |

| 1 | 16 | R 2   | 1K               | WIDERSTAND   |

| 1 | 17 | R 3   | 1K               | WIDERSTAND   |

| 1 | 18 | R 4   | 100 OHM          | WIDERSTAND   |

| 1 | 19 | R 5   | 1K               | WIDERSTAND   |

| 1 | 20 | R 6   | 1K               | WIDERSTAND   |

| 1 | 21 | R 7   | 1K               | WIDERSTAND   |

| 1 | 22 | R 8   | 1K               | WIDERSTAND   |

| 1 | 23 | C 1   | +5V Entk.        | KONDENSATOR  |

| 1 | 24 | C 2   | +5V Entk.        | KONDENSATOR  |

| 1 | 25 | C 3   | +5V Entk.        | KONDENSATOR  |

| 1 | 26 | C 4   | 1 nF             | KONDENSATOR  |

| 1 | 27 | C 5   | +5V Entk.        | KONDENSATOR  |

| 1 | 28 | C 6   | 4,4 uF Tantal    | KONDENSATOR  |

| 1 | 29 | C 7   | 4,7 uF Tantal    | KONDENSATOR  |

| 1 | 30 | C 8   | ***              | KONDENSATOR  |

| 1 | 31 | C 9   | 20 nF 390 pF     | KONDENSATOR  |

| 1 | 32 | C 10  | Kennzeichn. "B"  | KONDENSATOR  |

| 1 | 33 | C 11  | ***              | KONDENSATOR  |

| 1 | 34 | G 1   | 240 MHz 36864 Hz | QUARZ        |

| 1 | 35 | ST 1  | 13*2 pol Stift   | STECKER      |

| 1 | 36 | ST 2  | 13*2 pol Stift   | STECKER      |

| 1 | 37 | ST 3  | 3*1 pol Stift    | STECKER      |

| 1 | 38 | ST 4  | 13*2 pol Stift   | STECKER      |

| 1 | 39 | ST 5  | 12*2 pol Stift   | STECKER      |

Feld 7 7774 00

Adr. 1 Wohllebenstrasse 56 7000

Streckleiste 1 1 2000VU

Feld 1 Nr. 1 300017/5 1 Tor

FAKULTÄT FÜR INGENIEURWISSENSCHAFTEN

4930 DORTMUND 18

1 Bauteil

CPU&SC1

Seite 1 2

|   |    |      |                   |             |

|---|----|------|-------------------|-------------|

| 1 | 37 | C 2  | 22 nF Kondensator | KONDENSATOR |

| 1 | 38 | C 3  | 22 nF Kondensator | KONDENSATOR |

| 1 | 39 | C 4  | 22 nF Kondensator | KONDENSATOR |

| 1 | 40 | C 5  | 4,7 uF 250V Ta    | KONDENSATOR |

| 1 | 41 | C 6  | 1 uF              | KONDENSATOR |

| 1 | 42 | C 7  | 33 nF             | KONDENSATOR |

| 1 | 43 | C 8  | 0,1 uF 300V Ta    | KONDENSATOR |

| 1 | 44 | C 9  | 0,1 uF 300V Ta    | KONDENSATOR |

| 1 | 45 | C 10 | 10 nF Kondensator | KONDENSATOR |

| 1 | 46 | C 11 | 4,7 uF 250V Ta    | KONDENSATOR |

| 1 | 47 | C 12 | 33 uF 10V Ta      | KONDENSATOR |

| 1 | 48 | C 13 | 22 nF Trimmer     | KONDENSATOR |

| 1 | 49 | C 14 | XXXXXXXXXXXXXX    | KONDENSATOR |

| 1 | 50 | C 15 | 1 STCK. +5V Entk. | KONDENSATOR |

| 1 | 51 | C 16 | Berechn. "B"      | KONDENSATOR |

| 1 | 52 | C 17 | XXXXXXXXXXXXXX    | KONDENSATOR |

| 1 | 53 | Q 1  | 8 KHz             | QUARZ       |

| 1 | 54 | Q 2  | 32 KHz            | QUARZ       |

| 1 | 55 | S1 1 | 64 pol. VU-Leiste | STECKER     |

ST2 2x1 pol. STIFT

HUKU 1,2V

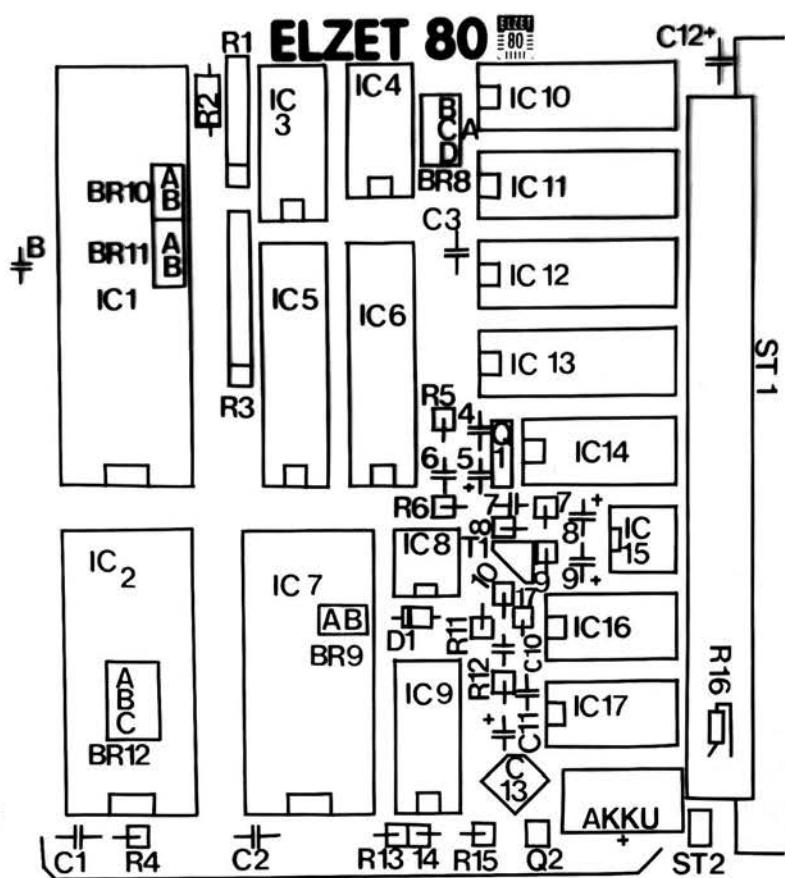

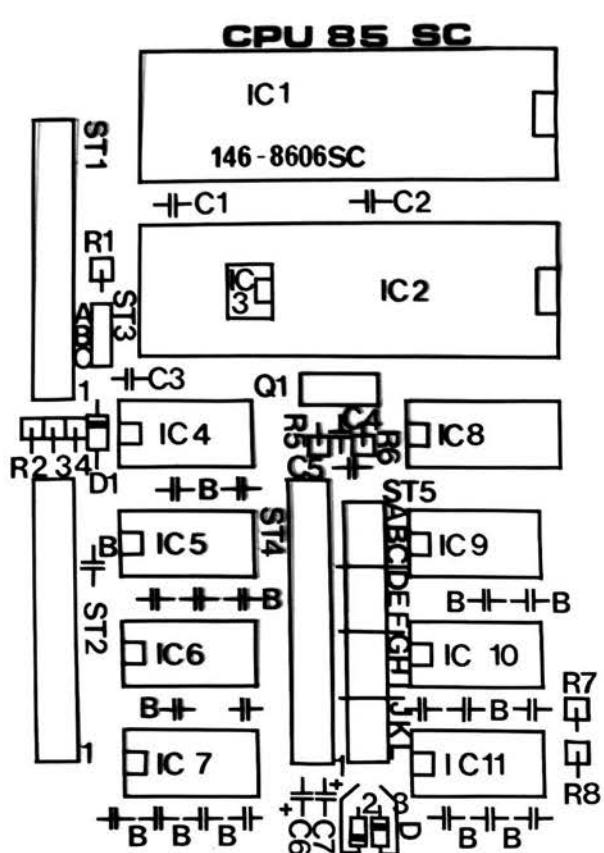

CPU 85 SC

146 - 8606 SC

3-5-89/1

Solder stop marks

Bestückungsseite

Component Side

|                  |     |      |                                                         |               |                              |                                |

|------------------|-----|------|---------------------------------------------------------|---------------|------------------------------|--------------------------------|

|                  |     |      | <b>85</b>                                               | Tag           | Name                         | Benennung<br><br><b>CPU85E</b> |

|                  |     |      | Bearb.                                                  | <b>05.02.</b> | CADTRON                      |                                |

|                  |     |      | Gepr.                                                   |               |                              |                                |

|                  |     |      |                                                         |               |                              |                                |

|                  |     |      | <b>ELZET 88<br/>4890 DETMOLD 18<br/>Tel. 05292/8191</b> |               | Zetchn.-Nr.                  | Blatt                          |

|                  |     |      |                                                         |               | <b>Uebergabeanschluessel</b> | 3                              |

|                  |     |      |                                                         |               |                              | U.3 BL                         |

| Revidierungs-Nr. | Tag | Name |                                                         |               | zu Gerät                     | zu Anlage                      |

## Centronics-Druckeranschluß für CPU85SC

---

Diese Anwenderinformation Version 1.0 beschreibt die Leiterplatte mit der Filmnummer 152-8620.

---

C P U 8 5 S C A

---

Die CPU85SCA stellt der CPU85SC eine Centronics-kompatible Druckerschnittstelle, einen Piezobeeper und 3 freie Ein- oder Ausgabebits zur Verfügung.

Der Anschluß geschieht über ein direkt anquetschbares 26-poliges Flachbandkabel an die CIO der CPU-Karte.

Ein Treiber in Z80-Assembler (aus dem CP/M+ Bios) ist im Anhang abgedruckt, vorhandene Treiber für unsere PRINT/XXX-Karten können bei Änderung der Portadressen und Einfügen einer Initialisierung verwendet werden.

# ELZET 80

Mikrocomputer GmbH & Co. KG

Wilhelm-Mellies-Straße 88

D-4930 Detmold 18

Tel. 05232-8131 · Tx. 931473 elzet d

25.7.86

ELZET 80

## Centronics-Druckeranschluß für CPU85SC

---

### Übersicht der Funktionen:

CIO Port A: Daten Centronics

CIO Port B: Steuerleitungen Centronics

CIO Port C: C0: Beeper

C1-C3: frei

Counter/Timer 1: Verteiler für Sekundeninterrupt

Counter/Timer 2: Sekundeninterrupt

Counter/Timer 3: Timer 1KHz für Beeper

### Stückliste:

|      |                           |

|------|---------------------------|

| IC 1 | 74LS541                   |

| IC 2 | 74LS541                   |

| C 1  | 22uF/16V                  |

| B    | 100nF/50V Keramik         |

| B    | 100nF/50V Keramik         |

| ST 1 | Stiftleiste 2x26-polig    |

| ST 2 | Stiftleiste 1x5-polig     |

| ST 3 | JD 36 (Centronics-Buchse) |

| LS   | Piezobeeper QMB111P       |

0,5m 26-pol Flachbandkabel, beidseitig Quetscher

Filmnummer: 152-8620