# ECB-CPUS

ECB-Prozessor-Baugruppe für die Serienanwendung

in Steuerungsrechnern

Unterspannungsüberwachung mit automatischem RESET

Erzeugung der Bank-Adressen für 1 MByte Adreßraum

Internes EPROM bis 32 KByte

schaltbar als Betriebssystem-lader (boot)

internes RAM 8 KByte

zwei serielle Schnittstellen

Mikrocomputer GmbH & Co. KG

---

Für Ihren Bedarf bevorraten wir die Handbücher der ZILOG Z85XX-Bauelemente. Wir geben die Handbücher zum Preise von 15,-DM ab.

## Anwenderhandbuch ELZET 80 CPU/S

---

1

### INHALTSVERZEICHNIS

#### 2 ÜBERSICHT

|     |                                      |      |

|-----|--------------------------------------|------|

| 2.1 | Aufbau.....                          | S. 3 |

| 2.2 | Einsatzbereich.....                  | S. 4 |

| 2.3 | Ausführungen und Modifikationen..... | S. 5 |

#### 3 HARDWARE

|       |                                         |       |

|-------|-----------------------------------------|-------|

| 3.1   | Blockschaltbild.....                    | S. 6  |

| 3.2   | Funktion.....                           | S. 6  |

| 3.3   | Anschlüsse.....                         | S. 15 |

| 3.4   | Einstellmöglichkeiten.....              | S. 17 |

| 3.4.1 | Steck- und Lötbrücken.....              | S. 18 |

| 3.4.2 | Einstellmögl. durch Betriebssoftware..  | S. 23 |

| 3.4.3 | Einstellmögl. durch Bauelementewechsel  | S. 27 |

| 3.5   | Beispiele für die Einstellung.....      | S. 28 |

| 3.5.1 | Beispieleinstellung für CP/M-Betrieb..  | S. 28 |

| 3.5.2 | Beispieleinst.f. Steuerungsapplikation. | S. 29 |

#### 4 SOFTWARE

|       |                                   |       |

|-------|-----------------------------------|-------|

| 4.1   | Allgemeines.....                  | S. 30 |

| 4.2   | Initialisierung.....              | S. 31 |

| 4.3   | Applikationsbeispiel.....         | S. 33 |

| 4.4   | Betrieb mit Standardsoftware..... | S. 36 |

| 4.4.1 | Der Bootlademonitor "SSM".....    | S. 36 |

| 4.4.2 | Das CP/M-Betriebssystem.....      | S. 37 |

| 4.4.3 | MSR-BASIC.....                    | S. 38 |

## Anwenderhandbuch ELZET 80 CPU/S

---

### 5 INBETRIEBNAHME

|     |                                      |       |

|-----|--------------------------------------|-------|

| 5.1 | Voraussetzungen für den Betrieb..... | S. 39 |

| 5.2 | Art und Umfang des Testbetriebs..... | S. 41 |

| 5.3 | Aufbau der Testumgebung.....         | S. 42 |

| 5.4 | Testablauf.....                      | S. 46 |

| 5.5 | Diagnosemöglichkeiten.....           | S. 46 |

### 6 TECHNISCHE UNTERLAGEN

|     |                             |        |

|-----|-----------------------------|--------|

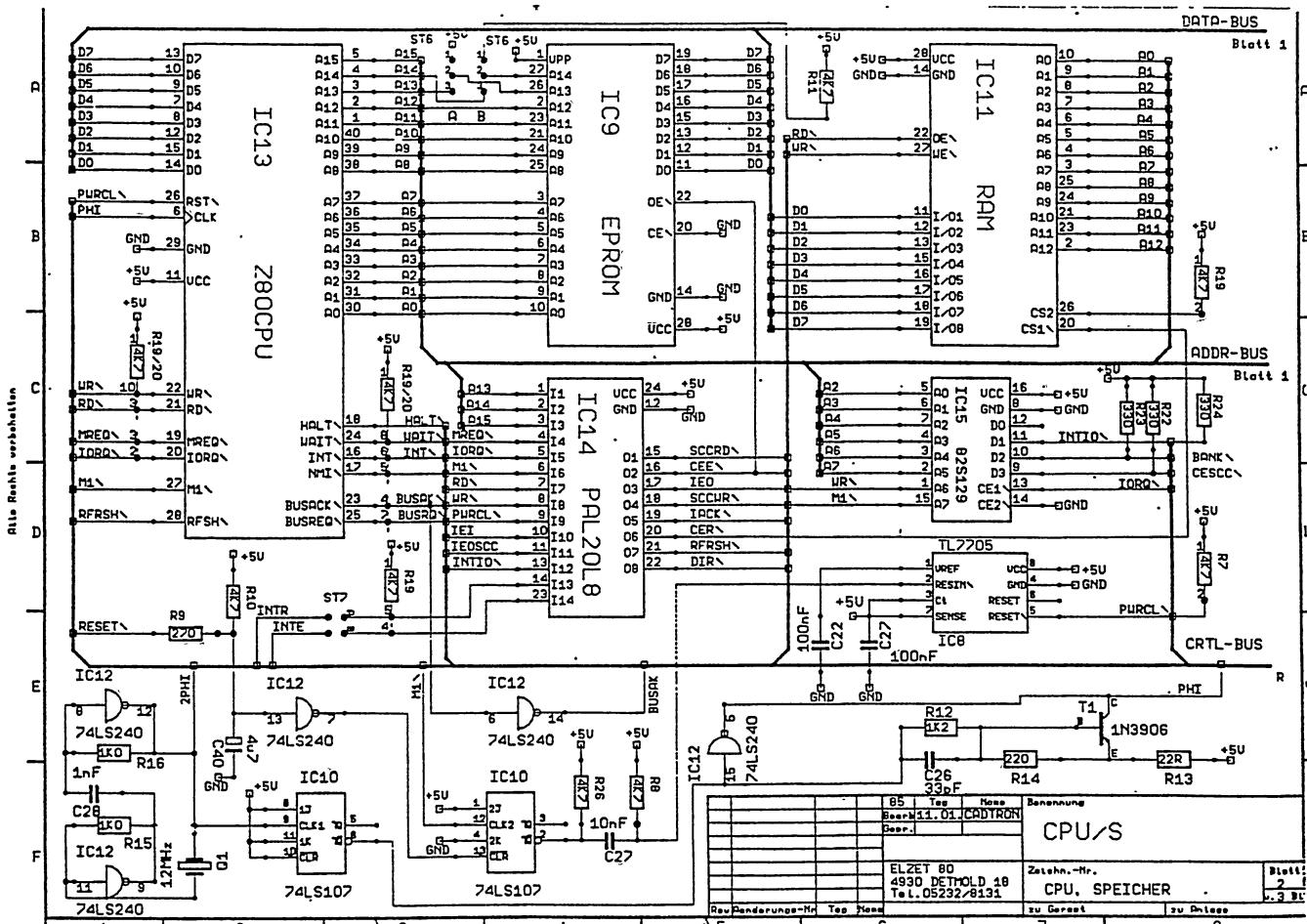

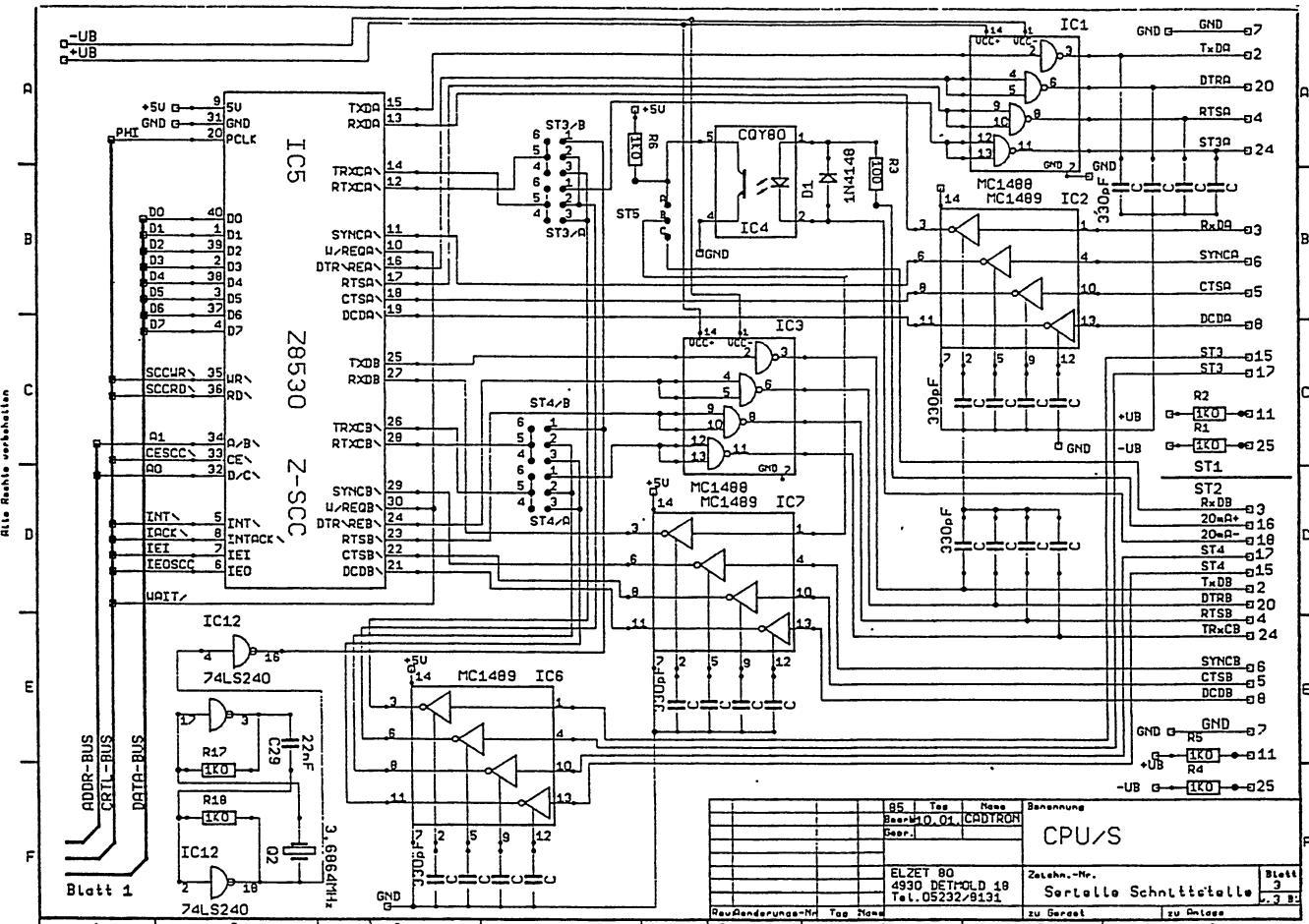

| 6.1 | Schaltungsbeschreibung..... | S. 48  |

| 6.2 | Technische Daten.....       | S. 50  |

| 6.3 | Busteckerbelegung.....      | S. 54  |

| 6.4 | Stückliste.....             | S. 55  |

| 6.5 | Bestückungsplan.....        | S. 57  |

| 6.6 | Datenblattauszüge.....      | S. 58  |

| 6.7 | Schaltbild.....             | Anhang |

## 2 Übersicht

---

2

### ÜBERSICHT

#### 2.1 Aufbau

=====

Die ELZET 80 CPU/S ist eine einfache, aber moderne Prozessorbaugruppe mit der Z80A (4 MHz) bzw. Z80B CPU (6 MHz). Neben der Funktion als ECB-Hauptprozessor bietet die Karte einen eingebauten Speicherbereich für Programme (Eeprom bis 32KByte) und Daten (Ram 8KByte).

Zwei serielle Schnittstellen nach RS232/V24 sind mit dem Baustein Z8530 SCC realisiert. Die SCC ermöglicht alle asynchronen Betriebsarten sowie Mono-/Bi-Sync und SDLC. Neben den Datenleitungen sind alle Modemsignale und die Takteleitungen getrieben. Die Baudrate ist programmierbar im Bereich von unter 10 bis 38400 Baud bei Teilerfaktor 16.

Ein Baudratengenerator kann auch als 10ms Interruptgeber programmiert werden, wenn der Takt vom anderen Kanal übernommen wird.

Die von den ELZET 80 -Speicherbaugruppen dekodierten Bankadressen (A16-A19) zur Erweiterung des Speicherbereichs von 64KByte auf 1MByte werden über ein DMA-fähiges Ausgabeport auf der Baugruppe erzeugt.

Definierte Betriebsbedingungen bei Unterspannung werden durch eine Sensorschaltung mit RESET-Ausgang ermöglicht.

## 2.2 Einsatzbereich

---

### 2.2 Einsatzbereich

---

Die ELZET 80 CPU/S ist ideal geeignet für eine Unterrechnereinheit, beispielsweise für eine Regelung, eine Versuchssteuerung oder einen Prüfautomaten. Sie deckt Anwendungen ab, bei denen ein Einplatinencomputer - z.B. aus der MOPS-Serie - nicht ausreicht. Das ist der Fall bei sehr vielen E/As (24 Relais oder acht 12-Bit D/As) oder ungewöhnlichen Peripherieanschlüssen (Grafikdisplay, isolierte A/Ds).

Die CPU/S verfügt für diese Anwendungen über die normalerweise nötige Speicherkapazität, verhindert jedoch keinesfalls Erweiterungen durch Speicherbaugruppen am Bus. Hierfür werden sogar die Bankadressen erzeugt, wenn der 64K-Bereich überschritten werden soll. Im Speicherbereich der Baugruppe selbst kann z.B. ein BASIC-Interpreter oder ein Systemmonitor untergebracht werden, im gleichen Eprom ist dann auch noch Platz für das Anwenderprogramm. Alternativ kann im Download-Verfahren das Betriebsprogramm vom Hauptrechner in das RAM der CPU/S übertragen werden, wo es dann ausgeführt wird.

Auch die immer notwendigen seriellen Schnittstellen sind auf der Baugruppe integriert, z.B. für den Anschluß eines Diagnoseterminals oder die Verbindung zum übergeordneten Rechner, für Peripheriegeräte wie Drucker, Plotter, intelligente Meßgeräte o.ä. Alle Schnittstellensignale sind modemfähig gepuffert. Für einen Kanal ist alternativ ein

## 2.2 Einsatzbereich

---

20mA-TTY-Eingang zum Anschluß der ELZET 80 DIN-TAST vorhanden.

Die Baugruppe ist aufgrund des konservativ großflächigen Layouts, der umfangreichen Buspufferung (41 getriebene Signale) und der Unterspannungserkennung mit definierter RESET-Zeit ideal geeignet für kritische Anwendungen.

Die CPU/S eignet sich zum Aufbau von Computern mit Floppy-Disk, sie wird entsprechend von CP/M+ unterstützt. Allerdings fehlt eine akkugepufferte Uhr, wie sie beispielsweise auf der CPU85SC vorhanden ist.

## 2.3 Ausführungen und Modifikationen

---

Die CPU/S wird in einer Version ohne serielle Schnittstellen als CPU/S1 ausgeliefert.

### 3 Hardware

#### 3

#### HARDWARE

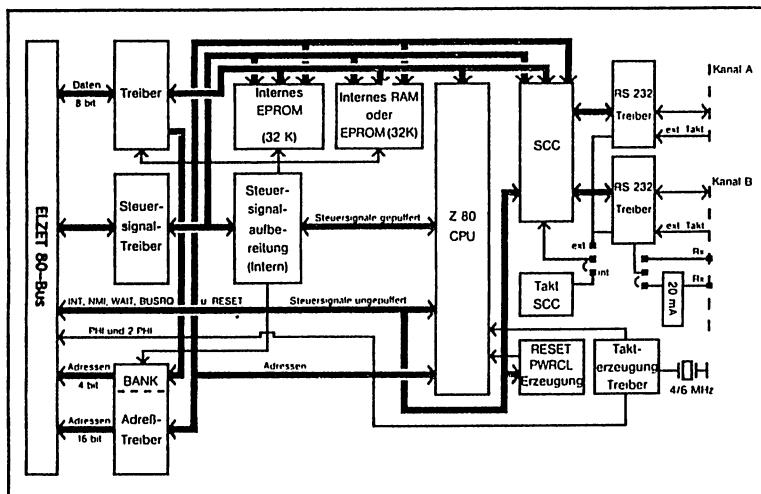

##### 3.1 Blockschaltbild

=====

##### 3.2 Funktion

=====

Dominierendes Element der CPU/S ist selbstverständlich die Z80 CPU, die in verschiedenen Ausführungen bis 6 MHz Taktfrequenz betrieben werden kann. Standard ist die Z80A CPU für Frequenzen bis 4 MHz.

### 3.2 Funktion

---

#### Buspufferung

Alle Adressen, Daten und Steuersignale werden über Treiber auf den Busanschluß geführt, die mit Lasten von über 40 LSTTL-Einheiten beaufschlagt werden können.

#### Bussteuerung

Die Bussteuerung wird über ein hochintegriertes PAL vorgenommen. Die Richtung des Datenbustreibers wird darin abhängig gemacht vom Zustand der Interruptkette, der Art des Speicherzugriffs, intern oder extern, der Auswahl der SIO als E/A-Baustein und natürlich der Steuersignale der CPU. Bei Freigabe eines externen Masters, also z.B. einer DMA, die auf dem Bus durch /BUSAK angezeigt wird, werden alle Treiber hochohmig geschaltet. Lediglich die Bankadressen können durch Öffnen von Jumper BR8 ständig freigegeben bleiben, wenn die DMA nur 16 Adressen bedient.

Auf das interne RAM und die internen E/As kann nicht über eine DMA zugegriffen werden. Da diese unübliche Anwendung hohe Kosten verursacht hätte, wurde darauf verzichtet.

#### Taktoszillator

Der CPU-Takt wird aus einem mit doppelter Taktfrequenz schwingendem Oszillatator gewonnen. Die Grundfrequenz geht als 2PHI auf den Bus und kann dort z.B. von der Speicher-Karte 1M zu Synchronisationszwecken verwandt werden. Die Nutzfrequenz wird in einer Treiberschaltung so aufbereitet,

### 3.2 Funktion

---

daß die Pegel NMOS-kompatibel sind.

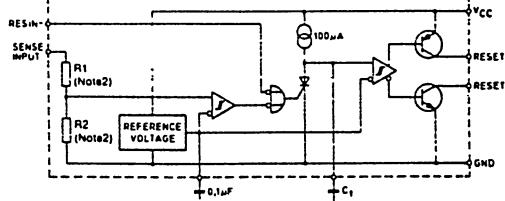

#### Spannungsüberwachung

Die verwendeten NMOS- und LSSTL-Bausteine sind spezifiziert für eine Betriebsspannung von 5V  $\pm 5\%$ . Spannungen außerhalb dieser Toleranz führen zu undefinierten Betriebszuständen. Aus diesem Grund wird eine spezielle Spannungsüberwachungsschaltung eingesetzt, die bei einem Abfallen der Spannung unter die Toleranzgrenze RESET auslöst. RESET wird dann gehalten, bis die Sensorschaltung selbst in undefinierten Zustand geht, was bei max. 3V geschieht. 3V ist unkritisch, da bei dieser Spannung die Speicherschutzschaltungen z.B. auf der 16KCE oder der 64KCE bereits Schreibzugriffe gesperrt haben. Wenn die Spannung wieder über 3V ansteigt, wird zunächst RESET erzeugt. Bei Wiedereintritt der Betriebsspannung in den spezifizierten Bereich über 4,7V wird aus Sicherheitsgründen für eine Zeit von 1ms RESET beibehalten. Auch der RESET-Eingang vom Bus bzw. Taster wird über eine M1-Verknüpfung auf den Überwachungsbaustein geführt, so daß ein RESET-Signal definierter Länge erzeugt wird.

#### E/A-Auswahl

Die Auswahl der internen E/A-Bausteine wird durch ein PROM vorgenommen. Die Startadresse des SCC auf 00 und die Adresse des Bankports (0CH bis 0FH) sind daher festgelegt, wenn auch durch Bausteinwechsel änderbar.

### 3.2 Funktion

---

#### Bank-Adresserweiterung

Das Bank-Port, welches mit einer beliebigen der o.g. Adressen angesprochen wird, ist ein 8-Bit-Register, welches in 4 Bit die gewünschte Bank-Adresse speichert und zwei Bit für die Abschaltung der internen Speichersockel unter Programmsteuerung benutzt. Die Bank-Adresse kann 16 Zustände annehmen (4 hoch 2), so daß der Z80 CPU 16 verschiedene Speicherbereiche zu 64K vorgelegt werden können, wodurch sich der Adressbereich auf 1 MByte erhöht. Da die CPU nichts von der Bankadresse "merkt", muß dafür gesorgt werden, daß die Interrupttabelle bzw. die Sprungadressen für NMI oder Restart in einem Speicherbereich liegen, der für alle Banks gleich ist. Ein solcher Bereich wird Common-Bereich genannt, da der gefragte Speicher allen Banks gemeinsam ist. Für die Arbeit mit dem CP/M-Betriebssystem unter Vektorinterrupt bietet es sich beispielsweise an, die oberen 4K aller Banks so zu behandeln, daß die CPU immer im Bereich F000H bis FFFFH in der Bank 0 "landet". Dort kann man dann gefahrlos die Vektortabelle und die Einsprünge der Interruptserviceroutinen ablegen. Solche Common-Bereiche sind vorhanden bei den Baugruppen FDC3, 256K, 1M und 64KCE.

#### Speicher

Auf der CPU/S kann für "kleine" Anwendungen der benötigte Speicher direkt untergebracht werden. Dazu stehen Sockel für ein Eprom bis 32KByte und für ein RAM von 8KByte zur Verfügung. Beide Sockel sind fest oder per Programm abschaltbar.

### 3.2 Funktion

---

#### Internes Eprom

Der Sockel IC 9 nimmt Eproms zwischen 2732 und 27256 auf, entsprechend einer Kapazität von 4 bis 32 KByte. Das Eprom kann durch Entfernen der Brücke ST7b abgeschaltet werden. Startadresse des Eproms ist 0, so daß das Programm in diesem Eprom bei RESET oder Einschalten angesprochen wird.

Neben der Programmspeicher-Funktion für Geräte ohne weitere Speicherbaugruppen ist das Eprom auch als Bootlader verwendbar. Dazu wird das interne Eprom bei RESET angesprochen, während Speicher am Bus bis 7FFFH gesperrt sind. Nach der Initialisierungsfunktion kann das Eprom durch Software abgeschaltet werden. Diese Funktion erlaubt es insbesondere, ein Betriebssystem von Floppy oder über eine serielle Schnittstelle zu laden und dennoch nach dem Ladevorgang einen ab Adresse 0 startenden RAM-Bereich zur Verfügung zu stellen. Dazu muß einfach eine RAM-Baugruppe auf 0 adressiert werden. Zum Abschalten des Eproms wird beim Bankport das für das Eprom zugewiesene Bit auf High gesetzt. Ein Rücksetzen erfolgt durch Einschreiben eines Low oder automatisch durch RESET.

Es ist günstig, die adressgleiche externe RAM-Baugruppe bei Zugriff auf das interne Eprom zu sperren, damit die Bustreiber nicht gegeneinander arbeiten. Die CPU schickt nämlich die aus dem internen Eprom gelesenen Daten auf den Bus, bei gleichzeitiger Aktivierung von /RD. Dies dient der RETI-Erkennung durch die externen Z80 Peripheriebausteine.

### 3.2 Funktion

---

Die CPU/S stellt das Signal /Boot active bei Adressierung des internen Eproms auf dem Bus zur Verfügung.

#### Internes Ram

In den Sockel IC11 passt ein 8KByte-RAM des Typs 6264, 5565 o.ä. Dieses Ram lässt sich auf den Adressen 8000H - 9FFFH ansprechen und dient vor allem als Datenspeicher für kleine bis mittlere Steuerungsprogramme. Für dieses RAM werden die Bankadressen nicht dekodiert, eine Meldeleitung an externe Einheiten wie die /Boot-active-Leitung beim internen Eprom existiert nicht.

#### Serielle Schnittstellen

Für die zwei seriellen Schnittstellen wird die Z85 SCC (Serial Communications Controller Z8530) eingesetzt. Die SCC hat eine ähnliche Struktur wie die bekannte SIO (Z8440), ist jedoch erweitert um zwei programmierbare Baudratengeneratoren, eine Autoecho-Betriebsart, PLL für die Taktgewinnung und NRZ, NRZI bzw. FM-Codierung. Die SCC erlaubt Datenraten bis 1 MBit, die allerdings wegen der Limitierung der RS232-Spezifikation nicht ausgenutzt werden können.

Ansonsten findet man die bekannten Eigenschaften der SIO wieder:

3-Byte-Empfangs-FIFO, 1-Byte-Sende-FIFO, /WAIT- oder DMA-Synchronisation, 5 Quittungsleitungen (Modem) pro Kanal. Vier verschiedene bedingte Interruptvektoren können pro

### 3.2 Funktion

---

Kanal erzeugt werden. Die SCC verarbeitet in der asynchronen Betriebsart Zeichenlängen von 5 bis 8 Bit mit 1-2 Stopbits, beinhaltet Paritäts- und Rahmenprüfung, einen Taktvorteiler :1 bis :64 und schließlich Break-Erzeugung und -Erkennung.

Als synchrone Betriebsarten beherrscht die SCC Monosync, Bisync und SDLC. Die SCC übernimmt die gesamte Blockübertragung mit Erzeugung bzw. Erkennung von Sync/Flag-Bytes, CRC, Einfüge-Nullen und Sekundäradresse.

Die SCC ist in die Interrupt-Priorisierungskette des ELZET 80 Bus einzufügen, die CPU-Funktion ist unabhängig von der Plazierung. Kanal A hat die höhere Anforderungspriorität. Für Blocktransfers kann die WAIT-Synchronisation der SCC verwendet werden, da die W/REQ-Ausgänge entsprechend mit dem /WAIT-Eingang der CPU verbunden sind.

Weitere Eigenschaften und Programmierhinweise finden Sie im technischen Handbuch der SCC.

#### Taktoszillator

Auf der CPU/S wird der interne Quarzoszillator der SCC nicht ausgenutzt, da beim CPU-Taktoszillator noch eine Hälfte "abfiel" und die so gewonnenen Pins für Steuerleitungen und externe Takteingänge benutzt werden sollten.

Der externe Quarzoszillator arbeitet mit einer Frequenz von 3,6864 MHz. Diese Frequenz ermöglicht bei einem SCC-

### **3.2 Funktion**

---

internen Teilerfaktor von 16 eine höchste Baudrate von 38400 Baud durch Programmierung des Teilerfaktors 1.

#### **Schnittstellentreiber**

Für die Pufferung der Schnittstellen werden Treiber der Typen 1488 und 1489 eingesetzt, die der CCITT-Spezifikation V28 und der EIA-Norm RS232C entsprechen. Für alle Treiber wird die Begrenzung der Anstiegszeit des Ausgangssignals mit externen Kondensatoren vorgenommen, alle Empfänger sind zur Störunterdrückung ebenfalls mit Kondensatoren ausgestattet. Alle an der SCC verfügbaren Modemsteuerleitungen werden getrieben herein- bzw. herausgeführt, also die Signale RTS, CTS, DTR, DCD und SYNC. Sowohl Sende- als auch Empfangstakt können von der Schnittstelle geliefert werden, auch kann der Ausgang des Baudratengenerators getrieben auf der Schnittstelle abgegriffen werden. Die verschiedenen Taktmöglichkeiten werden über ST3 bzw. ST4 eingestellt.

Alle Schnittstellensignale sind an je einem 26-poligen Pfostenstecker pro Kanal abgreifbar. Dieser Pfostenstecker ist so verdrahtet, daß mit einem 25-poligen Flachkabel eine Normbuchse (ISO 2110, DB25S) korrekt angequetscht werden kann.

Für eventuell nötige Vorgabeeinstellungen an den Steuerleitungen oder für die Versorgung eines externen Treibers sind die Schnittstellen-Hilfsspannungen an der Steckerleiste über 1 KOhm Vorwiderstände abgreifbar.

### 3.2 Funktion

---

Der Dateneingang des Kanal B ist umsteckbar (ST5 A/B) auf Optokoppler-Eingabe (20mA TTY). Diese dient vornehmlich als Eingang für die Tastatur ELZET 80 DIN-TAST.

#### Interruptbearbeitung

Die CPU/S ist eingerichtet für den Z80-spezifischen Vektor-interrupt. Der Datenbus wird während der Interruptbestätigung (INTACK) so gesteuert, daß die CPU einen von der Peripherie abgegebenen Vektor einlesen kann. Die SCC ist der einzige interrupterzeugende Baustein und mit IEI/IEO des Bus verdrahtet. IEI ist mit einem Pullup-Widerstand beschaltet.

#### Spannungsversorgung

Neben der Standard-Systemspannung von +5V benötigt die Baugruppe für die seriellen Schnittstellen noch die Hilfsspannungen +12V und -12V. Erfahrungsgemäß kommt ein RS232-Empfänger bei kurzen Kabeln auch mit -5V statt -12V aus. Wenn nur diese Spannung zu Verfügung steht, kann eine Lötbrücke zur -5V-Busleitung gelegt werden.

### 3.3 Anschlüsse

#### 3.3 Anschlüsse

Die CPU/S hat zwei Peripherieanschlüsse, ST1 und ST2. Sie dienen der Verbindung externer Einheiten mit den beiden seriellen Schnittstellen der SCC.

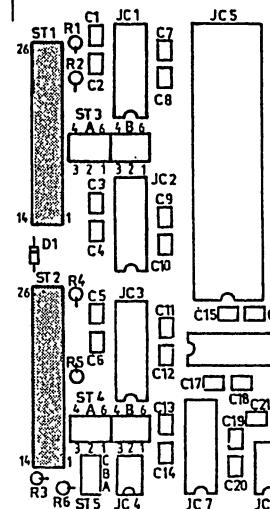

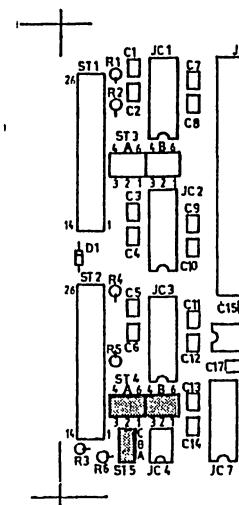

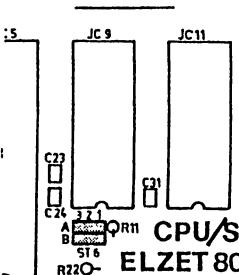

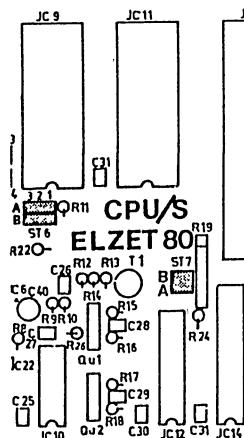

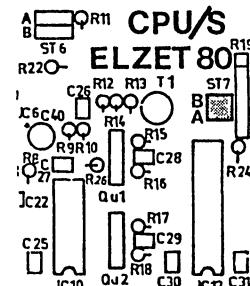

Nebenstehend finden Sie einen Auszug aus dem Bestückungsdruck.

ST1 ist der Anschluß für Kanal A, ST2 für Kanal B. Die beiden Anschlüsse sind identisch bis auf die Zusatzanschlüsse für den Optokoppler bei ST2.

Die Stiftnumerierung weicht ab von der üblichen Markierung bei Pfostenstekkern, um Übereinstimmung mit den Schnittstellen-Normverbindern zu erreichen. Auf der Folgeseite sind die Anschlüsse mit den entsprechenden SCC-Anschlußbezeichnungen versehen. Die Schnittstellentreiber dazwischen bleiben unbeachtet und müssen ggf. dem Schaltbild entnommen werden.

### 3.3 Anschlüsse

---

Steckerbelegung in der Adernreihenfolge des Flachkabels:

DB25S

26p. Pfosten

|        |                    |                                     |       |    |        |

|--------|--------------------|-------------------------------------|-------|----|--------|

| (o 26) | nicht anschließbar | -----                               | 26    | o  | o 13   |

| 13     | o                  | unbeschaltet                        | ----- |    |        |

|        | o 25               | -----negative Hilfsspannung         | ----- | 25 | o o 12 |

| 12     | o                  | unbeschaltet                        | ----- |    |        |

|        | o 24               | -----ST3/4 A1 (TRxC) Ausgang        | ----- | 24 | o o 11 |

| 11     | o                  | positive Hilfsspannung              | ----- |    |        |

|        | o 23               | -----unbeschaltet                   | ----- | 23 | o o 10 |

| 10     | o                  | unbeschaltet                        | ----- |    |        |

|        | o 22               | -----unbeschaltet                   | ----- | 22 | o o 9  |

| 9      | o                  | unbeschaltet                        | ----- |    |        |

|        | o 21               | -----unbeschaltet                   | ----- | 21 | o o 8  |

| 8      | o                  | -----DCD-Eingang                    | ----- |    |        |

|        | o 20               | -----DTR-Ausgang                    | ----- | 20 | o o 7  |

| 7      | o                  | Signalmasse                         | ----- |    |        |

|        | o 19               | -----unbeschaltet                   | ----- | 19 | o o 6  |

| 6      | o                  | -----SYNC-Eingang (DSR)             | ----- |    |        |

|        | o 18               | -----nur ST2: -20mA-Eingang         | ----- | 18 | o o 5  |

| 5      | o                  | CTS-Eingang                         | ----- |    |        |

|        | o 17               | -----ST3/4 A2+B2 Takteingang        | ----- | 17 | o o 4  |

| 4      | o                  | RTS-Ausgang                         | ----- |    |        |

|        | o 16               | -----nur ST2: +20mA-Eingang         | ----- | 16 | o o 3  |

| 3      | o                  | RxD-Dateneingang (bei ST2 über ST5) | ----- |    |        |

|        | o 15               | -----ST3/4 A3+B3 Takteingang        | ----- | 15 | o o 2  |

| 2      | o                  | TxD-Datenausgang                    | ----- |    |        |

|        | o 14               | -----unbeschaltet                   | ----- | 14 | o o 1  |

| 1      | o                  | unbeschaltet                        | ----- |    |        |

### 3.4 Einstellmöglichkeiten

---

#### 3.4 Einstellmöglichkeiten

---

Übersicht über die Einstellmöglichkeiten bei der ELZET 80 CPU/S:

##### a) Steckbrücken

ST 3        Taktversorgung Kanal A

ST 4        Taktversorgung Kanal B

ST 5        Umschaltung RxDB RS232/20mA

ST 6        Einstellung Epromkapazität

ST 7        Aktivierung interner Speicher

ST 8        Bankadreßabschaltung bei BUSACK

##### b) Lötbrücken

BR        Negative Hilfsspannung -5/-12V

##### c) Software

00-04      SCC Register

0C-0F      Bank-/Boot-Register

##### d) Bausteinwechsel

IC14      PAL20L8A Adreßdekodierung interner Speicher

IC15      PROM256x4 Adreßdekodierung interner E/A

Q1        Taktfrequenz CPU

### 3.4 Einstellmöglichkeiten

#### 3.4.1 Steck- und Lötbrücken

##### ST 3 - Taktversorgung Kanal A

Mit ST3 wird die bidirektionale Taktversorgung der SCC eingestellt. ST3A ordnet den SCC-Anschluß TRxC externen Treibern zu, ST3B schließt RTxC an.

Als Taktquellen kommen in Frage:

- Quarzoszillator mit Q2

- Schnittstellentakt von Stift 15

- Schnittstellentakt von Stift 17

- Systemtakt (SCC-intern)

Abgegeben werden kann auf Stift 24:

- Quarzoszillatortakt

- Sendetakt

- Baudratengenerator-Ausgang

- PLL-Ausgang (Empfang)

ST3 A TRxC A

|        |        |        |       |   |

|--------|--------|--------|-------|---|

| 4      | -----  | 5      | ----- | 6 |

| )      |        | )      |       | ) |

| 3      |        | 2      |       | 1 |

| St. 15 | St. 17 | St. 24 |       |   |

ST3 B RTxC A

|        |        |   |        |   |

|--------|--------|---|--------|---|

| 4      | -----  | 5 | -----  | 6 |

| )      |        | ) |        | ) |

| 3      |        | 2 |        | 1 |

| St. 15 | St. 17 |   | Q-Osz. |   |

In der Mehrzahl der Anwendungen wird nur ST3 B 6-1 gebrückt werden, um den Quarzoszillator auf den Baudratengenerator schalten zu können. Externe Taktung entfällt üblicherweise.

### 3.4 Einstellmöglichkeiten

#### ST 4 - Taktversorgung Kanal B

Die Taktversorgung für Kanal B geschieht mit ST4 in der gleichen Weise wie mit ST3 für Kanal A, auch die Steckbrückenbezeichnungen sind identisch.

#### ST 5 - Umschaltung RxDB RS232/20mA

Der SCC-Dateneingang für Kanal B kann statt von Stift 3 des ST2 alternativ von den Stiften 16 und 18 über den Optokoppler IC4 geführt werden.

Mit ST5 wird die Auswahl zwischen den beiden möglichen Signalquellen getroffen:

RS232, ST2/3 -----C o

Abgang zur SCC-----B o

Optokoppler-----A o

#### ST 6 - Einstellung Epromkapazität

Die verschiedenen Eproms benötigen unterschiedliche Signale an den Anschlüssen 26 und 27, wie aus der nebenstehenden Übersicht hervorgeht.

### 3.4 Einstellmöglichkeiten

Mit ST6 A wird die Zuordnung für Anschluß 26 vorgenommen, mit ST6 B entsprechend für Anschluß 28. ST7B muß geschlossen sein!

|   |         |          |              |

|---|---------|----------|--------------|

|   | CPU A13 | EPROM 26 | +5V          |

| A | 3 o     | 2 o      | 1 o          |

| B | 3 o     | 2 o      | 1 o          |

|   | CPU A14 | EPROM 27 | Pullup an 5V |

Hier die Einstellungen für die verwendbaren Eprom-Typen:

|      |   |   |     |      |   |   |     |   |

|------|---|---|-----|------|---|---|-----|---|

| 2732 | A | 3 | 2-1 | 2764 | A | 3 | 2   | 1 |

|      | B | 3 | 2   | 1    | B | 3 | 2-1 |   |

|       |   |     |     |       |   |     |   |

|-------|---|-----|-----|-------|---|-----|---|

| 27128 | A | 3-2 | 1   | 27256 | A | 3-2 | 1 |

|       | B | 3   | 2-1 |       | B | 3-2 | 1 |

ST 7 - Aktivierung interner Speicher

Die internen Speicher können über die Steckbrücken ST7 A/B aktiviert werden. Nur wenn die Brücken gesteckt sind, können die Ausgänge des Registers IC17 auf das PAL wirken, welches die Adresszuweisung vornimmt.

Sind die Brücken gesteckt und ist gleichzeitig das entsprechende Bit im Register IC17 auf Low gesetzt, dann kann auf

### 3.4 Einstellmöglichkeiten

die Speicher zugegriffen werden. Sind die Brücken jedoch nicht gesteckt, dann bleibt das Register wirkungslos, die Speicher können nicht angesprochen werden.

Wenn keine Speicher eingebaut sind, darf auch der zugehörige Jumper nicht gesteckt werden, da sonst das PAL nicht auf Buszugriff umschaltet, wenn eine interne Adresse angesprochen wird.

|        |      |       |

|--------|------|-------|

|        | IC17 | ST7   |

| Eeprom | D5   | B o o |

| Ram    | D4   | A o o |

#### ST 8 - Bankadreßabschaltung bei BUSACK

Da die Z80 CPU nur 16 Adressen (64KByte) ausgibt, sind auch die meisten externen DMA-Einheiten, die auf Z80 Peripherie aufbauen, nicht in der Lage, den vollen Bereich der ELZET 80 Busspezifikation (A0-A19, 1MByte) zu adressieren. Mit ST8 kann ausgewählt werden, ob die CPU grundsätzlich auch bei DMA-Transfer die Bankadressen (A16-A19) erzeugt, oder ob auch die hohen Adressen von der DMA geliefert werden.

ST8 gesteckt:

DMA erzeugt nach BUSACK Bankadresse.

ST8 offen:

Bankadresse kommt immer von der CPU.

### 3.4 Einstellmöglichkeiten

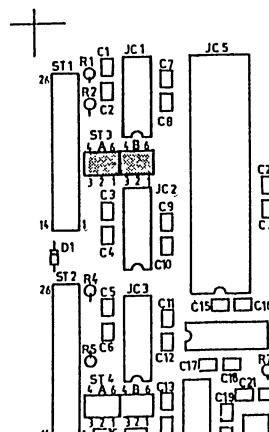

#### Lötbrücke BR - Negative Hilfsspannung -5/-12V

Für die RS232-Treiber werden die Schnittstellen-Hilfsspannungen +12V und -12V benötigt. Diese werden über die entsprechenden Anschlüsse des ELZET 80-Bus zugeführt. Der Anschluß für -12V ist jedoch in den ursprünglichen ECB-Busspezifikationen nicht definiert. Manche ECB-Anbieter verwenden den Anschluß 14A für andere Signale. Sollte die Baugruppe deswegen nicht mit -12V versorgt werden können, so kann man die Schnittstellen aus der -5V-Versorgung des Bus betrieben, Stift 15a. Dies reduziert die mögliche Entfernung des Peripheriegeräts, ist aber meistens ausreichend.

Um diese Anpassung vorzunehmen, muß die Brücke auf der Lötseite der Baugruppe aufgesucht werden, siehe nebenstehenden Leiterbildauszug des Bereichs um den Busstecker. Busanschuß 14a und der Abgang zu den Treibern sind fest mit einer Leiterbahn verdrahtet. Diese muß aufgekratzt werden, danach ist der Abgang durch einen Lötzinntropfen mit dem gegenüberliegenden Quadrat (Bus 15a) zu verbinden.

### 3.4 Einstellmöglichkeiten

---

#### 3.4.2 Einstellmöglichkeiten durch Betriebssoftware

Die Steuerung der seriellen Schnittstellen einschließlich der Einstellung der Baudrate wird ausschließlich über Software vorgenommen. Ansonsten ist auf der Baugruppe nur das Bank-/Boot-Register durch Programm veränderlich.

IC 5 - Z8530 SCC

Die SCC verfügt für jeden Kanal über eine Datenadresse und eine Steueradresse. Alle Befehle an die SCC werden über die Steueradresse ausgegeben. Die SCC arbeitet mit indirekter Registeradressierung. Nach RESET wird bei Schreibzugriffen auf die Steueradresse das interne Register WRO angesprochen. Der Schreibvorgang auf WRO kann nun einen Zeiger auf ein anderes Register (1 bis 15) beinhalten. In diesem Fall erfolgt der nächste Zugriff auf das über den Zeiger angeprochene Register. Ein weiterer Zugriff würde wieder auf Register 0 ausgeführt.

Die E/A-Adressen sind im PROM IC15 festgelegt und werden werkseitig wie folgt programmiert:

| Adresse | Kanal | Schreibzugriff | Lesezugriff    |

|---------|-------|----------------|----------------|

| 00      | B     | Steuerregister | Statusregister |

| 01      | B     | Sendedaten     | Empfangsdaten  |

| 02      | A     | Steuerregister | Statusregister |

| 03      | A     | Sendedaten     | Empfangsdaten  |

### 3.4 Einstellmöglichkeiten

---

Die Programmierung der Baudrate geschieht über verschiedene SCC-interne Register, genau wie die anderen Anweisungen an die SCC. Für die Takterzeugung sind die Register 11 bis 14 zuständig, wobei 12 den niedrigen Wert der Zeitkonstanten aufnimmt und 13 den hohen. Die Register 11 und 14 bestimmen die Quelle des Takts. Neben dem Baudratengenerator ist noch der immer bei USARTs vorhandene interne Teiler :1, :16, :32 und :64 vorhanden, der über Schreibregister 4 eingestellt wird.

Unter der Voraussetzung, daß der 3,6864 MHz Quarzoszillator die Taktquelle für den Baudratengenerator darstellt, und der SCC intern noch mal durch 16 teilt, müssen folgende Werte in WR12 und WR13 programmiert werden:

| Baudrate | Faktor | WR12 | WR13 | Baudrate | Faktor | WR12 | WR13 |

|----------|--------|------|------|----------|--------|------|------|

| 38400    | 1      | 01   | 00   | 600      | 190    | BE   | 00   |

| 19200    | 4      | 04   | 00   | 300      | 382    | 7E   | 01   |

| 9600     | 10     | 0A   | 00   | 150      | 766    | FE   | 02   |

| 4800     | 22     | 16   | 00   | 75       | 1534   | FE   | 05   |

| 2400     | 46     | 2E   | 00   | 45,45    | 2533   | E5   | 09   |

| 1200     | 94     | 5E   | 00   | ...      |        |      |      |

Die Berechnung erfolgt nach der Formel:

$$\frac{3.686.400 \text{ Hz}}{2 \times \text{Baudrate} \times 16} = \text{Teilerfaktor}$$

Weitere Programmierangaben entnehmen Sie bitte Punkt 4.2.

### 3.4 Einstellmöglichkeiten

---

#### IC 17 - Bank-/Boot-Register

Das Bank-/Boot-Register ist ein 8-Bit-Speicher, wovon 4 Bit für die Bankadresse und zwei für die Speicheraktivierung verwendet werden.

Das Register lässt sich durch Ausgabeanweisung auf eine beliebige Portadresse zwischen 0C und 0F Hex laden. Der Speicher wird bei RESET automatisch auf Low gelöscht.

Die einzelnen Bits des Ausgabebytes haben folgende Bedeutung:

| D7 | D6 | D5    | D4  | D3   | D2   | D1   | D0   |

|----|----|-------|-----|------|------|------|------|

| -- | -- | EPROM | RAM | A 19 | A 18 | A 17 | A 16 |

D0 bis D3: Bank 0 bis Bank 15, binär eingestellt

D4 : High schaltet Ram ab, Low schaltet Ram ein \*

D5 : High schaltet Eprom ab, Low schaltet Eprom ein \*

D6, D7 : Nicht benutzt

\*) ST7 muß gesteckt sein, sonst sind die Speicher grundsätzlich abgeschaltet.

Die Bits D0 bis D3 werden über einen Bustreiber auf die Stifte 19c, 17a, 12a und 12c der Bussteckerleiste geführt, entsprechend der Festlegung für A16 bis A19.

### 3.4 Einstellmöglichkeiten

---

Bei Umschaltaktionen der Bankhälfte muß darauf geachtet werden, daß der Zustand der Eprom- und Ram-Bits nicht versehentlich geändert wird und umgekehrt. Dazu ist es notwendig, den Inhalt vor Ausgabe in einer Speicherstelle innerhalb des Common-Ram-Bereichs abzulegen, wo er vor einer Änderung geprüft werden kann.

Da es nur selten notwendig ist, internen Speicher und Bankadressierung zu schalten, wurde aus Kostengründen auf eine Rücklesbarkeit des Registers verzichtet.

### 3.4 Einstellmöglichkeiten

---

#### 3.4.3 Einstellmöglichkeiten durch Bauelementewechsel

Die Adressen sowohl der Speicher wie auch der E/A-Bausteine auf der CPU/S sind in programmierten Bausteinen vorgegeben. Um diese Adressen zu ändern, müssen die Bausteine anders programmiert werden. Diese Arbeiten führen wir im Kunden-auftrag gerne aus. Sie werden nach Aufwand berechnet.

##### IC 14 - PAL 20L8A

Für die Bussteuerung wird ein programmierbares Gate-Array eingesetzt. Da die Ansprache des internen Speichers Einfluß auf die Bussteuerung hat, wurde die Adressierung der Speicher in die Steuergleichungen mit eingebbracht.

##### IC 15 - PROM 256x4

Die Auswahl der E/A-Adressen geschieht durch ein einmalprogrammierbares schnelles Schottky-ROM mit 4 Bit/Wort. Ein Bit (D1) teilt dem Bussteuer-PAL mit, daß interne I/Os angesprochen werden, ein Bit (D2) erlaubt Schreibzugriffe auf das Bank-/Boot-Register und das Bit D3 schließlich erzeugt das Freigabesignal für die SCC.

Da neben den Adressen noch die Signale /IORQ, /M1 und /WR verarbeitet werden müssen, kann nur auf 4 Adressen feindekodiert werden. Aus diesem Grund "findet" man das Bankregister auch auf allen Adressen zwischen 0C und 0F.

### 3.5 Beispiele für die Einstellung

---

#### 3.5 Beispiele für die Einstellung

---

Dieses Kapitel zeigt Beispielinitialisierungen für verschiedene Anwendungen. In 3.5.1 wird die Einstellung für die Haupt-CPU in einem CP/M+-Gerät angegeben, in 3.5.2 für eine CPU, die über den Bus nur noch E/A bedient.

##### 3.5.1 Beispieleinstellung für CP/M-Betrieb

Die Beispieleinstellung beschreibt eine Konfiguration mit FDC4 und VIDEO 80 sowie DIN-TAST. Auf der CPU/S ist das Booteprom (SSM 4.x, 2764) untergebracht, Kanal B des SCC dient als Tastatureingang (20mA) :

ST3, ST4 nach Wunsch, üblicherweise Takt vom Quarzoszillator, also ST3B 1-6; ST4B 1-6

ST5 a-b (20mA)

ST6 ST6A offen, ST6B 1-2 für 2764 Eprom

ST7 B gesteckt entspr. Eprom-Freigabe

ST8 gesteckt, bei DMA wird die Bankadresse von der FDC4 erzeugt

IC9 Bestückt mit SSM V4.x

### 3.5 Beispiele für die Einstellung

---

#### 3.5.2 Beispieleinstellung für Steuerungsapplikation

Die Beispieleinstellung beschreibt eine Konfiguration mit CPU/S und z.B. R24V, Terminal oder übergeordneter Rechner an ST1, Drucker an ST2. 8K Eprom 2764 mit Betriebsprogramm, 8K Ram 6264 als Datenspeicher:

ST3, ST4 A offen, B 1-6 (Quarzoszillator)

ST5 B/C (RS232)

ST6 A offen, B 1-2 (2764)

ST7 A und B gesteckt (Ram und Eprom aktiv)

ST8 beliebig, da kein weiterer Speicher

## 4 Software

---

### 4

### SOFTWARE

#### 4.1 Allgemeines

---

Für die Arbeit der CPU sind keine Initialisierungen vorzunehmen, die CPU erwartet lediglich auf Adresse 0 ein ablauffähiges Programm. Wenn die serielle Schnittstelle benutzt werden soll, ist die SCC zu initialisieren. Als Bankadresse wird beim RESET 0 ausgegeben, so daß hier eine Initialisierung entfällt.

Für die CPU/S existiert als Monitorprogramm mit dem CP/M-Lader der SSM ab Version 4.x aufwärts.

Die zwei grundsätzlichen Betriebsarten der CPU/S ergeben sich durch den Einsatz des Eproms. Es kann als ständig aktiver Programmspeicher benutzt werden oder als Betriebssystemlader für die Arbeit im externen dynamischen Ram.

Für den letzteren Fall kann das Eprom nach Transfer z.B. des Laders oder des Betriebssystems durch eine Ausgabe (High) auf Bit 5 des Bank-/Boot-Registers abgeschaltet werden. Dabei ist darauf zu achten, daß bei einer Ausgabe auf das Bootport die Bankadresse mit ausgegeben werden muß, falls benötigt.

## 4.2 Initialisierung

---

### 4.2 Initialisierung

---

Das Bank-/Boot-Register wird automatisch bei RESET auf 00 initialisiert, so daß die SCC als einziger Baustein einer Initialisierung bedarf.

Bitte lesen Sie zum Verständnis der Initialisierung das technische Handbuch zur SCC. Das hier folgende Beispiel ist die Initialisierungssequenz aus dem Applikationsprogramm unter 4.3.1. Die SCC wird auf 8 Bit Daten, 2 Stopbits, keine Parität und 9600 Baud bei Taktbetriebsart :16 initialisiert. An den Anschlüssen TRxC wird die Baudrate \* 16 ausgegeben.

Die Equates finden Sie beim Beispielprogramm 4.3.1.

```

; initialisierung des scc

;

initscc:ld      hl,initab      ; HL-->Start der Tabelle

ld      c,sccac      ; C = Adresse Steuerport A

ld      b,iblen      ; B = Laenge der Tabelle

otir

; Tabelle in SCC laden

ld      hl,initab      ; wie oben fuer Kanal B

ld      c,sccbc

ld      b,iblen

otir

ret

```

## 4.2 Initialisierung

---

```

initab: db      0          ; Register 0

db      00000000b      ;

db      1          ; Register 1

db      00000000b      ; Keine Interrupts und

; WAIT/DMA-Anforderung

db      2          ; Register 2

db      00000000b      ; Interruptvektor

db      3          ; Register 3

db      11000001b      ; Rx 8 Bit/Z.und freigeben

db      4          ; Register 4

db      01001100b      ; Clock Mode * 16, 2 Stop-

; bits, keine Paritaet

db      5          ; Register 5

db      11101010b      ; DTR, Tx 8 Bit/Zeichen,

; Tx freigeben, RTS

db      6          ; Register 6

db      00000000b      ; Sync Character ( Dummy )

db      7          ; Register 7

db      00000000b      ; Sync Character ( Dummy )

db      9          ; Register 9

db      00000000b      ; kein Interrupt

db      10         ; Register 10

db      00000000b      ; Dummy

db      11         ; Register 11

db      01010110b      ; Rx-Tx Clock vom BR-Gener.

; TRxC Ausgang = Tx Clock

db      12         ; Register 12

db      10         ; 9600 baud bei 3,6864 Mhz

db      13         ; Register 13

db      0          ; MSB Zeitkonstante

```

## 4.2 Initialisierung

---

```

db      14          ; Register 14

db      00000001b    ; BR-Gen-Versorgung v. RTxC

; Baudratengenerator freig.

db      15          ; Register 15

db      00000000b    ; keine externen oder

; Status-Interrupts

;

iblen    equ      $-initab

```

## 4.3 Applikationsbeispiele

---

Als Applikationsbeispiel wurde ein kleines Testprogramm geschrieben, das ohne Zugriff auf andere Baugruppen am Bus läuft und gleichzeitig eine go / no go-Aussage über das interne Eprom und das interne RAM erlaubt.

Das Programm muß für Adresse 0 assembliert bzw. gebunden und in ein Eprom programmiert werden. Das interne RAM wird als Stack benötigt.

Die Initialisierung aus 4.2 wird hier wieder verwendet (9600 Bd, 8 Bit Daten, keine Parität, 2 Stopbit).

### 4.3 Applikationsbeispiele

---

```

.z80

;

;***** Kleines Testprogramm fuer ELZET 80 CPU/S ****

; Kleines Testprogramm fuer ELZET 80 CPU/S *

;

; Es werden staendig 'A's bzw. 'B's an den *

; entsprechenden SCC Datenausgaengen aus- *

; gegeben. *

;***** CPU/S-Adressen

;

sccbc  equ    0          ; SCC Kanal B Steuerreg.

sccbd  equ    sccbc+1    ; SCC Kanal B Datenreg.

sccac  equ    sccbc+2    ; SCC Kanal A Steuerreg.

sccad  equ    sccbc+1    ; SCC Kanal A Datenreg.

;

ram    equ    8000h      ; Anfang des internen RAMs

ramend equ    ram + 1fffh ; letzter RAM-Platz

;

;

; Programmbeginn

;

start: ld     sp,ramend    ; Stack laden

call  initscc      ; SCC Kanäle initialisieren

loop:  ld     c,sccbc      ; Adresse Steuerreg. Kan. B

call  outstat      ; warten bis Sender frei

ld     a,'B'        ; soll ausgegeben werden

inc   c             ; C zeigt auf Kanal B Daten

out   (c),a         ; ausgeben

```

### 4.3 Applikationsbeispiele

---

```

;

inc      c          ; SCC Kanal A Steuerreg.

call    outstat     ; dito fuer Kanal A

ld      a,'A'       ;

inc      c          ;

out      (c),a      ;

jr      loop        ; Endlosschleife

;

include initscc    ; Initialisierungsprogramm

;

;

; von Punkt 4.2 hier ein-

; fügen !

;

; Abfrage Ausgabestatus

;

outstat:in  a,(c)      ; Read Register 0 lesen

and     00000100b    ; Tx Buffer leer ?

jr      z,outstat    ; wenn nicht, weiter abfra-

ret                ; gen, sonst zurueck

;

end

```

## 4.4 Betrieb mit Standardsoftware

---

### 4.4 Betrieb mit Standardsoftware

---

Die CPU/S wird von dem Bootlader SSM in den Versionen ab 4.0 aufwärts unterstützt. Ebenso ist ein CP/M+ für die CPU/S erhältlich.

Das MSR-BASIC ist neben dem Betrieb unter CP/M auch in einer Stand-alone-Version für die CPU/S lieferbar.

#### 4.4.1 Bootlademonitor SSM

Für die Arbeit mit einem Floppy-Betriebssystem ist der Bootlademonitor SSM erhältlich, der außer dem Ladevorgang noch die Diagnosefunktionen eines Maschinenmonitors erfüllt.

Der SSM ab Version 4.0 unterstützt den Betrieb der CPU/S mit Bildschirmausgabe über ein RS232-Terminal an Kanal B oder über VIDEO80(F) mit ELZET 80 DIN-TAST am Eingang von Kanal B der SCC.

Als Baudrate wird in beiden Fällen 9600 Baud vorausgesetzt, Terminal bzw. Tastatur müssen darüberhinaus auf 8 Bit Datenwort mit einem Stopbit und ohne Parität eingestellt werden. Eine Druckausgabe erfolgt auf alle parallelen Druckerschnittstellen (PRINT/CTC, /IEC, /UHR) und auf den Kanal A der SCC für RS232-Drucker (Format wie Terminal).

#### 4.4 Betrieb mit Standardsoftware

---

Als Floppy-Steuerbaugruppen können die FDC3 und die FDC4 Verwendung finden.

Die Hardwareeinstellung für den Betrieb mit SSM ist bei Punkt 3.5.1 beschrieben.

Für eine Beschreibung des SSM verweisen wir auf den ELZET80 Katalog 1985 und das SSM-Handbuch.

##### 4.4.2 Der Betrieb mit CP/M+

Für die CPU/S existiert eine angepaßte Version des Betriebssystems CP/M+ (Digital Research). Neben der CPU/S ist dazu folgende Hardware nötig:

|                         |                                                                                                                |

|-------------------------|----------------------------------------------------------------------------------------------------------------|

| Floppy-Steuerbaugruppe: | FDC3 oder FDC4                                                                                                 |

| Speicher :              | 128K auf FDC3 oder 1M/256K,<br>adressiert auf Bank 0,1,(2,3)                                                   |

| Benutzerkommunikation : | Terminal an SCC, Kanal B<br>oder : DIN-TAST an SCC-B und VIDEO80                                               |

| Floppy-Laufwerke :      | Ein(ES)- oder zweiseitig (DS) 8"<br>oder : DS 80-Spur 5,25" oder 3,5"<br>oder : ES 40-Spur 5,25" oder 3,25" *) |

| (Hard-Disk :            | Bis 65 MByte, nach Absprache)                                                                                  |

| Bootlademonitor :       | SSM Version 4.x aufwärts in<br>Eprom-Sockel auf CPU/S                                                          |

| Sonstiges :             | Busplatine und Stromversorgung                                                                                 |

Die Einstellung erfolgt wie unter 3.5.1 beschrieben.

## 4.4 Betrieb mit Standardsoftware

---

### 4.4.3 Funktionsbeschreibung mit MSR-Basic

Die CPU/S ist sehr gut geeignet für den Einsatz zusammen mit dem MSR-BASIC in Eprom.

Der 27256 auf der CPU/S faßt bequem den Interpreter und läßt Platz für ca. weitere 8KByte BASIC-Code bei fertig entwickelten Programmen.

Als Zeitscheibentakt für die Echtzeitfunktion des MSR-BASIC muß ein 10ms-Interrupt erzeugt werden. Dazu verwendet die vorliegende Implementation den Baudratenzähler des Kanals A. Aus diesem Grund ist es notwendig, die Taktversorgung der seriellen Schnittstelle Kanal A von Kanal B zu übernehmen. Dazu muß eine Drahtverbindung entweder direkt zwischen SCC Pin 26 und Pin 12 vorgenommen werden oder zwischen ST4A, P.5 und ST3B, P.5. Auf ST3 darf nichts gesteckt sein. Die seriellen Schnittstellen werden als MSR-Kanal 0 (SCC-B) und Kanal 1 (SCC-A) unterstützt, Standard-Baudrate ist 9600 Baud.

Die Steckbrücken auf der CPU/S sind für RS232-Terminal und RS232-Drucker sowie für 32K Eprom und 8K Ram wie folgt zu setzen:

- ST3 offen,

- ST4 A offen, B 1-6 (Quarzoszillator)

- ST5 B/C (RS232)

- ST6 A 2-3, B 2-3 (27256)

- ST7 A und B gesteckt (Ram und Eprom aktiv)

- ST8 beliebig, da kein weiterer Speicher

## 5 Inbetriebnahme

---

### 5

### INBETRIEBNNAHME

#### 5.1 Voraussetzungen für den Betrieb

---

Die Baugruppe ELZET 80 CPU/S benötigt für den Betrieb ein Programm (z.B. Monitor SSM), welches in Eprom vorliegen muß. Das Eprom kann vom Typ 2732 bis 27256 sein, das Programm muß für Adresse 0 geschrieben sein. Üblicherweise wird außerdem RAM benötigt, dazu ist im Sockel IC11 ein Speicherbaustein vom Typ 6264 einzusetzen. Als Assemblerdirektive ist der RAM-Start mit 8000H anzugeben.

Ferner werden die Spannungen + 5V mit 800mA und für die seriellen Schnittstellen +12V mit 30mA und -12V mit 30mA benötigt.

Punkt 3.4 gibt Auskunft über die Einstellung der CPU/S für verschiedene Eprom- und Ram-Bausteine.

Alternativ sind auch externe RAM-Baugruppen verwendbar, diese müssen jedoch so adressiert sein, daß sie den Eprom-Bereich von 0000 bis 8000H nicht gleichzeitig belegen.

Transfer des Eprom-Inhalts in externes RAM und Ausführung des Programms im RAM sind jedoch auch dann möglich, wenn das externe RAM bei 0 beginnt. Allerdings kann nur auf RAM-Adressen über 8000H transferiert werden. Dazu ist nach dem

### 5.1 Voraussetzungen für den Betrieb

---

Transfer das Freigabebit für das Eprom auf Adresse 0F, Bit D5, auf High zu setzen.

Der Peripheriebaustein SCC muß initialisiert werden, siehe dazu Punkt 4.2.

Zur korrekten Interruptbearbeitung muß die Z80 Interruptkette geschlossen sein, mit anderen Worten müssen die interruptgebenden Baugruppen im Bus ohne Zwischenraum gesteckt werden. Von der Baugruppe mit der höchsten Interruptpriorität ist die Bauteilseite im Kartenstapel sichtbar. Die CPU-Funktion ist unabhängig von der Lage in der IEI/IEO-Kette. Weitere Erläuterungen im Technik-Teil des ELZET 80 -Katalogs.

## 5.2 Art und Umfang des Testbetriebs

---

### 5.2 Art und Umfang des Testbetriebs

---

Für den Test seien hier zwei Möglichkeiten vorgestellt, eine bequeme und eine minimale. Die bequeme setzt einige Hardware voraus, die allerdings für den Betrieb mit Floppy ohnehin vorhanden sein muß. Die hardwaremäßig minimale Testmöglichkeit verwendet das Applikationsprogramm aus 4.3.1.

Für den bequemen Test wird die CPU mit dem SSM-Monitor bestückt. Als RAM ist eine externe Baugruppe notwendig, die mindestens im Bereich F000H bis FFFFH arbeitet. Über einen Bus werden die beiden Baugruppen verbunden und mit Spannung versorgt. Entweder kann dann an ST 2 ein Terminal angeschlossen werden, oder die VIDEO80-Karte wird als Ausgabemedium verwendet, zusammen mit der ebenfalls an ST2 anzuschließenden Tastatur. Die Steckbrücken sind wie im Beispiel 3.5.1. einzustellen.

Bei korrekter Verdrahtung können alle Funktionen des SSM mit Ausnahme des Bootladens ausgeführt werden, womit ein Großteil der Baugruppenfunktionen testbar wird.

Für den Minimaltest ist das Programm aus 4.3.1 in Eprom zu bringen und zusammen mit einem RAM auf die CPU zu stecken. An den Datenausgängen von ST1 und ST2 können Terminal und/oder Drucker angeschlossen werden, auf denen die Kanalbezeichnung fortlaufend ausgegeben wird.

### 5.3 Aufbau der Testumgebung

---

#### 5.3 Aufbau der Testumgebung

---

Für den Test mit SSM wie unter 5.2 sind folgende Teile notwendig:

- a) Netzteil mit 5V/2A,  $\pm 12V/50mA$ . Bei VIDEO80/DIN-TAST und DIN-TAST-Anschluß an den Optokoppler können die  $\pm 12V$  entfallen.

- b) BUS beliebiger Länge.

- c) Speicherbaugruppe, bei der der Bereich F000(Hex) bis FFFF (Hex) bestückt ist, also z.B. 64KRE mit RAM 8Kx8 in Sockel 4 bzw. 8, selektiert entsprechend auf U(pper) und ungebant bzw. Bank 0. Die 1M-Karte in jeder Bestückung eignet sich ebenso für den Test und auch die ältere Baugruppe 256K.

- d) Eprom mit SSM der Version 4.x oder höher.

- e1) Terminal an ST2.

oder

- e2) DIN-TAST an ST2, VIDEO80 auf dem Bus, Bildschirm an VIDEO80.

Das Netzteil wird zunächst auf korrekte Spannung überprüft. Dazu sind bei manchen Schaltnetzteilen (z.B. NT2) Vorlasten notwenig (NT2 600mA/5V, 300mA/ $\pm 12V$ ). Nun erfolgt die Verdrahtung mit dem Bus.

### 5.3 Aufbau der Testumgebung

---

Die +5V sind an 1a und 1c anzuschließen, Masse an 32a und 32c. Es ist Kabel mit ausreichendem Querschnitt zu verwenden, z.B. 1,5 <sup>2</sup> mm. Für die Schnittstellentreiber RS232 (Terminal oder Drucker) müssen noch +12V an 13a und -12V an 14a angelegt werden.

Das Eeprom mit dem SSM wird in den Sockel IC9 der CPU/S gesteckt (Pin 1 - Kerbe Richtung Kartenmitte). Je nach Eepromtyp werden die Steckbrücken ST6 eingestellt (siehe 3.4.1).

Die Steckbrücken auf der CPU/S sind wie bei 3.5.1 einzustellen, ST5 (20mA/RS232) bei Terminal jedoch auf b-c.

Ein Anschlußkabel für das Terminal ist zu fertigen. Dazu sind die Sendedaten des Terminals mit Anschluß 3 von ST2 zu verbinden, die Empfangsdaten mit 3/ST2 und Masse mit 7/ST2. Ist das Terminal nicht in der Lage, 9600 Baud ohne Handshake (Quittungsbetrieb) zu verarbeiten, so muß das Quittungssignal des Terminals auf Anschluß 5 (CTS) von ST2 verdrahtet werden.

Bei Verwendung der ELZET 80 DIN-TAST muß auf dieser der Stromschleifenausgang gewählt werden. Das Signal ist auf Pin 16/ST2 zu führen, Masse auf Pin 18. Die Tastatur muß außerdem mit +5V vom Netzteil versorgt werden.

Nach Anbringen des Anschlußkabels kann die CPU/S auf den Bus gesteckt werden.

### 5.3 Aufbau der Testumgebung

---

Die Speicherbaugruppe wird auf korrekte Adressauswahl überprüft (entfällt bei 1M) und ebenfalls auf den BUS gesteckt.

Bei Ausgabe über VIDEO80 ist ein Monitor anzuschließen, wobei für den ersten Test ein BAS-Monitor empfehlenswert ist, um Fehler durch falsche SYNC-Polaritätswahl zu vermeiden.

Das Terminal wird auf 9600 Baud, 8 Bit Daten, keine Parität und ein Stopbit eingestellt.

#### Test ohne SSM

Stehen SSM oder externer Speicher nicht zur Verfügung, kann auf das Testprogramm aus 4.3 zurückgegriffen werden. Dazu sind folgende Teile nötig:

- a) Netzteil mit 5V/2A,  $\pm 12V/50mA$ .

- b) Eprom mit SSM der Version 4.x oder höher.

- c) RAM 8Kx8 (6264, 5564, 5565)

- d) Terminal oder Drucker an ST2.

Das Netzteil zunächst auf korrekte Spannung überprüfen (s.o.). Die Verbindung zur Baugruppe kann z.B. über eine Federleiste (Busbuchse) vorgenommen werden. Dabei sind die +5V an 1a und 1c anzuschließen, Masse an 32a und 32c. Für

### 5.3 Aufbau der Testumgebung

---

die Schnittstellentreiber RS232 (Terminal oder Drucker) müssen noch +12V an 13a und -12V an 14a angelegt werden.

Das Eprom mit dem fertigen Testprogramm wird in den Sockel IC9 der CPU/S gesteckt (Pin 1 - Kerbe Richtung Kartenmitte). Je nach Epromtyp werden die Steckbrücken ST6 eingestellt (siehe 3.4.1).

Das RAM wird mit der Kerbe zur Kartenmitte in den Sockel IC11 gesteckt.

Die Steckbrücken auf der CPU/S sind wie bei 3.5.2 einzustellen.

Ein Anschlußkabel für das Terminal oder den Drucker ist zu fertigen. Dazu sind die Empfangsdaten des Terminals mit Anschluß 2 von ST2 zu verbinden und Masse mit 7/ST2. Ist das Terminal nicht in der Lage, 9600 Baud ohne Handshake (Quittungsbetrieb) zu verarbeiten, so muß das Quittungssignal des Terminals auf Anschluß 5 (CTS) von ST2 verdrahtet werden.

Das Terminal bzw. der Drucker wird auf 9600 Baud, 8 Bit Daten, keine Parität und ein Stopbit eingestellt.

## 5.4 Testablauf

---

### 5.4 Testablauf

---

#### a) Test mit SSM

Netzteil einschalten. Der SSM-Monitor meldet sich bei korrektem Betrieb auf dem Bildschirm und nimmt Anweisungen entgegen.

#### b) Test mit Testprogramm

Netzteil einschalten. Auf dem Ausgabegerät werden laufend B's ausgegeben.

## 5.5 Diagnosemöglichkeiten

---

#### a) Test mit SSM

Meldet sich der SSM-Monitor nicht, zunächst Bildschirm überprüfen (Netzspannung).

Dann Betriebsspannungen nachmessen.

Eeprom überprüfen, ob alle Pins sich in der Fassung befinden.

## 5.5 Diagnosemöglichkeiten

---

VIDEO80 entfernen. Mit dem Oszilloskop an TxDB (2/ST2) RESET auslösen (Bus 31c auf Masse tasten): Wird die Meldung zum Terminal übertragen ? Achtung: Dauer nur ca. 30ms.

Wenn nicht: Liegt Takt 3,6864 MHz an RTxCB (Pin 28) an?

Wird die SCC auf Eingaben abgefragt (Low-Pulse an CESCC, Pin 33).

### b) Test mit Testprogramm

Werden keine Zeichen ausgegeben, zunächst Betriebsspannungen überprüfen.

RAM und EPROM auf korrekten Sitz im Sockel testen. ST7 A und ST7 B müssen gesteckt sein. Ist ST6 korrekt für das gewählte Eprom eingestellt ?

Dann direkt mit Oszilloskop an Pin2/ST2 (TxDB)

Wenn Schnittstelle keine Signale abgibt, RTxCB und CESCC (s.o. SSM) überprüfen.

"Bewegen" sich die unteren Adressen der CPU?

Wenn auch da alles tot ist, auf Taktfrequenz CPU gehen (Bus 29c).

## 6 Technische Unterlagen

---

### 6

### TECHNISCHE UNTERLAGEN

#### 6.1 Schaltungsbeschreibung

---

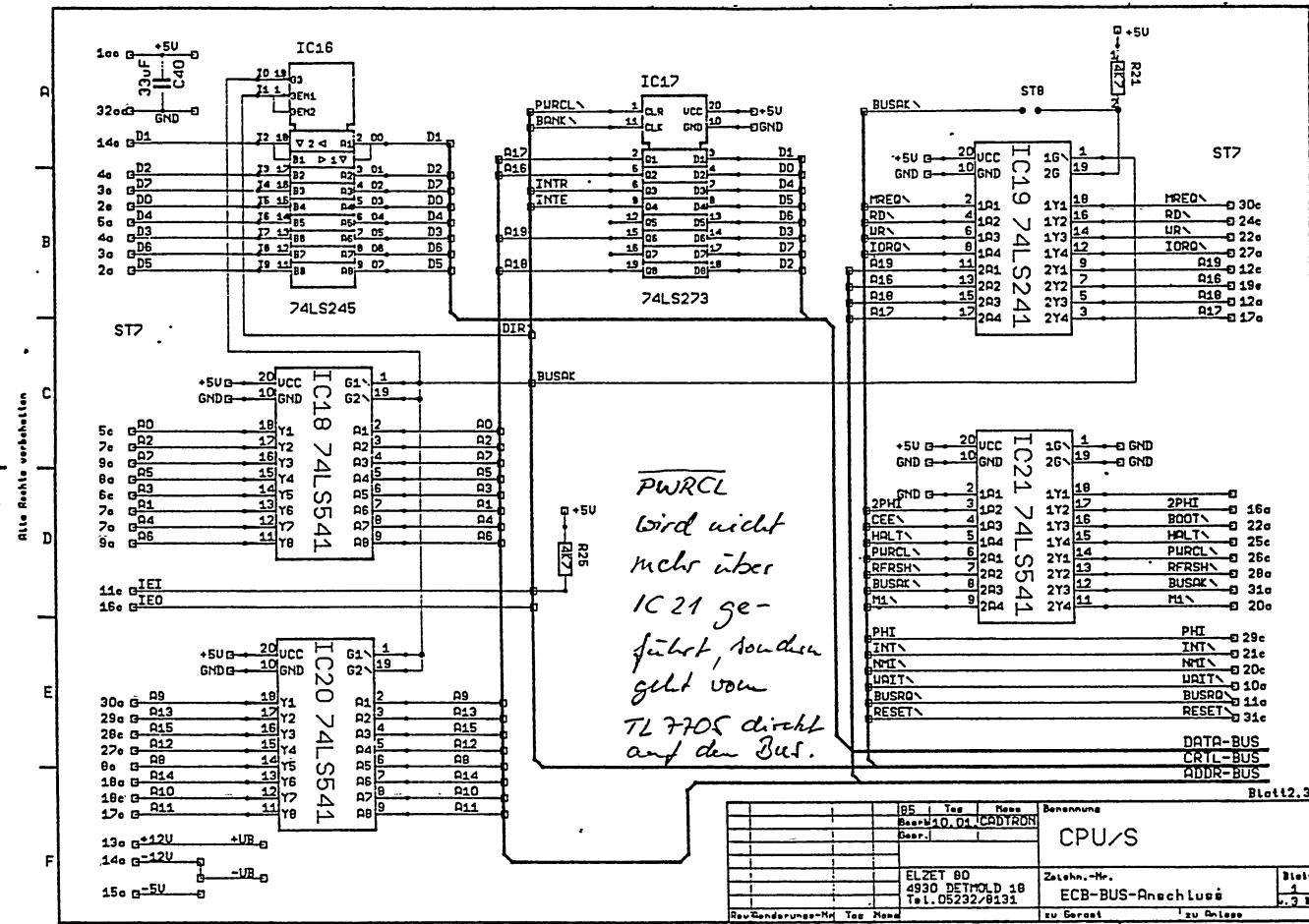

Neben der CPU erfolgt die Steuerung der Funktionen auf der Baugruppe hauptsächlich durch das IC14, ein PAL 20L8A. Hier wird die Richtungsumschaltung des Datenbus (/DIR) unter Einbeziehung der Interruptkonditionen und des Zugriffs auf interne Speicher vorgenommen. Gleichzeitig erledigt das PAL die Adressdekodierung für die internen Speicher. Die Look-ahead-Schaltung für die IEI/IEO-Kette sowie die Erzeugung der Sondersignale (IACK, RESET) für die Z85-Peripherie (SCC).

Die eigentliche Datenbuspufferung übernimmt IC16 (LS245), der Adressbus bis A15 wird über IC18 und IC20 (LS541) getrieben. Die oberen Adressen und ein Teil der Steuersignale werden mit IC19 (LS241) gepuffert, die restlichen Steuersignale mit IC21 (LS541).

Die Erzeugung der oberen Adressen geschieht durch Ausgabe auf IC17 (LS273), welches mit dem PROM-Ausgang /BANK getaktet und durch /PWRCL rückgesetzt wird.

Das PROM IC15 (256x4, 82S129) erzeugt zudem die E/A-Adressdekodierung für die SCC (/CESCC) und meldet über /INTIO die Adressierung interner E/As an das PAL.

## 6 Technische Unterlagen

---

RESET wird über IC10 nach ZILOG-Empfehlung mit M1 verknüpft und auf das IC 8 (TL7705) gegeben, welches eine definierte RESET-Zeit, abhängig von der Kapazität C21, erzeugt. IC8 erzeugt ebenfalls RESET bei Unterspannung (<4,7V) bzw. beim Einschalten.

Als Taktoszillator wird ein Treiber IC12 (LS240) benutzt, der auf der doppelten Frequenz der eigentlichen Prozessor-Arbeitsfrequenz schwingt. Das Oszillatorsignal wird als 2PHI direkt auf den Bus gebracht. Die Arbeitsfrequenz wird durch Teilung in IC10 erzeugt und mit einer aktiven Pullup-Schaltung mit T1 als PHI auf den Bus und die internen LSI-Bausteine geführt. Durch die Treiberschaltung werden MOS-spezifische Pegel bei gleichzeitig schnellen Anstiegszeiten ermöglicht.

Weitere Treiber des IC12 werden für den Taktoszillator der seriellen Schnittstelle eingesetzt, der auf 3,6864 MHz schwingt. IC5 ist der Serienwandler SCC (Z8530). Als Pegelwandler für die RS232-Pufferung werden 1488/1489-Standardtreiber eingesetzt, IC1 und IC2 für Kanal A, IC3 und IC7 für Kanal B, IC6 als Taktempfänger für beide Kanäle und IC4 (CQY80) als Optokoppler für den 20mA-Eingang.

## 6.2 Technische Daten

---

### 6.2 Technische Daten

---

#### Filmnummer der neuesten Version:

134-8519.

Die nach Filmnummer 134-8519 gearbeiteten Baugruppen sind die neuesten, die dieser Beschreibung zugrundeliegen. Vorherige Versionen wurden nicht allgemein zugänglich gemacht.

#### Betriebsspannungen:

+5V ( $\pm 5\%$ ) mit max. 800mA

Nur für die Pegelwandler der seriellen Schnittstelle werden zusätzlich noch Hilfsspannungen benötigt:

+12V mit max. 30mA und -12V mit max. 30mA.

#### E/A-Kanäle:

Zwei serielle Voll-Duplex-Kanäle mit Treibern nach RS232/V28. Pro Kanal sind die beiden Datenleitungen, 5 Modemsignale (Handshake) und drei Taktsignale getrieben verfügbar. Der Empfänger des Kanals B kann auch aus einer 20mA-Stromschleife bedient werden.

Ferner ist die Bankadreßserzeugung als Ausgabekanal ausgeführt: 4 Bit mit  $I_{OL} = 24mA$ , die fest auf die Busschnittstelle verdrahtet sind.

## 6.2 Technische Daten

---

### RESET-Zeit:

Die RESET-Zeit wird über C21 eingestellt. Mit der Standardbestückung von 100nF ergibt sich eine Zeit von ca. 1ms. Eine Veränderung der Kapazität bewirkt eine proportionale Veränderung der Zeit; 10nF entsprechen also 100us.

### Speicher:

Je ein Sockel für EPROMs 2732 bis 27256 (IC9, 4 KByte bis 32 KByte) und RAMs 6264 (IC11, 8 KByte). Die Speicher müssen für folgende Zugriffsgeschwindigkeit über den gewünschten Temperaturbereich ausgelegt sein:

|               |       |       |

|---------------|-------|-------|

| Taktfrequenz: | 4 MHz | 6 MHz |

| Eeprom:       | 350ns | 250ns |

| Ram:          | 350ns | 250ns |

### Adressierung:

Das interne Eprom wird auf den Adressen zwischen 0 und 7FFFH angesprochen, das interne RAM zwischen 8000 und 9FFFH. Die Bankadressen bleiben bei der Dekodierung unberücksichtigt.

Die seriellen Schnittstellen (SCC) werden über die Adressen 00 bis 03 im E/A-Adressbereich angesprochen, das Bank/Boot-Port über die Adressen 0C bis 0FH.

## 6.2 Technische Daten

---

### Peripherie-Anschlüsse:

An ST1 ist die serielle Schnittstelle Kanal A anzuschließen, an ST2 entsprechend Kanal B. Es handelt sich bei ST1 und ST2 um 26-polige Pfostenstecker, auf die Flachkabelverbinder aufgesteckt werden können. Die SIEMENS-Bestellbezeichnung für die passende Kupplung lautet: C42334-A422-A64.

Am anderen Ende des Kabels kann eine RS232/V24-Normbuchse angeschlagen werden, die entsprechende SIEMENS-Bestellnummer lautet: V42254-A5231-B325.

### Busanschluß:

Die Verbindung zum Bus erfolgt über einen Steckverbinder nach DIN 41612, Bauform C, bestückt auf den Kontaktreihen a und c.

Die Belegung entnehmen Sie bitte dem Abschnitt 6.3.

### Arbeitstemperaturbereich:

0 bis +55 C bei freier Konvektion

### Lagertemperaturbereich:

-40 C bis +125 C

## 6.2 Technische Daten

---

### Feuchtebereich:

0% bis 95%, nicht kondensierend

### Abmessungen:

100 x 167 x 17 mm<sup>3</sup>

### Gewicht:

ca. 130 g

### 6.3 Busteckerbelegung

---

#### 6.3 Busteckerbelegung

---

Nur die Anschlüsse, bei denen die Stiftsymbole (o) gefüllt sind, werden von der Baugruppe erzeugt bzw. benötigt. Bitte beachten Sie die Markierungen "#"; bei diesen Anschlüssen sind Abweichungen gegenüber anderen ECB-Anbietern möglich.

#### 6.4 Stückliste

---

##### 6.4 Stückliste

---

| Bez.                        | Stück | Artikel                 | Typ/Wert   |

|-----------------------------|-------|-------------------------|------------|

| IC 1, 3                     | 2     | Integrierte Schaltungen | MC1488     |

| IC 2, 6, 7                  | 3     | Integrierte Schaltungen | MC1489     |

| IC 4                        | 1     | Optokoppler             | CQY80      |

| IC 5                        | 1     | Integrierte Schaltung   | Z8530 SCC  |

| IC 8                        | 1     | Integrierte Schaltung   | TL7705     |

| IC 9                        | 1     | Sockel für Eprom        | 28p.       |

| IC 10                       | 1     | Integrierte Schaltung   | 74LS107    |

| IC 11                       | 1     | Sockel für Ram          | 28p.       |

| IC 12                       | 1     | Integrierte Schaltung   | 74LS240    |

| IC 13                       | 1     | Integrierte Schaltung   | Z8400 CPU  |

| IC 14                       | 1     | Integrierte Schaltung   | PAL20L8    |

| IC 15                       | 1     | Integrierte Schaltung   | PROM82S129 |

| IC 16                       | 1     | Integrierte Schaltung   | 74LS245    |

| IC 17                       | 1     | Integrierte Schaltung   | 74LS273    |

| IC 18, 20, 21               | 3     | Integrierte Schaltungen | 74LS541    |

| IC 19                       | 1     | Integrierte Schaltung   | 74LS241    |

| T 1                         | 1     | Transistor              | 2N3906     |

| D 1                         | 1     | Diode                   | 1N4148     |

| R 1, 2, 4, 5, 6,<br>15 - 18 | 9     | Widerstände 1/3 W       | 1kOhm      |

| R 3                         | 1     | Widerstand 1/3 W        | 100 Ohm    |

| R 7, 8, 10, 11,<br>21       | 5     | Widerstände 1/3 W       | 4,7 kOhm   |

| R 9                         | 1     | Widerstand 1/3 W        | 270 Ohm    |

| R 12                        | 1     | Widerstand 1/3 W        | 1,2 kOhm   |

#### 6.4 Stückliste

---

|               |    |                         |             |

|---------------|----|-------------------------|-------------|

| R 13, 14      | 2  | Widerstände 1/3 W       | 220 Ohm     |

| R 19          | 1  | Widerstandsnetzwerk     | 5x 4,7 kOhm |

| R 20          | 1  | Widerstandsnetzwerk     | 8x 4,7 kOhm |

| R 22, 23      | 2  | Widerstände 1/3 W       | 330 Ohm     |

| C 1 - 20      | 20 | Keramikkondensatoren    | 330, pF     |

| C 21 - 25, 30 |    |                         |             |

| - 39          | 15 | Keramikkondensatoren    | 100 nF      |

| C 26          | 1  | Keramikkondensator      | 33 pF       |

| C 27          | 1  | Keramikkondensator      | 10 nF       |

| C 28          | 1  | Keramikkondensator      | 1 nF        |

| C 29          | 1  | Keramikkondensator      | 22 nF       |

| C 40          | 1  | Tantalkondensator       | 33 uF/6,3 V |

| Q 1           | 1  | Quarz HC 18/U           | 8 MHz       |

| Q 2           | 1  | Quarz HC 18/U           | 3,6864 MHz  |

| ST 1, 2       | 2  | Pfostenstecker          | 2 x 13p.    |

| ST 3, 4       | 2  | Pfostenstecker          | 2 x 6p.     |

| ST 5          | 1  | Pfostenstecker          | 1 x 3p.     |

| ST 6          | 1  | Pfostenstecker          | 2 x 3p.     |

| ST 7          | 1  | Pfostenstecker          | 2 x 2p.     |

| ST 8          | 1  | Stiftleiste abgewinkelt | 64p. a+c    |

| LP            | 1  | Leiterplatte            | 134-8519    |

## 6.5 Bestückungsplan

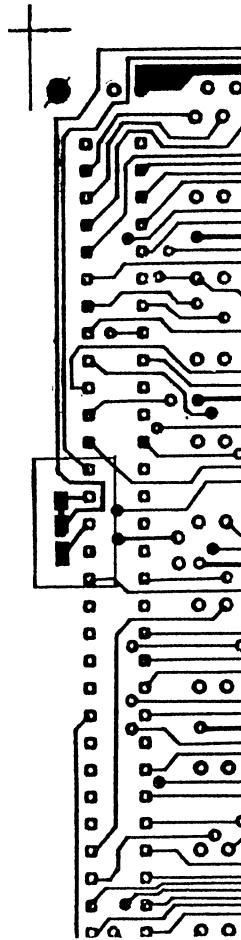

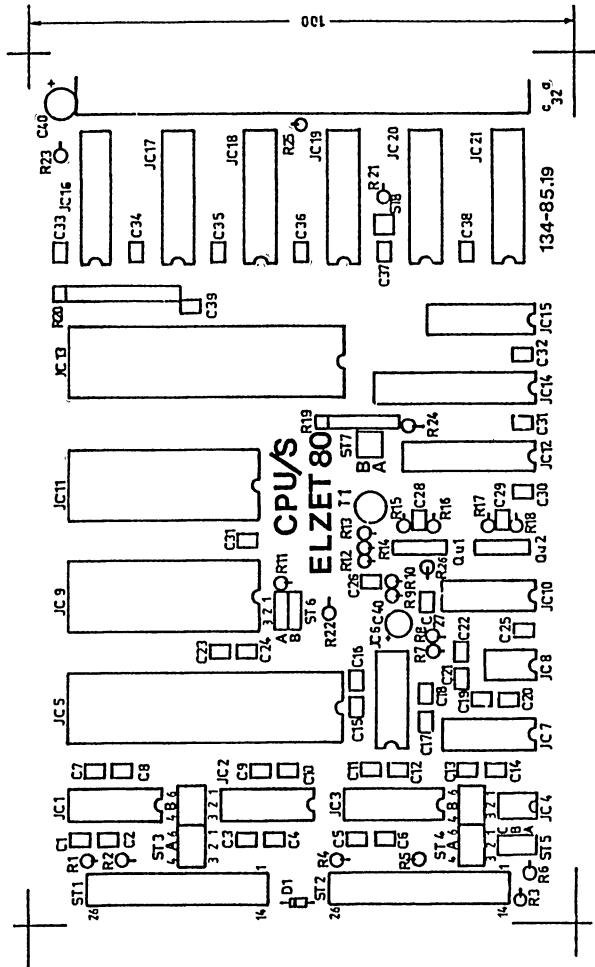

### 6.5 Bestückungsplan

---

## 6.6 Datenblattauszüge

---

### 6.6 Datenblattauszüge

---

|               |    | a | c |                  |

|---------------|----|---|---|------------------|

| +5V           | 1  | ● | ● | 1 +5V            |

| D5            | 2  | ● | ● | 2 D0             |

| D6            | 3  | ● | ● | 3 D7             |

| D3            | 4  | ● | ● | 4 D2             |

| D4            | 5  | ● | ● | 5 A0             |

| A2            | 6  | ● | ● | 6 A3             |

| A4            | 7  | ● | ● | 7 A1             |

| A5            | 8  | ● | ● | 8 A8             |

| A6            | 9  | ● | ● | 9 A7             |

| /WAIT         | 10 | ● | ○ | 10 --            |

| /BUSRQ        | 11 | ● | ● | 11 IE1           |

| A18#          | 12 | ● | ● | 12 #A19          |

| +12V          | 13 | ● | ○ | 13 --            |

| -12V          | 14 | ● | ● | 14 D1            |

| -5V           | 15 | ○ | ○ | 15 -15V          |

| 2PH1          | 16 | ● | ● | 16 IEO           |

| A17#          | 17 | ● | ● | 17 A11           |

| A14           | 18 | ● | ● | 18 A10           |

| +15V          | 19 | ○ | ● | 19 #A16          |

| /M1           | 20 | ● | ● | 20 /NNI          |

| --            | 21 | ○ | ● | 21 /INT          |

| /Boot active# | 22 | ● | ● | 22 /WR           |

| /BA1#         | 23 | ○ | ○ | 23 #/VIDEO BLANK |

| VMOS          | 24 | ○ | ● | 24 /RD           |

| /BA0#         | 25 | ○ | ● | 25 /HALT         |

| --            | 26 | ○ | ● | 26 /PWRCL        |

| /IORQ         | 27 | ● | ● | 27 A12           |

| /RFRSH        | 28 | ● | ● | 28 A15           |

| A13           | 29 | ● | ● | 29 PHI           |

| A9            | 30 | ● | ● | 30 /HREQ         |

| /BUSAR        | 31 | ● | ● | 31 /RESET        |

| MASSE         | 32 | ● | ● | 32 MASSE         |

\* = abweichend von KONTRON EBC-Busbelegung

Preliminary Data Sheet of the Supply Voltage Supervisor

SERIES TL7702

Preliminary Data Sheet of the Supply Voltage Supervisor

SERIES TL7702

absolute maximum ratings over operating free-air temperature range (unless otherwise noted)

|                                          |                |

|------------------------------------------|----------------|

| Supply voltage $V_{CC}$ (see Note 1)     | 20V            |

| Input voltage at RESIN- (see Note 1)     | -0.3 to 20V    |

| Input voltage at SENSE                   |                |

| TL7702 (see Note 1)                      | -0.3 to 6V     |

| TL7705 TL7709 TL7712 TL7715 (see Note 1) | -0.3 to 20V    |

| Operating free-air temperature range     | 0°C to 70°C    |

| Storage temperature range                | -65°C to 150°C |

NOTE 1. All voltage values are with respect to the network ground terminal.

recommended operating conditions at specified temperature range

|                                             | MIN | TYP | MAX | UNIT |

|---------------------------------------------|-----|-----|-----|------|

| Supply voltage $V_{CC}$                     | 3   | 18  | 20  | V    |

| High-level input voltage at RESIN- $V_{IH}$ | 2.0 |     |     | V    |

| Low-level input voltage at RESIN- $V_{IL}$  |     | 0.7 |     | V    |

| High-level output current $I_{OH}$ at RESET |     | -1  |     | mA   |

| Low-level output current $I_{OL}$ at RESET  |     | 16  |     | mA   |

| Operating free-air temperature range $T_A$  | 0°  | 70° | C   |      |

electrical characteristics over full range of recommended operating conditions

| PARAMETER                                   | TEST CONDITIONS                | MIN          | TYP  | MAX     | UNIT |

|---------------------------------------------|--------------------------------|--------------|------|---------|------|

| $I_{IL}$ Low-level input current at RESIN-  | $V_{IL} = 0.4V$                |              | -100 | $\mu A$ |      |

| $I_{IH}$ High-level input current at RESIN- | $V_{IH} = 2.4V$ $V_{CC}$       |              | 20   | $\mu A$ |      |

| $V_{CH}$ High-level output voltage at RESET | $I_{OH} = \text{max}$          | $V_{CC} - 1$ |      |         | V    |

| $V_{OL}$ Low-level output voltage at RESET  | $I_{OL} = \text{max}$          |              | 4    | V       |      |

| $V_{REF}$ Reference voltage                 |                                |              | 2.5  |         | V    |

| $V_S$ Sense voltage                         | $V_{CC} = 3.5 \text{ to } 18V$ |              |      |         |      |

| TL7702                                      |                                |              |      |         |      |

| TL7705                                      |                                | 4.7          | 4.75 | 4.8     | V    |

| TL7709                                      |                                | 7.5          | 7.6  | 7.7     | V    |

| TL7712                                      |                                | 11.2         | 11.4 | 11.6    | V    |

| TL7715                                      |                                | 14.0         | 14.2 | 14.4    | V    |

| $I_{CC}$ Supply current                     | All inputs and outputs open    | 1.8          | 3    |         | mA   |

switching characteristics over full range of recommended operating conditions

| PARAMETER                                             | TEST CONDITIONS                                             | MIN  | TYP | MAX     | UNIT    |

|-------------------------------------------------------|-------------------------------------------------------------|------|-----|---------|---------|

| $t_{P1}$ Pulse width at SENSE input                   | $V_{IH} = V_{Styp} - 200mV$<br>$V_{IL} = V_{Styp} - 200mV$  | 0.5  |     | $\mu s$ |         |

| $t_{PO}$ Pulse width at output                        | $C_1 = 0.1\mu F$                                            | 0.65 | 1.3 | 2.6     | ms      |

| $t_{PD}$ Propagation delay time from RESIN- to RESET- | $C_1 = 100\text{ pF}$ , $V_{CC} = 5V$                       |      | 9   |         | $\mu s$ |

| $t_{RF}$ Rise/Falltime at RESET and RESET-            | $C_1 = 100\text{ pF}$ , $V_{CC} = 5V$<br>$R_1 = 4.7k\Omega$ |      | 1   | $\mu s$ |         |

\*All characteristics are measured with capacitors of each  $C = 0.1\mu F$  across PIN1/GND and PIN3/GND

Functional Diagram

| Note 2: | $R_1$ typ. | $R_2$ typ. |

|---------|------------|------------|

| TL7702  | 0          | -          |

| TL7705  | 9.0k       | 10.0k      |

| TL7709  | 20.4k      | 10.0k      |

| TL7712  | 36.6k      | 10.0k      |

| TL7715  | 46.8k      | 10.0k      |

Mikrocomputer GmbH & Co. KG

Vaalser Straße 148

D-5100 Aachen

Telefon 02 41-87 0081

Telex 8 329 454 elzet d

Telefax 02 41-87 02 31