**Technische

Beschreibung

zum**

Speedmaster 5.3

Alle Rechte vorbehalten, insbesondere auch diejenigen aus der spezifischen Gestaltung, Anordnung und Einteilung des angebotenen Stoffes. Der auszugsweise oder teilweise Nachdruck sowie fotomechanische Wiedergabe oder Übertragung auf Datenträger zur Weiterverarbeitung ist untersagt und wird als Verstoß gegen das Urheberrechtsgesetz und als Verstoß gegen das Gesetz gegen den unlauteren Wettbewerb gerichtlich verfolgt. Für etwaige technische Fehler, sowie für die Richtigkeit aller in diesem Buch gemachten Angaben, übernehmen der Herausgeber und Autor keine Haftung.

Technische Beschreibung des SpeedMaster 5.3

=====

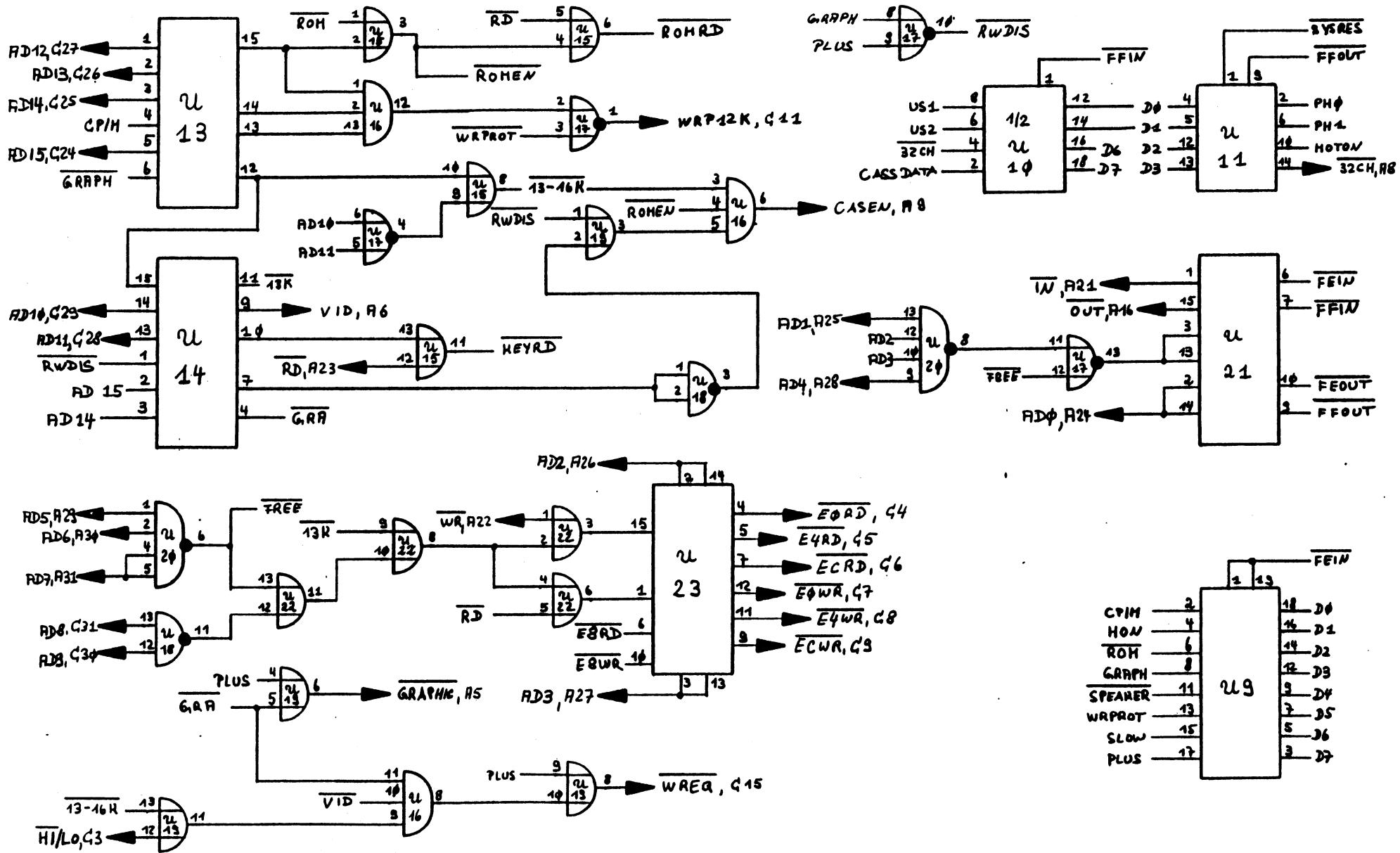

1. Prinzipieller Aufbau:

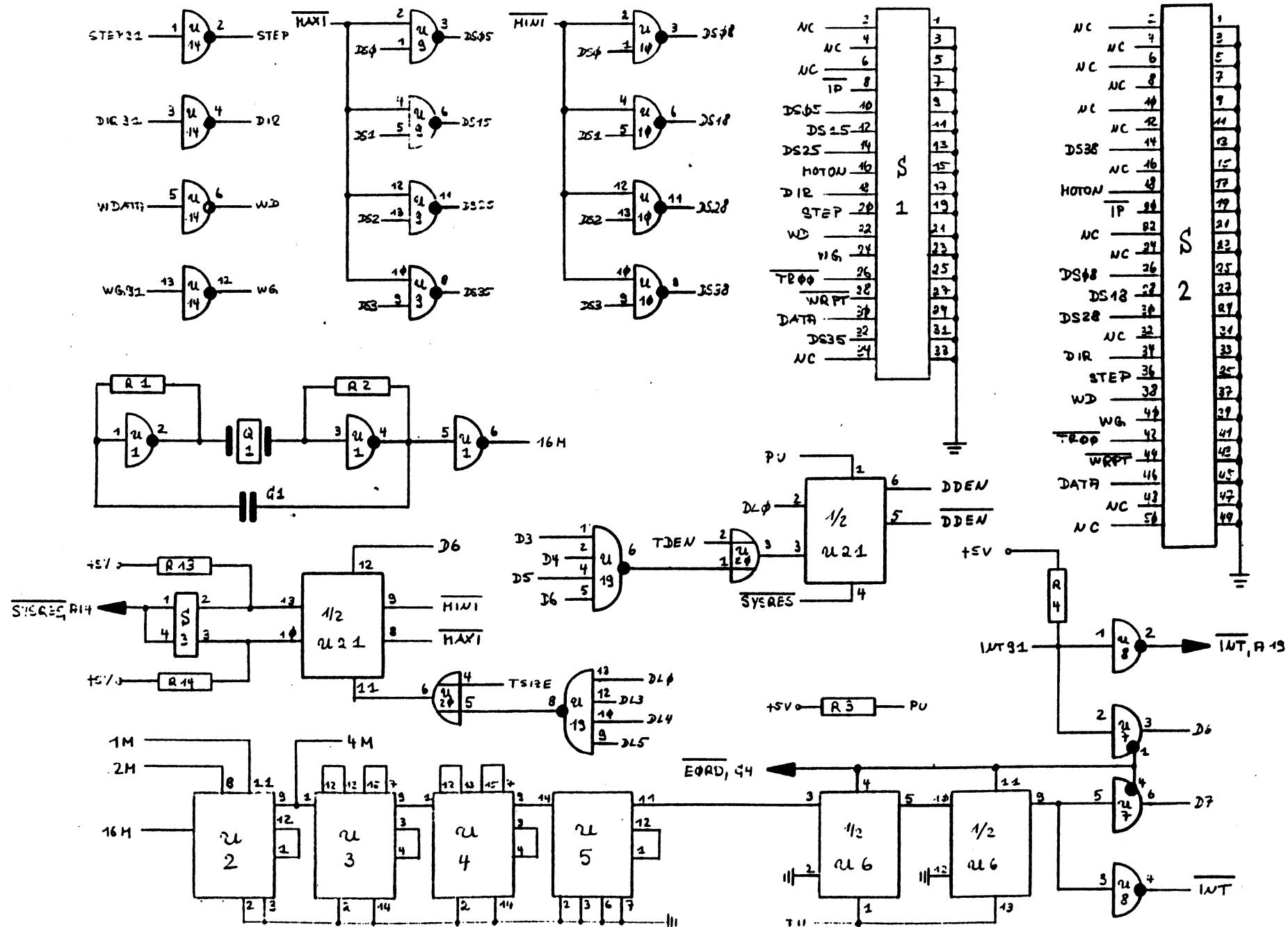

Beim SpeedMaster 5.3 handelt es sich um ein 19" Einschub-System. Die unter 2.-6. aufgeführten Baugruppen sind als Europakarten in 2 Lagen Feinleitertechnik gefertigt. Auf der BUS-Platine befinden sich außer den Steckplätzen für die Systembaugruppen noch 8 freie Plätze für Erweiterungen. Der BUS benutzt eine, von bekannten Belegungen abweichende Orientierung, um auch noch bis zu 8 MHz Taktfrequenz stabile Signale zu liefern.

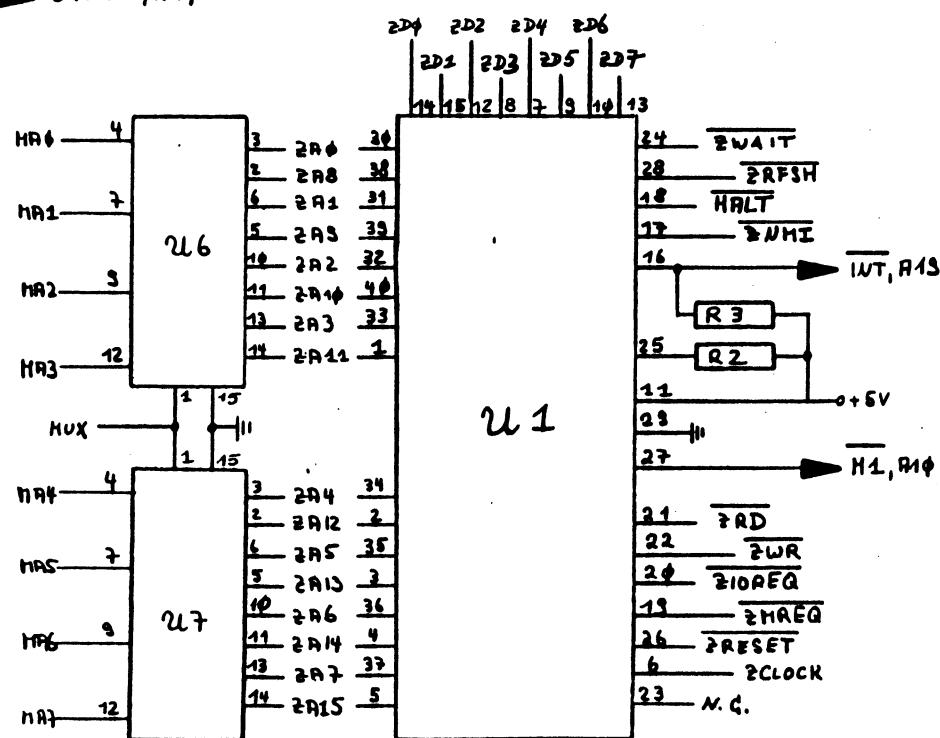

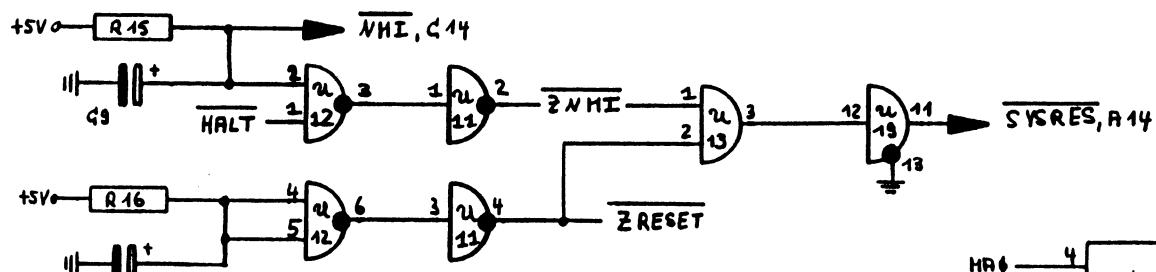

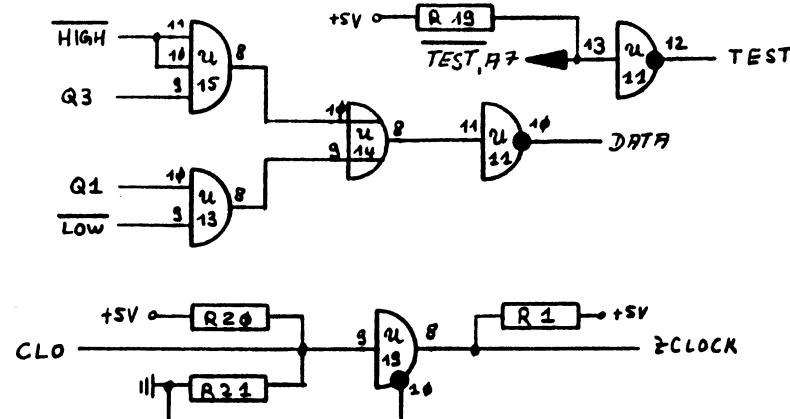

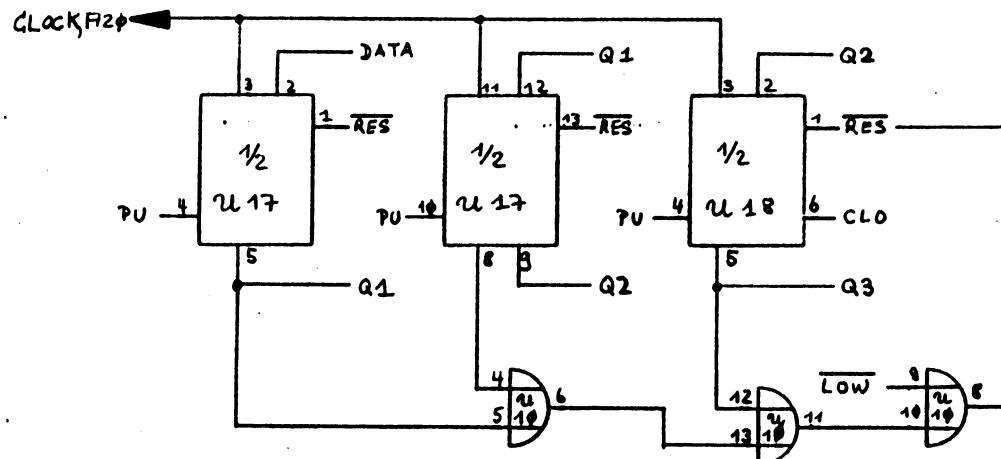

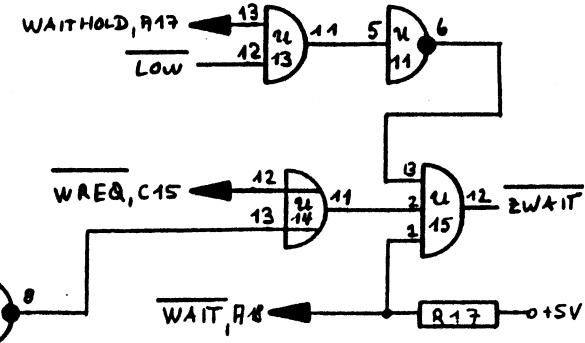

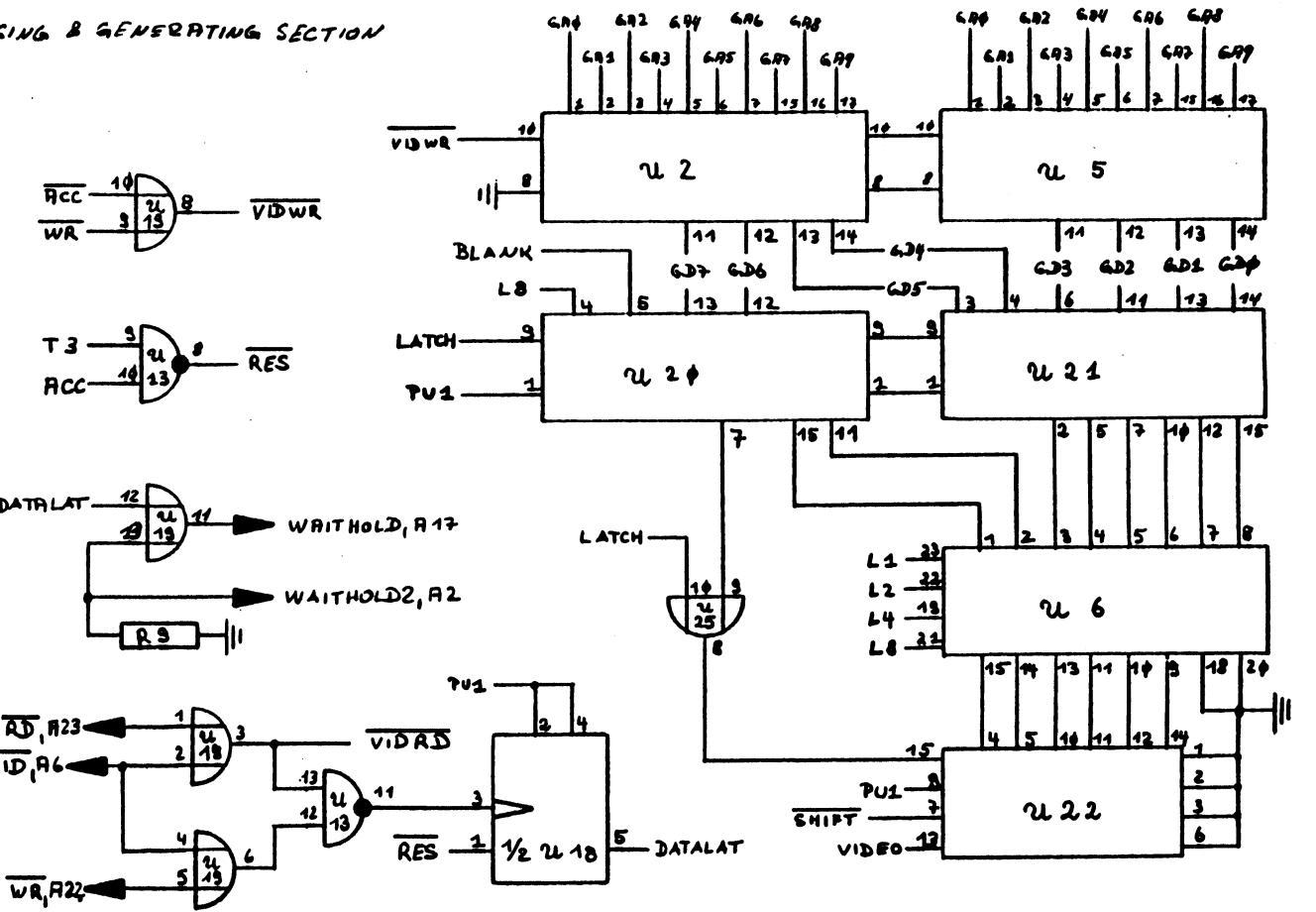

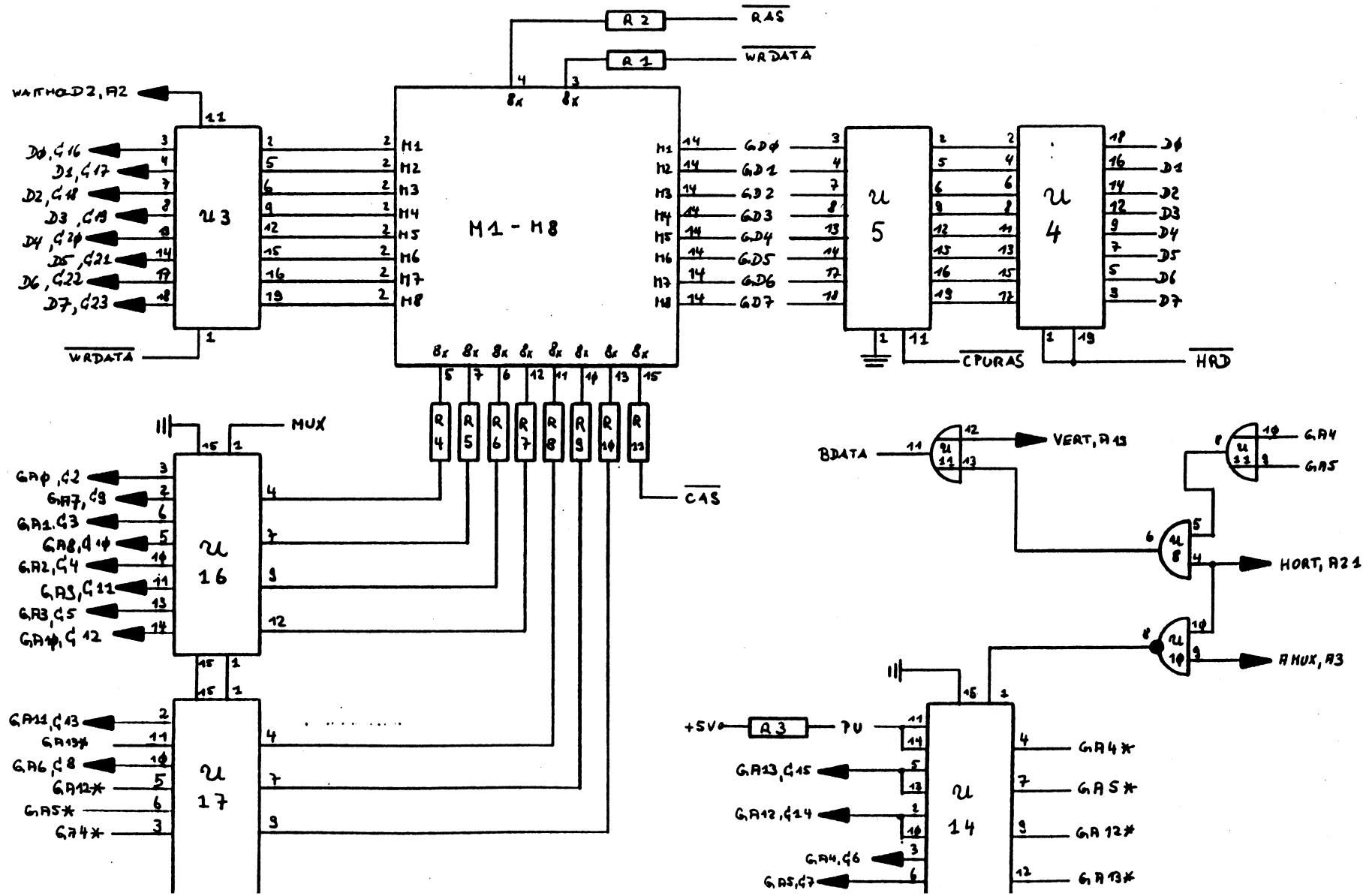

2. CPU und Speichergruppe

Als Prozessor wird eine Z-80-B CPU eingesetzt, die mit 5.35 MHz getaktet wird. Ein, in diesem System erstmalig einge- bauter Waitzyklus Generator dient zur vollständigen Synchronisation der Peripheriebaugruppen wie VIDEO, FLOPPY, KEY- BOARD usw. und erhöht die effektive Verarbeitungsgeschwindigkeit wesentlich. So entfallen zum Beispiel die störenden Streifen beim Zugriff der CPU auf den Videospeicher, ohne das auf die Blankingsignale der Videobaugruppe gewartet werden muß.

Auf der Platine CPU 1.0 befinden sich 64 k-Byte dynamische RAM's (4164 mit 150 ns Zugriffszeit), wobei sich die Kapazität über den BUS durch die Baugruppe RAM 2.0 auf bis zu 832 k-Byte erweitern lässt.

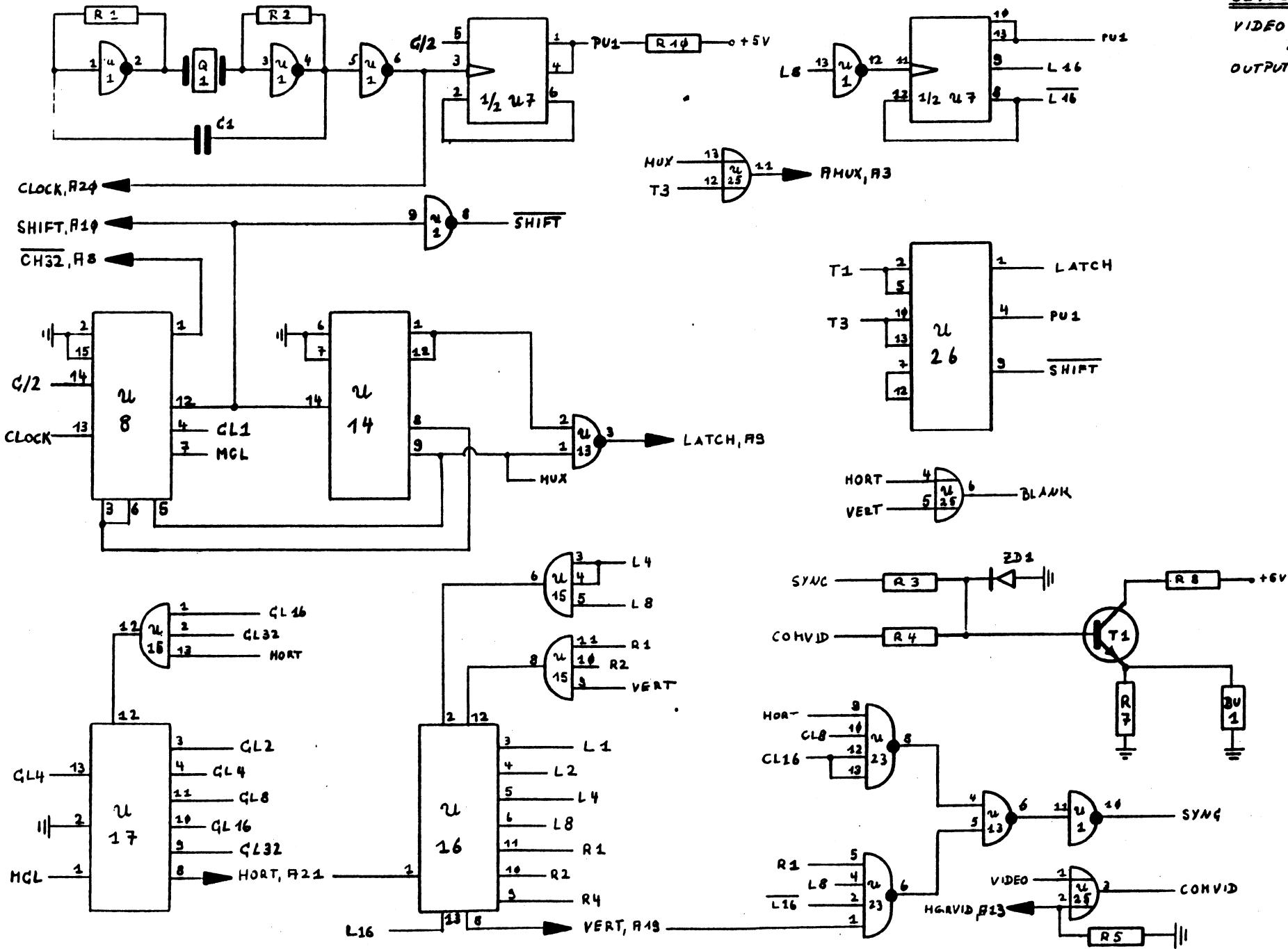

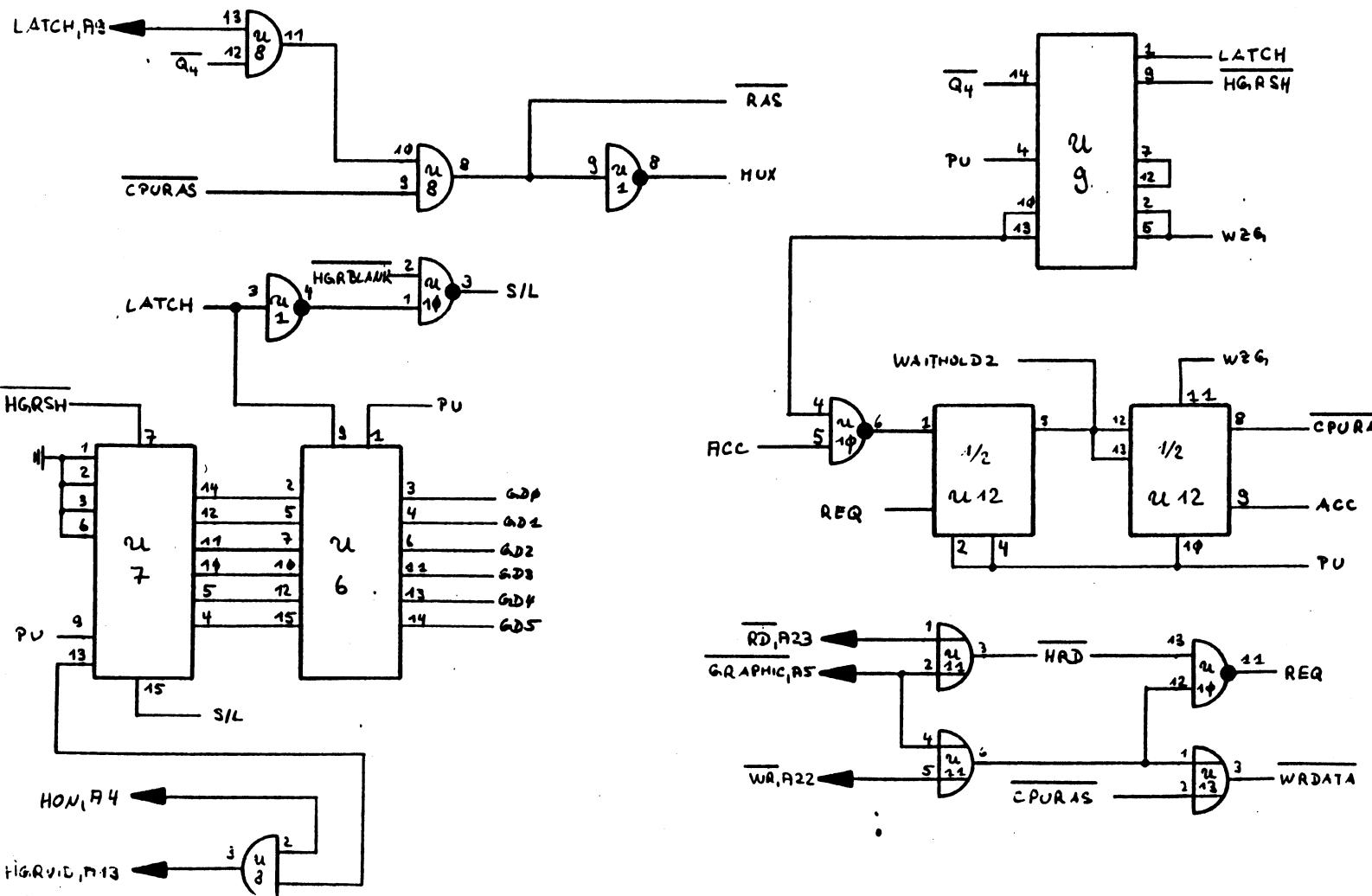

3. Video Baugruppe

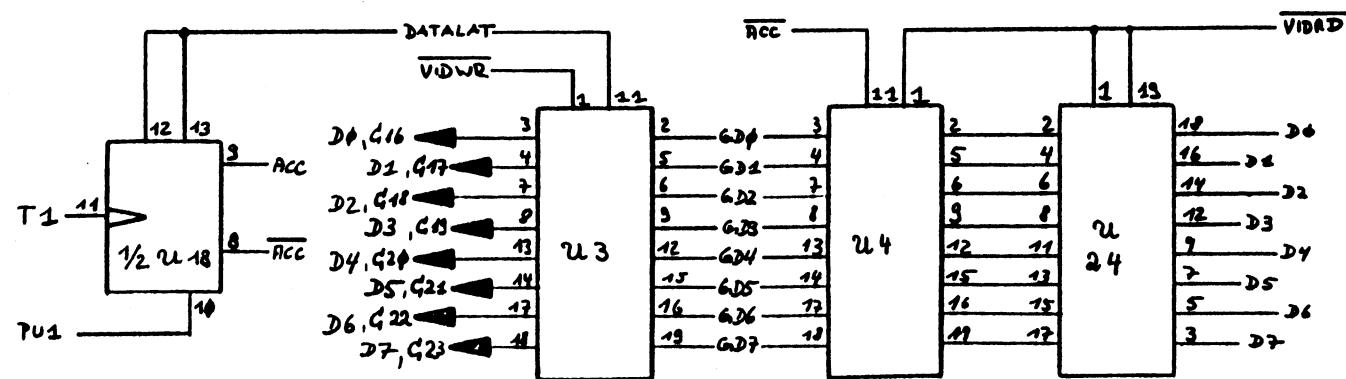

Die Baugruppe VIDEO 1.2 erlaubt es, ein Bildschirmformat von 64 Zeichen pro Zeile und 16 Zeilen pro Seite darzustellen. Durch Umschaltung der Auslesefrequenz kann bei Verdopplung der Zeichenbreite die Zeichenanzahl halbiert werden. Der Zeichensatz befindet sich in einem EPROM (2732) und kann, da alle IC's gesockelt sind, jederzeit ersetzt werden. Die Zeichenmatrix ist auf 6 x 12 festgelegt. Der Bildwiederhol- speicher besteht aus 1 k-Byte statischem RAM (2 x 2114) und belegt somit keinen Hauptspeicher. Das Videoausgangs- signal steht als BAS-Normsignal zur Verfügung. Zur gleichzeitigen Darstellung von Grafik (siehe 4.) und Text ist ein BIT IMAGE MISCHER mit ODER Funktion einge- baut.

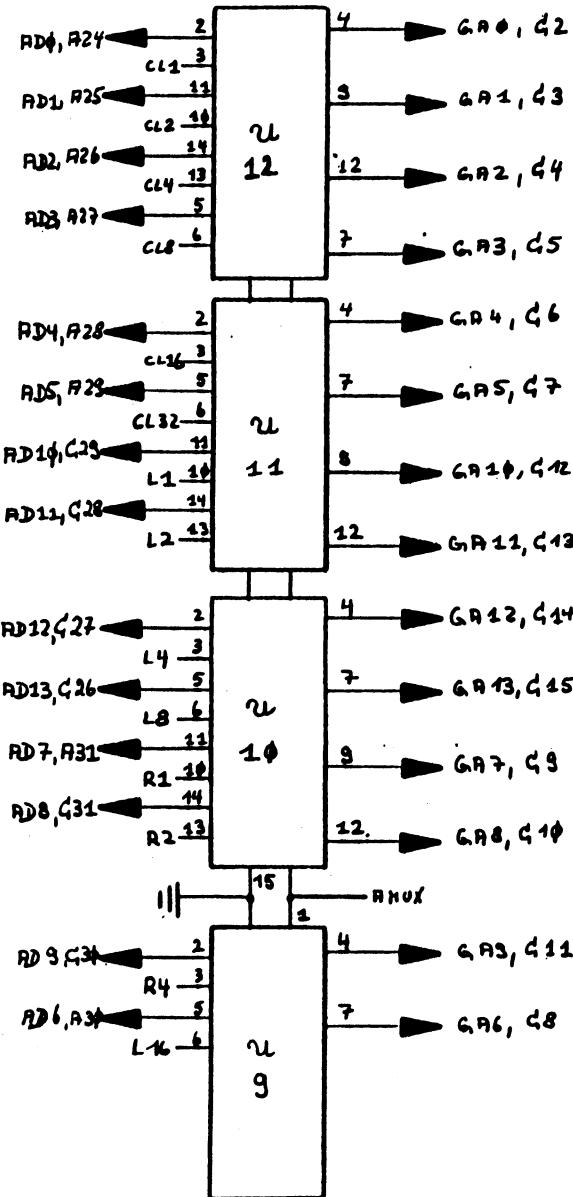

4. Grafik Baugruppe

16 k-Byte dynamische RAM's (4116 mit 150 ns Zugriffszeit) bilden den Grafikspeicher der Baugruppe GRAPHIC 1.5. Durch Erweiterung des von der Videokarte erzeugten Adressbereiches können 480 x 192 Punkte dargestellt werden, wobei eine gleichzeitige Darstellung mit der Textseite möglich ist (siehe 3.). Darüberhinaus kann ein Bildschirmformat von 24 x 80 erzeugt werden (CP/M).

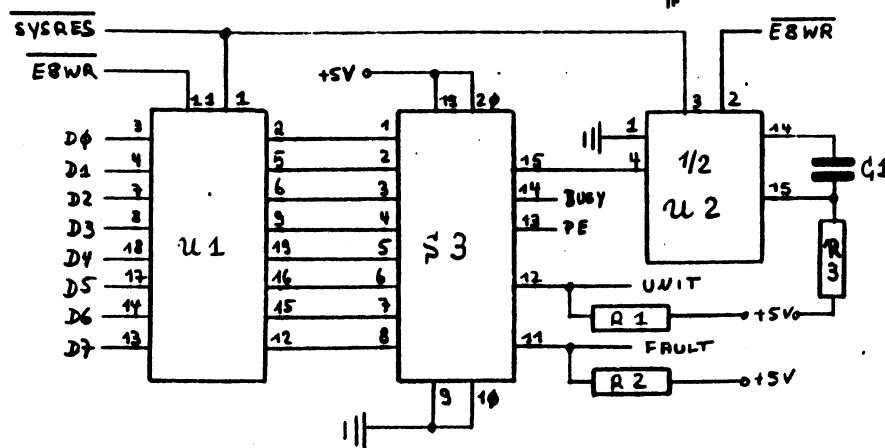

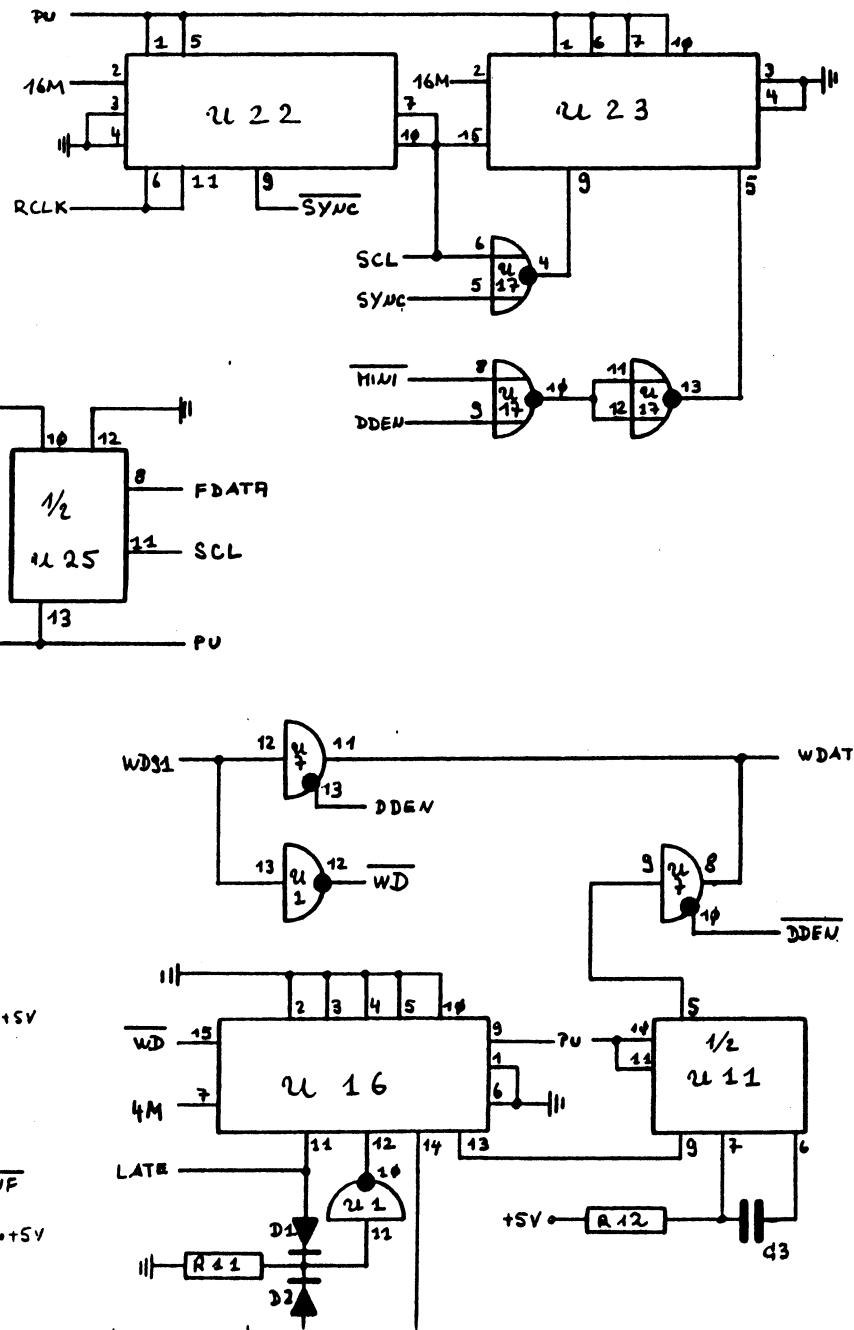

## 5. I/O Baugruppe

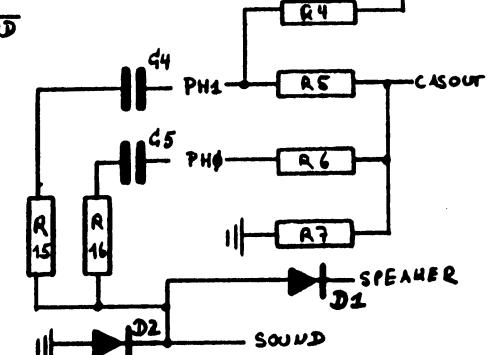

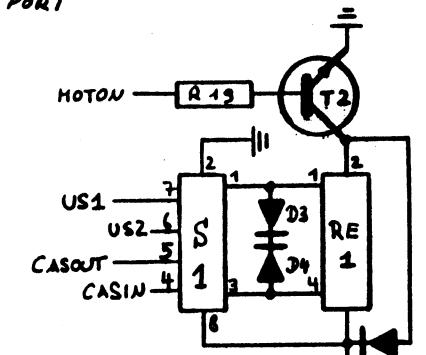

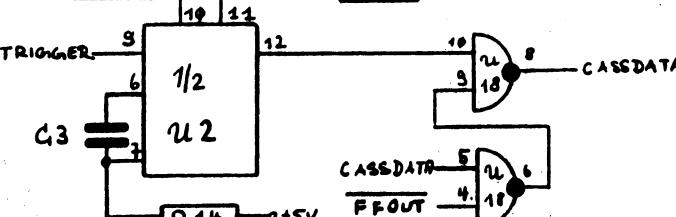

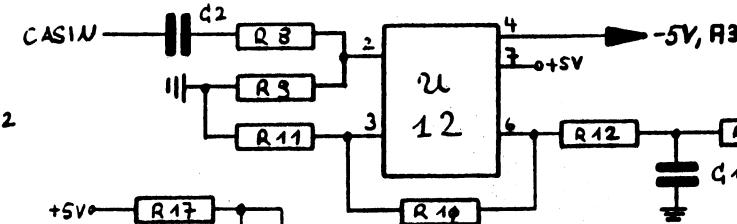

Auf der Platine I/O 1.1 befindet sich eine Centronics Parallel Schnittstelle mit 4 Hand-Shake-Leitungen und negativem Strobe. 4 k-Byte EPROM enthalten den Boot-Strap-Loader und einen Mini-Monitor. Über einen Pfostenstecker kann ein Kassettenrekorder angeschlossen werden. Außerdem ist natürlich ein Keyboard-Anschluß vorhanden.

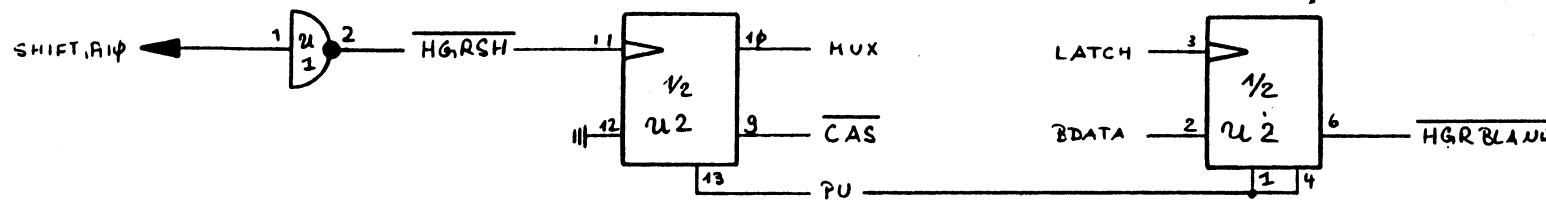

## 6. Floppy Baugruppe

Die Platine FLOPPY 5/8 A stellt für 5 1/4" und 8" je (!) einen Pfostenstecker zum Anschluß von bis zu 6 Laufwerken (3 x 5 1/4", 3 x 8") zur Verfügung. Dabei können 5 1/4" Laufwerke von Single-Sided, Single-Density bis Double-Sided, Double-Density und 8" Laufwerke Single/Double-Sided, Single-Density angeschlossen werden. Als Floppy Kontroller befindet sich der SAB 1791 - 2 auf der Platine. Über einen BOOT-Jumper kann die Laufwerksgröße, von der aus gebootet werden soll, vorgewählt werden. Außerdem liefert die Karte einen 25 ms System-Interrupt.

Achtung:

=====

Die Platine FLOPPY DS/DD ist ab sofort als Option lieferbar. Änderungen zu den oben genannten Spezifikationen sind:

1. Es können alle Laufwerke von Single-Side, Single-Density bis Double-Sided, Double-Density eingesetzt werden.

2. Die maximale Laufwerksanzahl erhöht sich auf 8. Über Jumper auch NEWDOS 80 Kompatibilität herstellbar.

3. Die Schreibdichte, mit der gebootet werden soll, ist voreinstellbar.

4. Als Floppy Kontroller kommt der SAB 2791 mit integriertem Daten-Separator und Write-Precompensations Logik zum Einsatz.

## 7. Keyboard

Das Keyboard ist als offene X-Y Matrix ausgelegt. Als Tasten werden hochwertige SIEMENS Module mit integrierter Diode für echten N-Key-Rollover verwendet. Der System RESET ist über 2 Tasten verriegelt. Eine internationale Auslegung der Tastatur (z. B. mit deutschen Umlauten) ist vorgesehen.

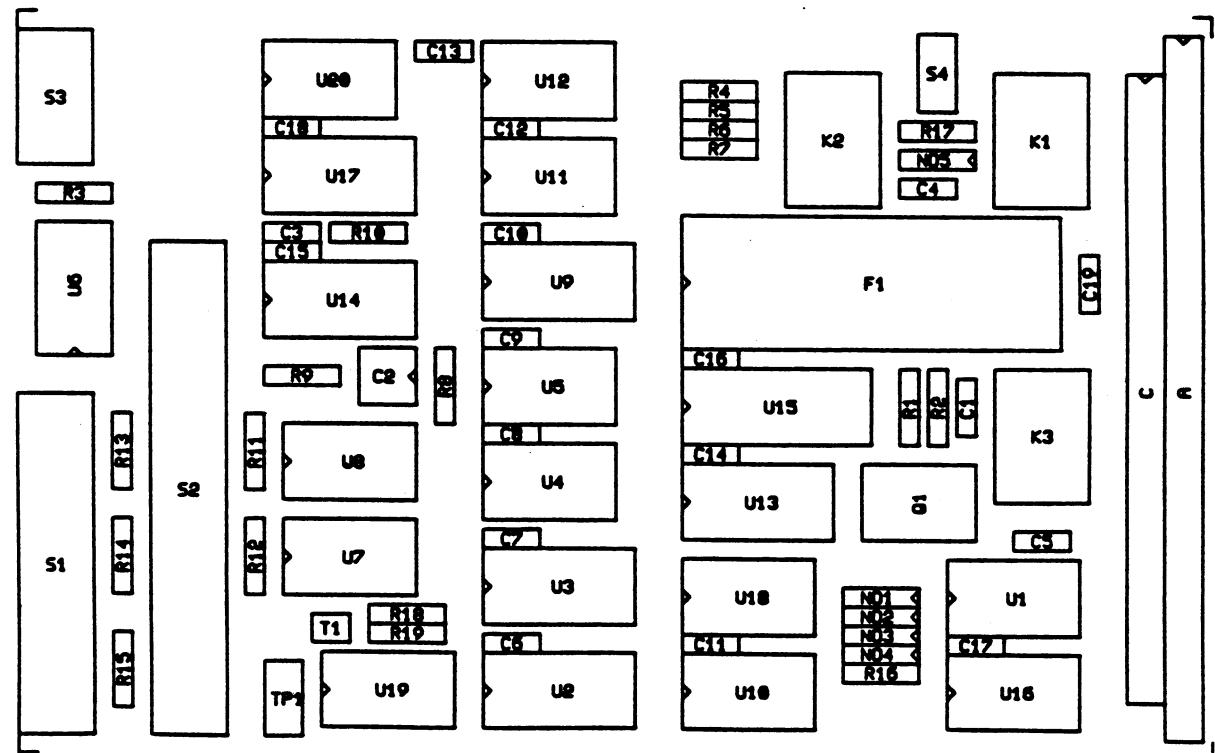

Passive Bauteile: SpeedMaster 5.3, CPU 1.0

## Wertordnung

| Widerstände: | Anzahl: | Bauteilname:   |

|--------------|---------|----------------|

| 33 Ohm       | 11      | R 4 - R 14     |

| 330 Ohm      | 1       | R 1            |

| 470 Ohm      | 2       | R 20 - 21      |

| 1 kOhm       | 3       | R 2, R 18 - 19 |

| 4.7 kOhm     | 2       | R 3, R 17      |

| 10 kOhm      | 2       | R 15 - 16      |

| Kondensatoren: | Anzahl: | Bauteilname: |

|----------------|---------|--------------|

| 100 nF         | 18      | C 1 - 8, C 1 |

| 10 uF          | 1       | C 9          |

| 47 uF          | 1       | C 10         |

Steckerleisten: Anzahl: Bauteilname:

----- ----- -----

VG. 64 pol. a+c 1 VG 1. A C

Passive Bauteile: SpeedMaster 5.3, CPU 1.0

=====

Rangordnung

Bauteilname:

Widerstand:

R 1

R 2

R 3

R 4 - 14

R 15 - 16

R 17

R 18 - 19

330 Ohm

1 kOhm

4.7 kOhm

33 Ohm

10 kOhm

4.7 kOhm

1 kOhm

Bauteilname:

Kapazität:

C 1 - 8

C 9

C 10

C 11 - 20

100 nF

10 uF

47 uF

100 nF

Bauteilname:

Bezeichnung:

VG 1, A C

Steckerleiste, VG, 64 pol. a+c

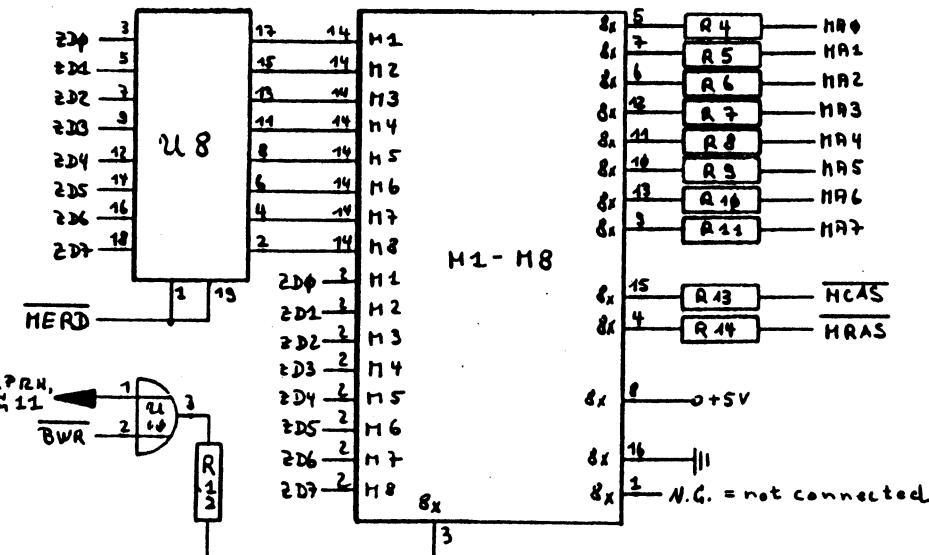

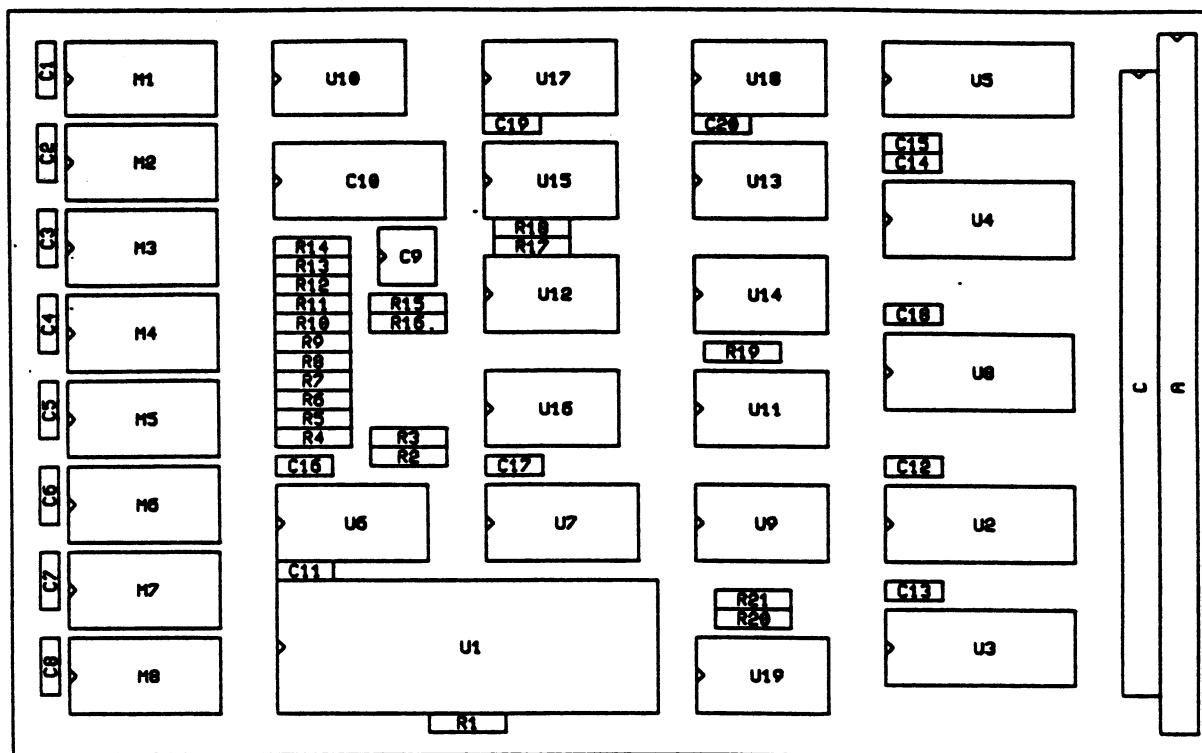

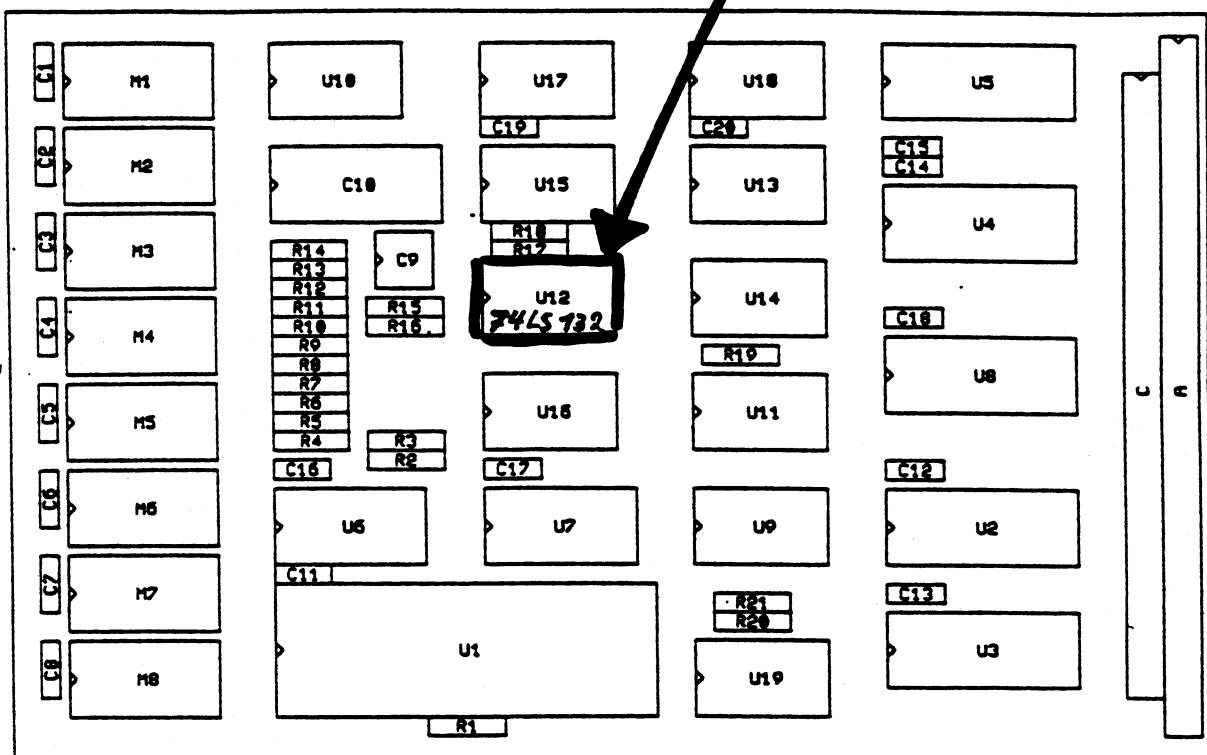

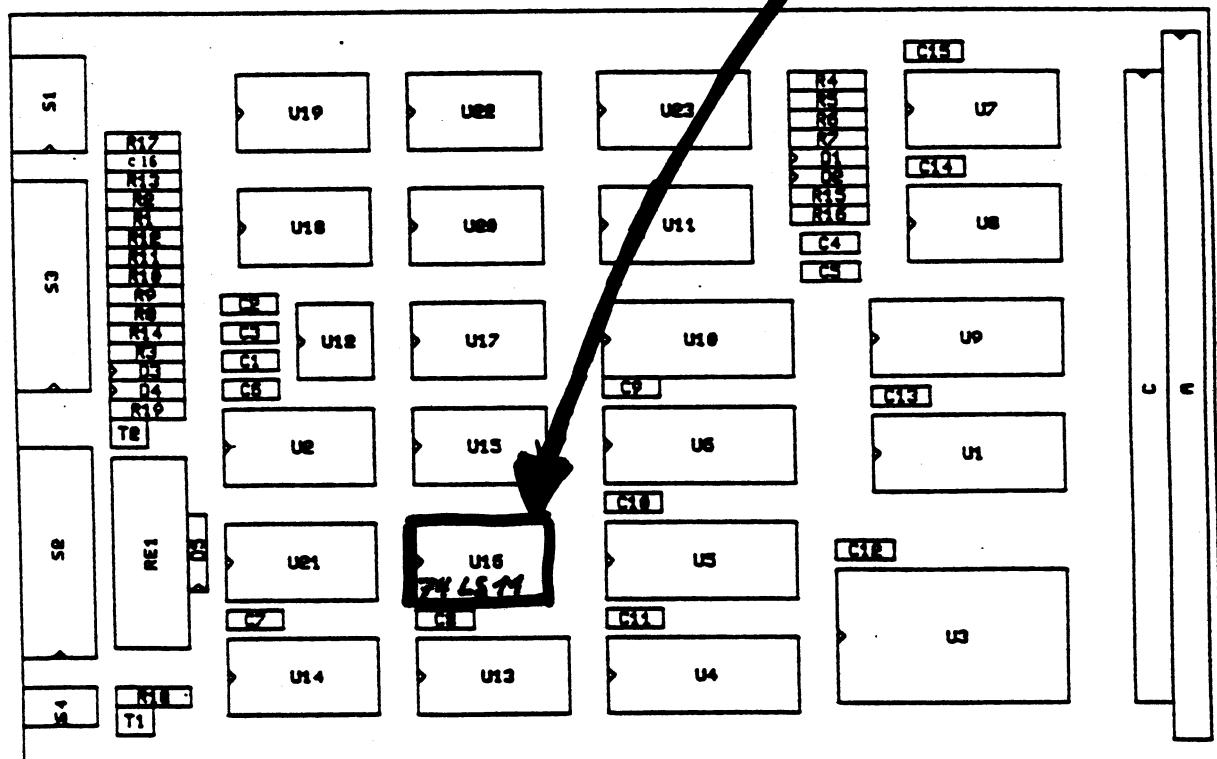

Aktive Bauteile: SpeedMaster 5.3, CPU 1.0

Wertordnung

=====

| TTL Baustein: | Anzahl: | Bauteilname:   |

|---------------|---------|----------------|

| 74 LS 04      | 1       | U 11           |

| 74 LS 08      | 1       | U 13           |

| 74 LS 11      | 1       | U 15           |

| 74 LS 32      | 3       | U 9 - 10, U 14 |

| 74 LS 74      | 1       | U 16           |

| 74 S 74       | 2       | U 17 - 18      |

| 74 LS 125     | 1       | U 19           |

| 74 LS 132     | 1       | U 12           |

| 74 S 157      | 2       | U 6 - 7        |

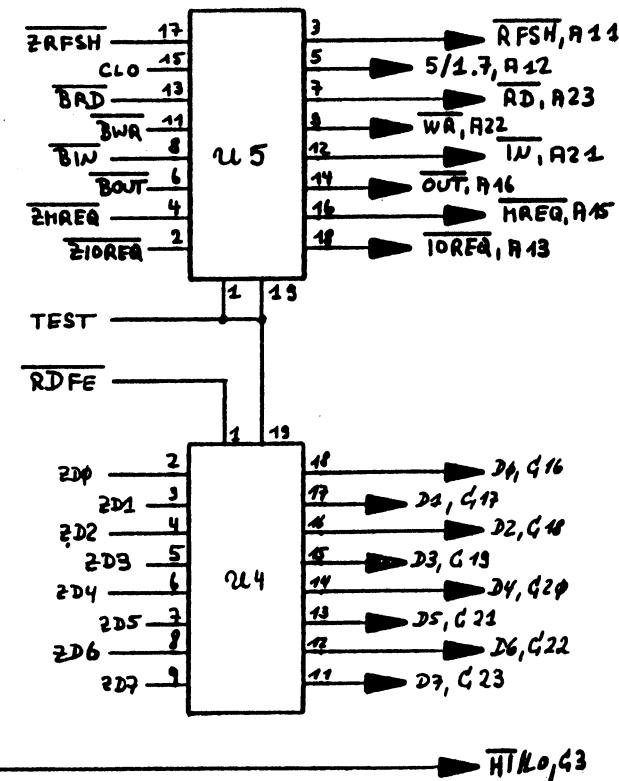

| 74 LS 244     | 2       | U 5, U 8       |

| 74 LS 245     | 3       | U 2 - 4        |

| Sonder IC's:     | Anzahl: | Bauteilname: |

|------------------|---------|--------------|

| Z-80-B CPU       | 1       | U 1          |

| NEC D 4164 C - 3 | 8       | M 1 - 8      |

Aktive Bauteile: SpeedMaster 5.3, CPU 1.0

=====

Rangordnung

| Bauteilname: | Bezeichnung:   |

|--------------|----------------|

| U 2 - 4      | TTL, 74 LS 245 |

| U 5          | TTL, 74 LS 244 |

| U 6 - 7      | TTL, 74 S 157  |

| U 8          | TTL, 74 LS 244 |

| U 9 - 10     | TTL, 74 LS 32  |

| U 11         | TTL, 74 LS 04  |

| U 12         | TTL, 74 LS 132 |

| U 13         | TTL, 74 LS 08  |

| U 14         | TTL, 74 LS 32  |

| U 15         | TTL, 74 LS 11  |

| U 16         | TTL, 74 LS 74  |

| U 17 - 18    | TTL, 74 S 74   |

| U 19         | TTL, 74 LS 125 |

| Bauteilname: | Bezeichnung:     |

|--------------|------------------|

| U 1          | Z-80-B CPU       |

| M 1 - 8      | NEC D 4164 C - 3 |

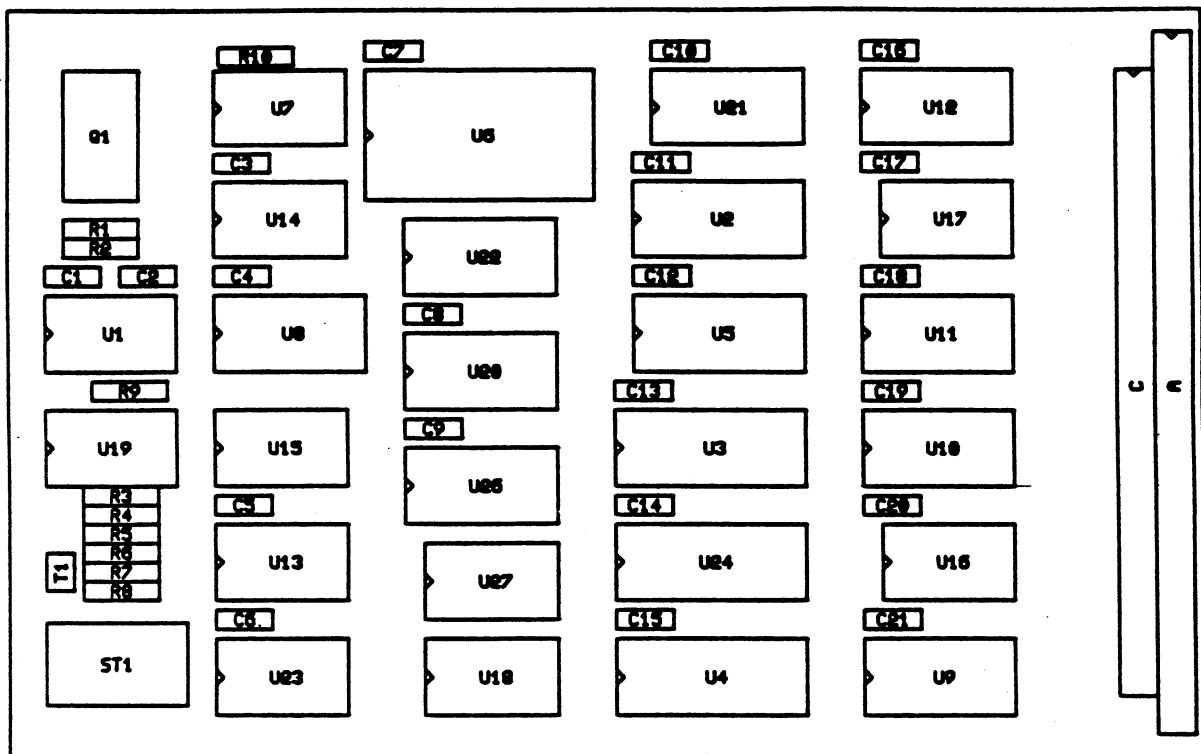

Passive Bauteile: SpeedMaster 5.3, I/O 1.1

=====

Wertordnung

| Widerstände: | Anzahl: | Bauteilname:    |

|--------------|---------|-----------------|

| 27 Ohm       | 1       | R 18            |

| 1 kOhm       | 2       | R 12, R 17      |

| 1.2 kOhm     | 1       | R 7             |

| 4.7 kOhm     | 3       | R 1 - 2, R 8    |

| 7.5 kOhm     | 2       | R 5 - 6         |

| 10 kOhm      | 3       | R 9, R 11, R 14 |

| 20 kOhm      | 2       | R 3, R 19       |

| 47 kOhm      | 2       | R 15 - 16       |

| 220 kOhm     | 1       | R 4             |

| 1 MOhm       | 1       | R 10            |

| Kondensatoren: | Anzahl: | Bauteilname:  |

|----------------|---------|---------------|

| 220 pF         | 1       | C 1           |

| 10 nF          | 2       | C 3, C 16     |

| 100 nF         | 13      | C 2, C 4 - 15 |

| Dioden:  | Anzahl: | Bauteilname: |

|----------|---------|--------------|

| 1 N 4148 | 5       | D 1 - 5      |

| Relais:         | Anzahl: | Bauteilname: |

|-----------------|---------|--------------|

| Hamlin, 1 x ein | 1       | RE 1         |

| Steckerleisten: | Anzahl: | Bauteilname: |

|-----------------|---------|--------------|

| 2 polig         | 1       | S 4          |

| 8 polig         | 1       | S 1          |

| 20 polig        | 2       | S 2 - 3      |

| VG, 64 pol. a+c | 1       | VG 1, A C    |

| Sonderbauteile: | Anzahl: | Bauteilname: |

|-----------------|---------|--------------|

| Drahtbrücke     | 1       | R 13         |

Passive Bauteile: SpeedMaster 5.3, I/O 1.1

=====

Rangordnung

Bauteilname:

Widerstand:

|           |     |      |

|-----------|-----|------|

| R 1 - 2   | 4.7 | kOhm |

| R 3       | 20  | kOhm |

| R 4       | 220 | kOhm |

| R 5 - 6   | 7.5 | kOhm |

| R 7       | 1.2 | kOhm |

| R 8       | 4.7 | kOhm |

| R 9       | 10  | kOhm |

| R 10      | 1   | MOhm |

| R 11      | 10  | kOhm |

| R 12      | 1   | kOhm |

| R 14      | 10  | kOhm |

| R 15 - 16 | 47  | kOhm |

| R 17      | 1   | kOhm |

| R 18      | 27  | Ohm  |

| R 19      | 20  | kOhm |

Bauteilname:

Kapazität:

|          |     |    |

|----------|-----|----|

| C 1      | 220 | pF |

| C 2      | 100 | nF |

| C 3      | 10  | nF |

| C 4 - 15 | 100 | nF |

| C 16     | 10  | nF |

Bauteilname:

Bezeichnung:

D 1 - 5

Diode, 1 N 4148

Bauteilname:

Bezeichnung:

RE 1

Relais, Hamlin, 1 x ein

Bauteilname:

Bezeichnung

|           |                                |

|-----------|--------------------------------|

| S 1       | Steckerleiste, 8 polig         |

| S 2 - 3   | Steckerleiste, 20 polig        |

| S 4       | Steckerleiste, 2 polig         |

| VG 1, A C | Steckerleiste, VG, 64 pol. a+c |

Bauteilname:

Bezeichnung:

R 13

Drahtbrücke

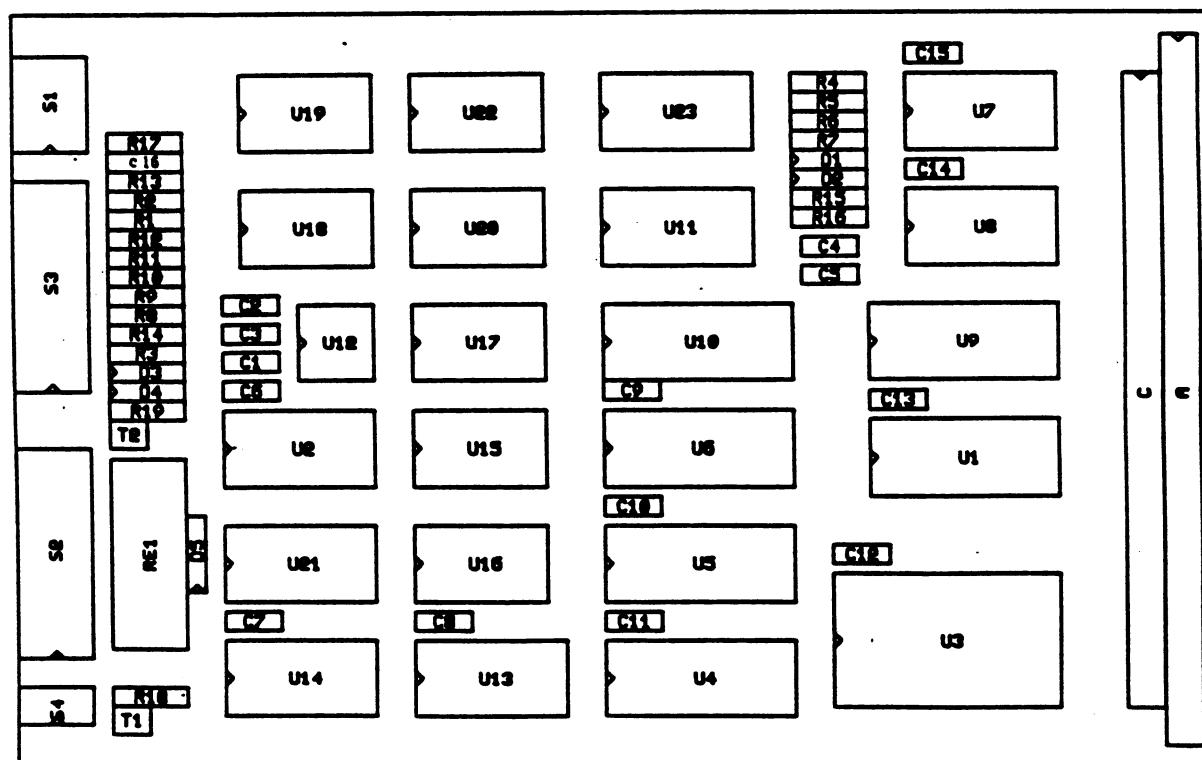

Aktive Bauteile: SpeedMaster 5.3, I/O 1.1

=====

Wertordnung

Transistoren: Anzahl: Bauteilname:

----- ----- -----

|        |   |     |

|--------|---|-----|

| BC 107 | 1 | T 2 |

| BC 517 | 1 | T 1 |

TTL Baustein: Anzahl: Bauteilname:

----- ----- -----

|           |   |                  |

|-----------|---|------------------|

| 74 LS 00  | 1 | U 18             |

| 74 LS 02  | 1 | U 17             |

| 74 LS 11  | 1 | U 16             |

| 74 LS 20  | 1 | U 20             |

| 74 LS 32  | 3 | U 15, U 19, U 22 |

| 74 LS 123 | 1 | U 2              |

| 74 LS 138 | 1 | U 13             |

| 74 LS 139 | 3 | U 14, U 21, U 23 |

| 74 LS 175 | 2 | U 7 - 8          |

| 74 LS 175 | 1 | U 11             |

| 74 LS 240 | 2 | U 5 - 6          |

| 74 LS 244 | 3 | U 4, U 9 - 10    |

| 74 LS 273 | 1 | U 1              |

Sonder IC's: Anzahl: Bauteilname:

----- ----- -----

|                  |   |      |

|------------------|---|------|

| uA 741           | 1 | U 12 |

| EPROM 2732 (350) | 1 | U 3  |

Aktive Bauteile: SpeedMaster 5.3, I/O 1.1 Rangordnung

=====

Bauteilname: Bezeichnung:

-----

T 1 Transistor, BC 517

T 2 Transistor, BC 571

Bauteilname: Bezeichnung:

-----

|          |                |

|----------|----------------|

| U 1      | TTL, 74 LS 273 |

| U 2      | TTL, 74 LS 123 |

| U 4      | TTL, 74 LS 244 |

| U 5 - 6  | TTL, 74 LS 240 |

| U 7 - 8  | TTL, 74 LS 175 |

| U 9 - 10 | TTL, 74 LS 244 |

| U 11     | TTL, 74 175    |

| U 13     | TTL, 74 LS 138 |

| U 14     | TTL, 74 LS 139 |

| U 15     | TTL, 74 LS 32  |

| U 16     | TTL, 74 LS 11  |

| U 17     | TTL, 74 LS 02  |

| U 18     | TTL, 74 LS 00  |

| U 19     | TTL, 74 LS 32  |

| U 20     | TTL, 74 LS 20  |

| U 21     | TTL, 74 LS 139 |

| U 22     | TTL, 74 LS 32  |

| U 23     | TTL, 74 LS 139 |

Bauteilname: Bezeichnung:

-----

U 3 EPROM 2732 (350)

U 12 uA 741

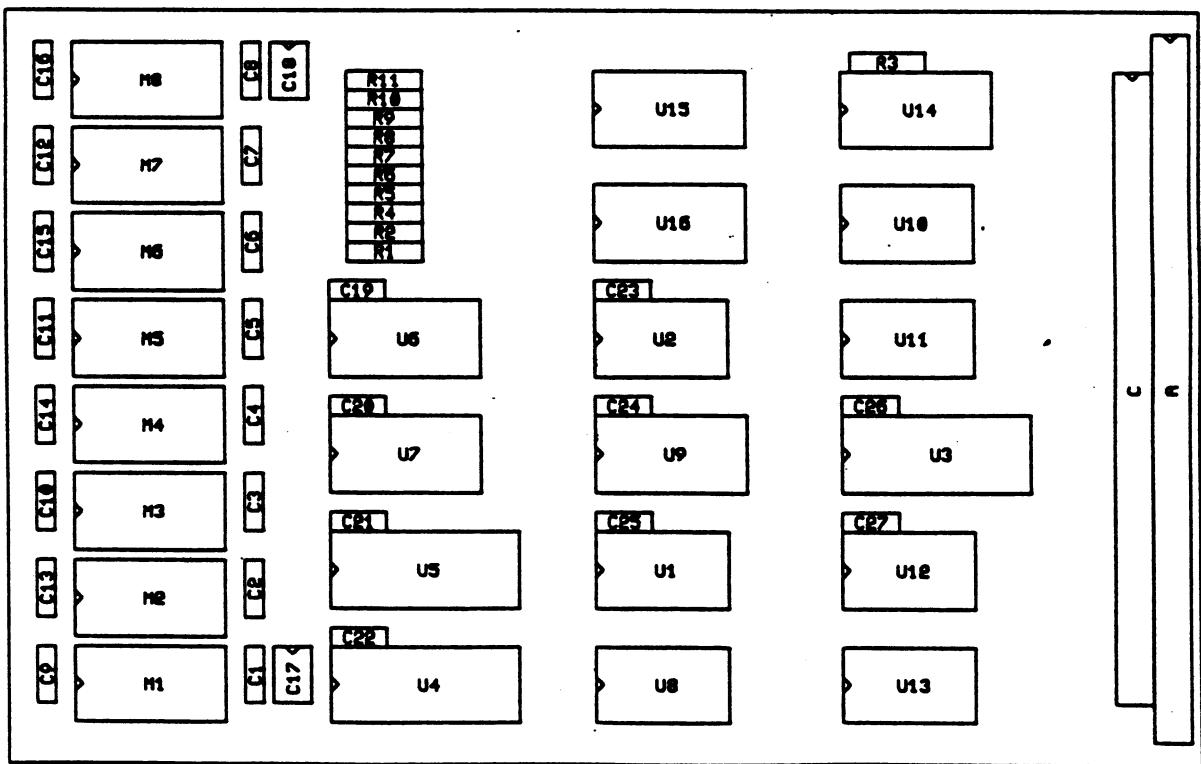

Passive Bauteile: SpeedMaster 5.3, VIDEO 1.2      Wertordnung

=====

| Widerstände: | Anzahl: | Bauteilname:                   |

|--------------|---------|--------------------------------|

| 10    Ohm    | 1       | R    8                         |

| 75    Ohm    | 1       | R    7                         |

| 470    Ohm   | 5       | R    1 - 2, R    4 - 5, R    9 |

| 1    kOhm    | 2       | R    3, R    10                |

| Kondensatoren: | Anzahl: | Bauteilname: |

|----------------|---------|--------------|

| 470    pF      | 1       | C    1       |

| 100    nF      | 20      | C    2 - 21  |

| Dioden:  | Anzahl: | Bauteilname: |

|----------|---------|--------------|

| ZD 2.4 V | 1       | ZD    1      |

| Quarze:  | Anzahl: | Bauteilname: |

|----------|---------|--------------|

| 10.7 MHz | 1       | Q    1       |

| Steckerleisten: | Anzahl: | Bauteilname: |

|-----------------|---------|--------------|

| VG, 64 pol. a+c | 1       | VG 1, A C    |

| Buchsen:           | Anzahl: | Bauteilname: |

|--------------------|---------|--------------|

| ToBu 3, Hirschmann | 1       | BU    1      |

Achtung:

=====

R    6 entfällt.

Passive Bauteile: SpeedMaster 5.3, VIDEO 1.2 Rangordnung

**Bauteilname:** \_\_\_\_\_ **Widerstand:** \_\_\_\_\_

|         |     |      |

|---------|-----|------|

| R 1 - 2 | 470 | Ohm  |

| R 3     | 1   | kOhm |

| R 4 - 5 | 470 | Ohm  |

| R 7     | 75  | Ohm  |

| R 8     | 10  | Ohm  |

| R 9     | 470 | Ohm  |

| R 10    | 1   | kOhm |

Bauteilname: \_\_\_\_\_ Kapazität: \_\_\_\_\_

C 1 470 pF

C 2 100 nF

**Bauteilname:** **Bezeichnung:**

ZD 1 Zener-Diode, 2.4 Volt, 500 mW

**Bauteilname:** **Bezeichnung:**

**Bauteilname:**    **Bezeichnung:**

VG 1, A C Steckerleiste, VG, 64 pol. a+c

**Bauteilname:** \_\_\_\_\_ **Bezeichnung:** \_\_\_\_\_

BU 1 Buchse, ToBu 3, Hirschmann

## Achtung:

---

R 6 entfällt.

Aktive Bauteile: SpeedMaster 5.3, VIDEO 1.2

=====

- Wertordnung

Transistoren: Anzahl: Bauteilname:

-----

BC 107 1 T 1

TTL Baustein: Anzahl: Bauteilname:

-----

|           |   |            |

|-----------|---|------------|

| 74 S 04   | 1 | U 1        |

| 74 LS 11  | 1 | U 15       |

| 74 LS 20  | 1 | U 23       |

| 74 LS 32  | 2 | U 19, U 25 |

| 74 LS 37  | 1 | U 13       |

| 74 LS 74  | 2 | U 7, U 18  |

| 74 LS 92  | 1 | U 14       |

| 74 LS 157 | 4 | U 9 - 12   |

| 74 157    | 1 | U 8        |

| 74 LS 166 | 1 | U 22       |

| 74 LS 174 | 1 | U 21       |

| 74 LS 175 | 2 | U 20, U 26 |

| 74 LS 244 | 1 | U 24       |

| 74 LS 374 | 2 | U 3 - 4    |

| 74 LS 393 | 2 | U 16 - 17  |

Sonder IC's Anzahl: Bauteilname:

-----

|                  |   |          |

|------------------|---|----------|

| uPD 2114 LC - 3  | 2 | U 2, U 5 |

| EPROM 2732 (350) | 1 | U 6      |

Aktive Bauteile: SpeedMaster 5.3, VIDEO 1.2

Rangordnung

=====

Bauteilname:

-----

T 1

Bezeichnung:

-----

Transistor, BC 107

Bauteilname:

-----

U 1

U 3 - 4

U 7

U 8

U 9 - 12

U 13

U 14

U 15

U 16 - 17

U 18

U 19

U 20

U 21

U 22

U 23

U 24

U 25

U 26

Bezeichnung:

-----

TTL, 74 S 04

TTL, 74 LS 374

TTL, 74 LS 74

TTL, 74 157

TTL, 74 LS 157

TTL, 74 LS 37

TTL, 74 LS 92

TTL, 74 LS 11

TTL, 74 LS 393, nicht Texas Ins.

TTL, 74 LS 74

TTL, 74 LS 32

TTL, 74 LS 175

TTL, 74 LS 174

TTL, 74 LS 166

TTL, 74 LS 20

TTL, 74 LS 244

TTL, 74 LS 32

TTL, 74 LS 175

Bauteilname:

-----

U 2

U 5

U 6

Bezeichnung:

-----

uPD 2114 LC - 3

uPD 2114 LC - 3

EPROM 2732 (350)

Passive Bauteile: SpeedMaster 5.3, GRAPHIC 1.5 Wertordnung

=====

| Widerstände: | Anzahl: | Bauteilname:      |

|--------------|---------|-------------------|

| 33 Ohm       | 10      | R 1 - 2, R 4 - 11 |

| 1 kOhm       | 1       | R 3               |

| Kondensatoren: | Anzahl: | Bauteilname:        |

|----------------|---------|---------------------|

| 100 nF         | 25      | C 1 - 16, C 19 - 27 |

| 10 uF          | 2       | C 17 - 18           |

| Steckerleisten: | Anzahl: | Bauteilname: |

|-----------------|---------|--------------|

| VG, 64 pol. a+c | 1       | VG 1, A C    |

Passive Bauteile: SpeedMaster 5.3, GRAPHIC 1.5 Rangordnung

=====

Bauteilname: Widerstand:

|          |        |

|----------|--------|

| R 1 - 2  | 33 Ohm |

| R 3      | 1 kOhm |

| R 4 - 11 | 33 Ohm |

Bauteilname: Kapazität:

|           |        |

|-----------|--------|

| C 1 - 16  | 100 nF |

| C 17 - 18 | 10 uF  |

| C 19 - 27 | 100 nF |

Bauteilname: Bezeichnung:

|           |                                |

|-----------|--------------------------------|

| VG 1, A C | Steckerleiste, VG, 64 pol. a/c |

|-----------|--------------------------------|

Aktive Bauteile: SpeedMaster 5.3, GRAPHIC 1.5 Wertordnung

=====

TTL Baustein: Anzahl: Bauteilname:

----- ----- -----

|           |   |            |

|-----------|---|------------|

| 74 LS 00  | 1 | U 10       |

| 74 LS 04  | 1 | U 1        |

| 74 LS 08  | 1 | U 8        |

| 74 LS 32  | 2 | U 11, U 13 |

| 74 LS 74  | 2 | U 2, U 12  |

| 74 LS 157 | 2 | U 15 - 16  |

| 74 S 157  | 1 | U 14       |

| 74 LS 166 | 1 | U 7        |

| 74 LS 174 | 1 | U 6        |

| 74 LS 175 | 1 | U 9        |

| 74 LS 244 | 1 | U 4        |

| 74 LS 374 | 2 | U 3, U 5   |

Sonder IC's Anzahl: Bauteilname:

----- ----- -----

|                 |   |         |

|-----------------|---|---------|

| NEC D 416 C - 3 | 8 | M 1 - 8 |

|-----------------|---|---------|

Aktive Bauteile: SpeedMaster 5.3, GRAPHIC 1.5 Rangordnung

=====

| Bauteilname: | Bezeichnung:   |

|--------------|----------------|

| U 1          | TTL, 74 LS 04  |

| U 2          | TTL, 74 LS 74  |

| U 3          | TTL, 74 LS 374 |

| U 4          | TTL, 74 LS 244 |

| U 5          | TTL, 74 LS 374 |

| U 6          | TTL, 74 LS 174 |

| U 7          | TTL, 74 LS 166 |

| U 8          | TTL, 74 LS 08  |

| U 9          | TTL, 74 LS 175 |

| U 10         | TTL, 74 LS 00  |

| U 11         | TTL, 74 LS 32  |

| U 12         | TTL, 74 LS 74  |

| U 13         | TTL, 74 LS 32  |

| U 14         | TTL, 74 S 157  |

| U 15 - 16    | TTL, 74 LS 157 |

| Bauteilname: | Bezeichnung:    |

|--------------|-----------------|

| M 1 - 8      | NEC D 416 C - 3 |

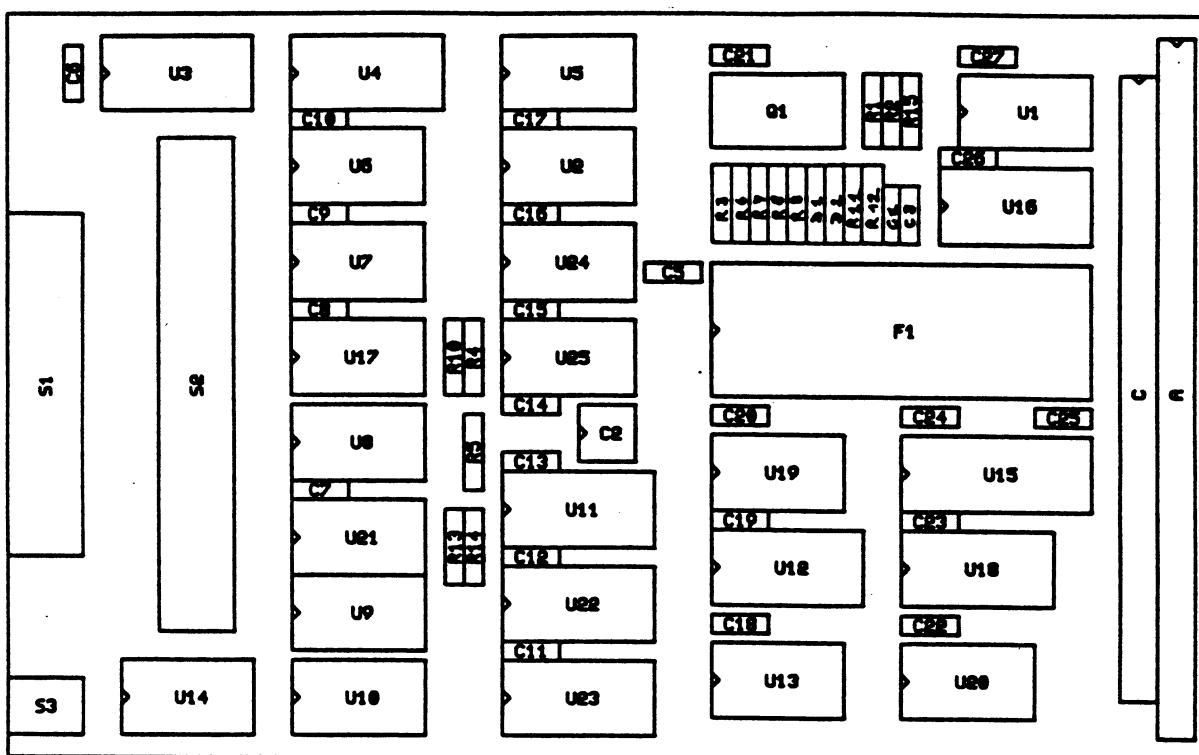

Passive Bauteile: SpeedMaster 5.3, FLOPPY 5/8 A Wertordnung

=====

Widerstände: Anzahl: Bauteilname:

|          |   |                           |

|----------|---|---------------------------|

| 330 Ohm  | 4 | R 7 - 9, R 15             |

| 470 Ohm  | 3 | R 1 - 2, R 11             |

| 1 kOhm   | 2 | R 3, R 12                 |

| 10 kOhm  | 5 | R 4, R 6, R 10, R 13 - 14 |

| 560 kOhm | 1 | R 5                       |

Kondensatoren: Anzahl: Bauteilname:

|        |    |          |

|--------|----|----------|

| 470 pF | 1  | C 3      |

| 1 nF   | 1  | C 1      |

| 100 nF | 23 | C 5 - 27 |

| 10 uF  | 1  | C 2      |

Dioden: Anzahl: Bauteilname:

|          |   |         |

|----------|---|---------|

| 1 N 4148 | 2 | D 1 - 2 |

|----------|---|---------|

Quarze: Anzahl: Bauteilname:

|          |   |     |

|----------|---|-----|

| 16.0 MHz | 1 | Q 1 |

|----------|---|-----|

Steckerleisten: Anzahl: Bauteilname:

|                 |   |           |

|-----------------|---|-----------|

| 4 polig         | 1 | S 3       |

| 34 polig        | 1 | S 1       |

| 50 polig        | 1 | S 2       |

| VG, 64 pol. a+c | 1 | VG 1, A C |

Kodierstecker: Anzahl: Bauteilname:

|         |   |      |

|---------|---|------|

| 2.54 mm | 1 | KD 1 |

|---------|---|------|

Achtung:

=====

C 4 entfällt.

Passive Bauteile: SpeedMaster 5.3, FLOPPY 5/8 A Rangordnung

=====

Bauteilname: Widerstand:

-----

|           |          |

|-----------|----------|

| R 1 - 2   | 470 Ohm  |

| R 3       | 1 kOhm   |

| R 4       | 10 kOhm  |

| R 5       | 560 kOhm |

| R 6       | 10 kOhm  |

| R 7 - 9   | 330 Ohm  |

| R 10      | 10 kOhm  |

| R 11      | 470 Ohm  |

| R 12      | 1 kOhm   |

| R 13 - 14 | 10 kOhm  |

| R 15      | 330 Ohm  |

Bauteilname: Kapazität:

-----

|          |        |

|----------|--------|

| C 1      | 1 nF   |

| C 2      | 10 uF  |

| C 3      | 470 pF |

| C 5 - 27 | 100 nF |

Bauteilname: Bezeichnung:

-----

D 1 - 2 Diode, 1 N 4148

Bauteilname: Bezeichnung:

-----

Q 1 Quarz, 16.0 MHz

Bauteilname: Bezeichnung:

-----

|           |                                |

|-----------|--------------------------------|

| S 1       | Steckerleiste, 34 polig        |

| S 2       | Steckerleiste, 50 polig        |

| S 3       | Steckerleiste, 4 polig         |

| VG 1, A C | Steckerleiste, VG, 64 pol. a+c |

Buteilname: Bezeclinung:

-----

KD 1 Kodierstecker, 2.54 mm

Achtung:

=====

C 4 entfällt.

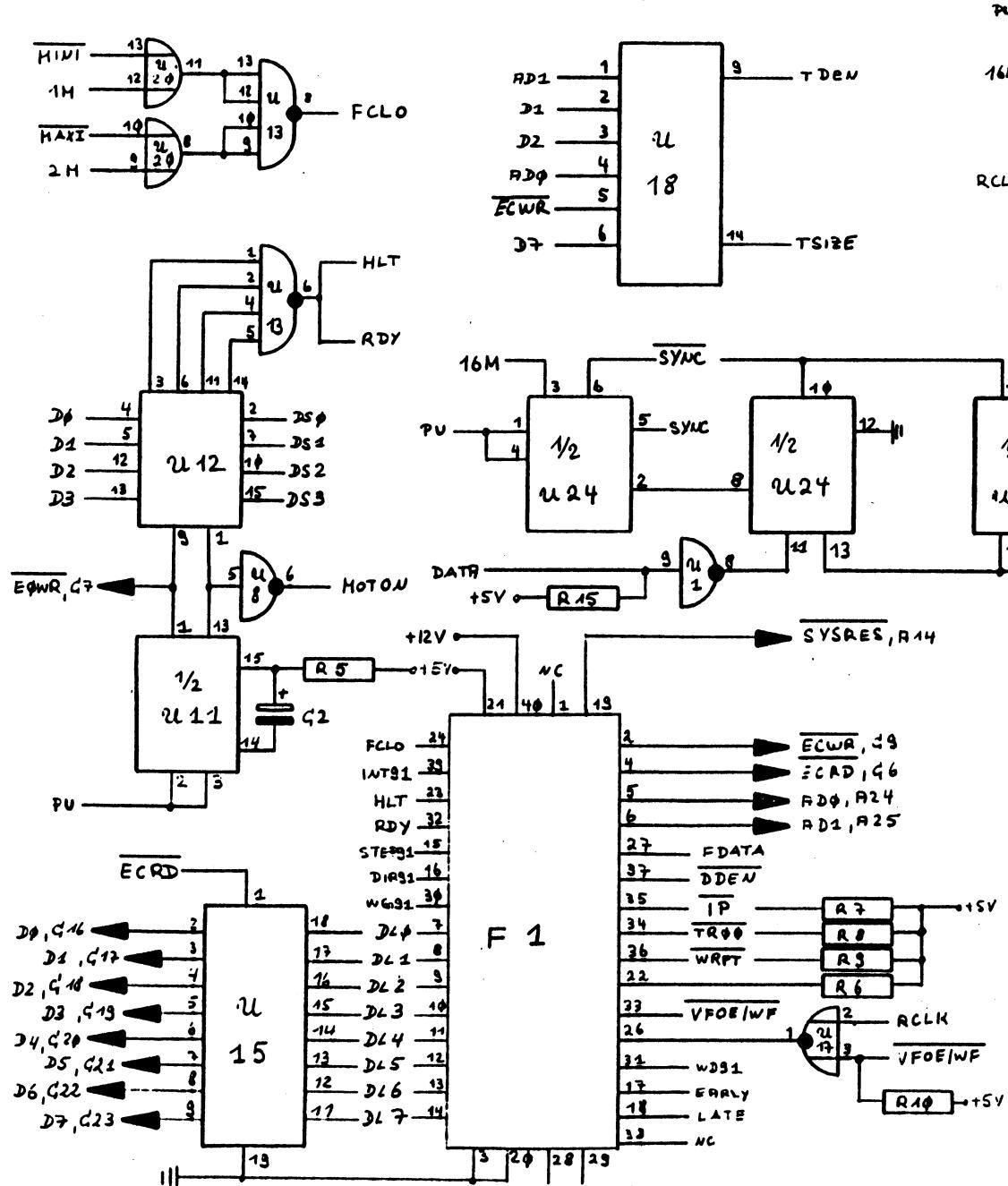

Aktive Bauteile: SpeedMaster 5.3, FLOPPY 5/8 A Wertordnung

=====

| TTL Baustein: | Anzahl: | Bauteilname:         |

|---------------|---------|----------------------|

| 74 LS 02      | 1       | U 17                 |

| 74 S 04       | 1       | U 1                  |

| 74 16         | 2       | U 8, U 14            |

| 74 LS 20      | 2       | U 13, U 19           |

| 74 LS 32      | 1       | U 20                 |

| 74 LS 38      | 2       | U 9 - 10             |

| 74 LS 74      | 4       | U 6, U 21, U 24 - 25 |

| 74 LS 90      | 1       | U 5                  |

| 74 LS 93      | 1       | U 2                  |

| 74 LS 123     | 1       | U 11                 |

| 74 LS 125     | 1       | U 7                  |

| 74 LS 138     | 1       | U 18                 |

| 74 LS 161     | 2       | U 22 - 23            |

| 74 LS 166     | 1       | U 16                 |

| 74 LS 175     | 1       | U 12                 |

| 74 LS 390     | 2       | U 3 - 4              |

| 74 LS 640     | 1       | U 15                 |

| Sonder IC's  | Anzahl: | Bauteilname: |

|--------------|---------|--------------|

| SAB 1791 - 2 | 1       | F 1          |

Aktive Bauteile: SpeedMaster 5.3, FLOPPY 5/8 A Rangordnung

=====

| Bauteilname: | Bezeichnung:           |

|--------------|------------------------|

| -----        | -----                  |

| U 1          | TTL, 74 S 04           |

| U 2          | TTL, 74 LS 93          |

| U 3 - 4      | TTL, 74 LS 390         |

| U 5          | TTL, 74 LS 90          |

| U 6          | TTL, 74 LS 74          |

| U 7          | TTL, 74 LS 125         |

| U 8          | TTL, 74 16, auch 74 06 |

| U 9 - 10     | TTL, 74 LS 38          |

| U 11         | TTL, 74 LS 123         |

| U 12         | TTL, 74 LS 175         |

| U 13         | TTL, 74 LS 20          |

| U 14         | TTL, 74 16, auch 74 06 |

| U 15         | TTL, 74 LS 640         |

| U 16         | TTL, 74 LS 166         |

| U 17         | TTL, 74 LS 02          |

| U 18         | TTL, 74 LS 138         |

| U 19         | TTL, 74 LS 20          |

| U 20         | TTL, 74 LS 32          |

| U 21         | TTL, 74 LS 74          |

| U 22 - 23    | TTL, 74 LS 161         |

| U 24 - 25    | TTL, 74 LS 74          |

| Bauteilname: | Bezeichnung: |

|--------------|--------------|

| -----        | -----        |

| F 1          | SAB 1791 - 2 |

Pinbelegung der Steckverbinder: SpeedMaster 5.3 FLOPPY 5/8 A

=====

Stecker: S 1

Dieser Steckverbinder dient zum Anschluß von bis zu drei 5 1/4" Floppy-Disk Laufwerken. (Siehe dazu auch S 3, Seite 25)

Die Pinbelegung ist Shugart kompatibel.

|       |       |       |

|-------|-------|-------|

| 2     | 6     | 34    |

| ..... | ..... | ..... |

| +     | ..... | ..... |

| 1     | 5     | 33    |

Die Position des Steckers entnehmen Sie bitte dem Lageplan.

| Pin: | Belegung: | Pin: | Belegung:               |

|------|-----------|------|-------------------------|

| 1    | Masse     | 2    | nicht belegt            |

| 3    | Masse     | 4    | nicht belegt            |

| 5    | Masse     | 6    | nicht belegt            |

| 7    | Masse     | 8    | Index Pulse             |

| 9    | Masse     | 10   | Drive Select 0 (5 1/4") |

| 11   | Masse     | 12   | Drive Select 1 (5 1/4") |

| 13   | Masse     | 14   | Drive Select 2 (5 1/4") |

| 15   | Masse     | 16   | Motor On                |

| 17   | Masse     | 18   | Direction               |

| 19   | Masse     | 20   | Step                    |

| 21   | Masse     | 22   | Write Data              |

| 23   | Masse     | 24   | Write Gate              |

| 25   | Masse     | 26   | Track 00                |

| 27   | Masse     | 28   | Write Protect           |

| 29   | Masse     | 30   | Read Data               |

| 31   | Masse     | 32   | Side Select (5", 8")    |

| 33   | Masse     | 34   | nicht belegt            |

Erklärungen zu den einzelnen Signalen entnehmen Sie bitte dem technischen Manual Ihrer Diskettenlaufwerke.

Sie können jedes 5 1/4" Laufwerk von Single-Sided, Single-Density bis Double-Sided, Double-Density anschließen.

## Stecker: S 3

## FLOPPY 5/8 A

Dieser Steckverbinder dient in Verbindung mit Kodiersteckern zum Einstellen von POWER ON bzw. RESET Parametern.

4 3

..

+.

1 2

Die Position des Steckers entnehmen Sie bitte dem Lageplan.

| Pin: | Belegung:     | Pin: | Belegung:     |

|------|---------------|------|---------------|

| 1    | System Reset  | 4    | System Reset  |

| 2    | Set 5" Drives | 3    | Set 8" Drives |

In der Grundeinstellung werden die Pin's 1 und 2 über einen Kodierstecker kurzgeschlossen. Damit stellt sich das System beim Einschalten oder bei einem RESET wie folgt ein:

1. Der Floppy Kontroller wird auf Single-Density Format gesetzt

2. Der Stecker S 1 für 5 1/4" Laufwerke wird aktiv

## Änderungen:

Soll das System mit 8" Laufwerken über Stecker S 2 booten, Pin 1 und 2 öffnen und Pin 3 und 4 kurzschließen.

Die Schreibdichte beim Booten ist immer Single-Density.

## Warnung:

Alle anderen Einstellungen führen zu nicht vorhersehbaren Fehlfunktionen des Systems.

## Stecker: S 2

## FLOPPY 5/8 A

Dieser Steckverbinder dient zum Anschluß von bis zu drei 8" Floppy-Disk Laufwerken. (Siehe dazu auch S 3, Seite 25)

Die Pinbelegung ist Shugart kompatibel.

|        |       |

|--------|-------|

| 2 6    | 50    |

| .....  | ..... |

| +..... | ..... |

| 1 5    | 49    |

Die Position des Steckers entnehmen Sie bitte dem Lageplan.

| Pin: | Belegung: | Pin: | Belegung:            |

|------|-----------|------|----------------------|

| 1    | Masse     | 2    | nicht belegt         |

| 3    | Masse     | 4    | nicht belegt         |

| 5    | Masse     | 6    | nicht belegt         |

| 7    | Masse     | 8    | nicht belegt         |

| 9    | Masse     | 10   | nicht belegt         |

| 11   | Masse     | 12   | nicht belegt         |

| 13   | Masse     | 14   | Side Select (5", 8") |

| 15   | Masse     | 16   | nicht belegt         |

| 17   | Masse     | 18   | Motor On, Head Load  |

| 19   | Masse     | 20   | Index Pulse          |

| 21   | Masse     | 22   | nicht belegt         |

| 23   | Masse     | 24   | nicht belegt         |

| 25   | Masse     | 26   | Drive Select 0 (8")  |

| 27   | Masse     | 28   | Drive Select 1 (8")  |

| 29   | Masse     | 30   | Drive Select 2 (8")  |

| 31   | Masse     | 32   | nicht belegt         |

| 33   | Masse     | 34   | Direction            |

| 35   | Masse     | 36   | Step                 |

| 37   | Masse     | 38   | Write Data           |

| 39   | Masse     | 40   | Write Gate           |

| 41   | Masse     | 42   | Track 00             |

| 43   | Masse     | 44   | Write Protect        |

| 45   | Masse     | 46   | Read Data            |

| 47   | Masse     | 48   | nicht belegt         |

| 49   | Masse     | 50   | nicht belegt         |

Erklärungen zu den einzelnen Signalen entnehmen Sie bitte dem technischen Manual Ihrer Diskettenlaufwerke.

Sie können jedes 8" Laufwerk mit Single-Sided, Single-Density oder Double-Sided, Single-Density anschließen.

## Stecker: S 1

## FLOPPY DS/DD

Dieser Steckverbinder dient zum Anschluß von bis zu vier 5 1/4" Floppy-Disk Laufwerken. (Siehe dazu auch S 3, Seite 28)

Die Pinbelegung ist Shugart kompatibel.

|       |       |    |

|-------|-------|----|

| 2     | 6     | 34 |

| ..... | ..... |    |

| +     | ..... |    |

| 1     | 5     | 33 |

Die Position des Steckers entnehmen Sie bitte dem Lageplan.

| Pin: | Belegung: | Pin: | Belegung:               |

|------|-----------|------|-------------------------|

| 1    | Masse     | 2    | nicht belegt            |

| 3    | Masse     | 4    | nicht belegt            |

| 5    | Masse     | 6    | Drive Select 3 (5 1/4") |

| 7    | Masse     | 8    | Index Pulse             |

| 9    | Masse     | 10   | Drive Select 0 (5 1/4") |

| 11   | Masse     | 12   | Drive Select 1 (5 1/4") |

| 13   | Masse     | 14   | Drive Select 2 (5 1/4") |

| 15   | Masse     | 16   | Motor On                |

| 17   | Masse     | 18   | Direction               |

| 19   | Masse     | 20   | Step                    |

| 21   | Masse     | 22   | Write Data              |

| 23   | Masse     | 24   | Write Gate              |

| 25   | Masse     | 26   | Track 00                |

| 27   | Masse     | 28   | Write Protect           |

| 29   | Masse     | 30   | Read Data               |

| 31   | Masse     | 32   | Side Select (5", 8")    |

| 33   | Masse     | 34   | nicht belegt            |

Erklärungen zu den einzelnen Signalen entnehmen Sie bitte dem technischen Manual Ihrer Diskettenlaufwerke.

Sie können jedes 5 1/4" Laufwerk von Single-Sided, Single-Density bis Double-Sided, Double-Density anschließen.

Stecker: S 2

FLOPPY DS/DD

Dieser Steckverbinder dient zum Anschluß von bis zu vier 8" Floppy-Disk Laufwerken. (Siehe dazu auch S 3, Seite 28)

Die Pinbelegung ist Shugart kompatibel.

|        |       |

|--------|-------|

| 2 6    | 50    |

| .....  | ..... |

| +..... | ..... |

| 1 5    | 49    |

Die Position des Steckers entnehmen Sie bitte dem Lageplan.

| Pin: | Belegung: | Pin: | Belegung:            |

|------|-----------|------|----------------------|

| 1    | Masse     | 2    | nicht belegt         |

| 3    | Masse     | 4    | nicht belegt         |

| 5    | Masse     | 6    | nicht belegt         |

| 7    | Masse     | 8    | nicht belegt         |

| 9    | Masse     | 10   | nicht belegt         |

| 11   | Masse     | 12   | nicht belegt         |

| 13   | Masse     | 14   | Side Select (5", 8") |

| 15   | Masse     | 16   | nicht belegt         |

| 17   | Masse     | 18   | Motor On, Head Load  |

| 19   | Masse     | 20   | Index Pulse          |

| 21   | Masse     | 22   | nicht belegt         |

| 23   | Masse     | 24   | nicht belegt         |

| 25   | Masse     | 26   | Drive Select 0 (8")  |

| 27   | Masse     | 28   | Drive Select 1 (8")  |

| 29   | Masse     | 30   | Drive Select 2 (8")  |

| 31   | Masse     | 32   | Drive Select 3 (8")  |

| 33   | Masse     | 34   | Direction            |

| 35   | Masse     | 36   | Step                 |

| 37   | Masse     | 38   | Write Data           |

| 39   | Masse     | 40   | Write Gate           |

| 41   | Masse     | 42   | Track 00             |

| 43   | Masse     | 44   | Write Protect        |

| 45   | Masse     | 46   | Read Data            |

| 47   | Masse     | 48   | nicht belegt         |

| 49   | Masse     | 50   | nicht belegt         |

Erklärungen zu den einzelnen Signalem entnehmen Sie bitte dem technischen Manual Ihrer Diskettenlaufwerke.

Sie können jedes 8" Laufwerk von Single-Sided, Single-Density bis Double-Sided, Double-Density anschließen.

## Stecker: S 3

## FLOPPY DS/DD

Dieser Steckverbinder dient in Verbindung mit Kodiersteckern zum Einstellen von POWER ON bzw. RESET Parametern.

12      7

.....

+.....

1      6

Die Position des Steckers entnehmen Sie bitte dem Lageplan.

| Pin: | Belegung:       | Pin: | Belegung:    |

|------|-----------------|------|--------------|

| 1    | Set Single Den. | 12   | System Reset |

| 2    | Set Double Den. | 11   | System Reset |

| 3    | Set 8" Drives   | 10   | System Reset |

| 4    | Set 5" Drives   | 9    | System Reset |

| 5    | Drive Sel. 3    | 8    | Side Select  |

| 6    | Drive Sel. 4    | 7    | Side Select  |

In der Grundeinstellung werden die Pin's 1 und 12, 4 und 9 sowie 6 und 7 über Kodierstecker kurzgeschlossen.

Damit stellt sich das System beim Einschalten oder bei einem RESET wie folgt ein:

1. Der Floppy-Kontroller wird auf Single-Density Format gesetzt

2. Der Stecker S 1 für 5 1/4" Laufwerke wird aktiv

3. Für den Side-Select wird BIT 4 des Select-Ports aktiv

## Änderungen:

Soll das System in Double-Density booten, Pin 1 und 12 öffnen und Pin 2 und 11 kurzschließen.

Soll das System mit 8" Laufwerken über Stecker S 2 booten, Pin 4 und 9 öffnen und Pin 3 und 10 kurzschließen.

Soll für den Side-Select BIT 3 des Select-Ports aktiv werden, Pin 6 und 7 öffnen und Pin 5 und 8 kurzschließen.

## Warnung:

Alle anderen Einstellungen, außer eine Kombination der oben genannten, führen zu nicht vorhersehbaren Fehlfunktionen des Systems.

## Stecker: S 4

Dieser Steckverbinder ist für Einstellarbeiten am Floppy-Kontroller erforderlich und darf nicht kurzgeschlossen werden.

## Stecker: S 1

I/O 1.1

Dieser Steckverbinder dient im wesentlichen zum Anschluß eines Kassettenrekorders. Dazu verbinden Sie Pin 4 mit dem Kopfhörerausgang und Pin 5 mit dem Mikrofoneingang des Rekorders, wobei Pin 2 die gemeinsame Masse darstellt. Die Pin's 1 und 3 können von dem eingebauten Reed-Relais kurzgeschlossen werden und dienen somit zur Motor An/Aus Steuerung. Die Pin's 6 und 7 können mit TTL-Eingangspegeln belegt und vom System gelesen werden.

8 5

....

+...

1 4

Die Position des Steckers entnehmen Sie bitte dem Lageplan.

## Pin: Belegung:

---

|   |        |

|---|--------|

| 1 | MOTOR0 |

| 2 | Masse  |

| 3 | MOTOR1 |

| 4 | CASIN  |

## Pin: Belegung:

---

|   |          |

|---|----------|

| 8 | + 5 Volt |

| 7 | User0    |

| 6 | User1    |

| 5 | CASOUT   |

## Stecker: S 2

Dieser Steckverbinder dient zum Anschluß des Keyboards.

20 11

.....

+.....

1 10

Die Position des Steckers entnehmen Sie bitte dem Lageplan.

## Pin: Belegung:

---

|    |                  |

|----|------------------|

| 1  | Y0-Eingang       |

| 2  | Y1-Eingang       |

| 3  | Y2-Eingang       |

| 4  | Y3-Eingang       |

| 5  | Y4-Eingang       |

| 6  | Y5-Eingang       |

| 7  | Y6-Eingang       |

| 8  | Y7-Eingang       |

| 9  | RESET, aktiv low |

| 10 | Masse            |

## Pin: Belegung:

---

|    |                   |

|----|-------------------|

| 20 | + 5 Volt          |

| 19 | SPEED, aktiv High |

| 18 | X0-Ausgang        |

| 17 | X1-Ausgang        |

| 16 | X2-Ausgang        |

| 15 | X3-Ausgang        |

| 14 | X4-Ausgang        |

| 13 | X5-Ausgang        |

| 12 | X6-Ausgang        |

| 11 | X7-Ausgang        |

Über die Pin's 11 bis 18 werden LOW-Pegel vom System zum Keyboard übertragen, die je nach gedrückter Taste an den Pin's 1 bis 8 einen LOW-Pegel erzeugen. Wird der Pin 19 auf LOW-Pegel gesetzt, geht die CPU Taktfrequenz von 5.3 MHz auf 1.77 MHz zurück. Geht Pin 9 auf LOW-Pegel, führt das System einen RESET durch.

## Stecker: S 3

I/O 1.1

Dieser Steckverbinder dient zum Anschluß eines Druckers mit Centronics Parallel Schnittstelle.

20            11

.....

+.....

1            10

Die Position des Steckers entnehmen Sie bitte dem Lageplan.

| Pin: | Belegung:  | Pin: | Belegung:         |

|------|------------|------|-------------------|

| 1    | DO-Ausgang | 20   | + 5 Volt          |

| 2    | D1-Ausgang | 19   | + 5 Volt          |

| 3    | D2-Ausgang | 18   | nicht belegt      |

| 4    | D3-Ausgang | 17   | nicht belegt      |

| 5    | D4-Ausgang | 16   | nicht belegt      |

| 6    | D5-Ausgang | 15   | STROBE, aktiv low |

| 7    | D6-Ausgang | 14   | BUSY              |

| 8    | D7-Ausgang | 13   | PAPER EMPTY       |

| 9    | Masse      | 12   | UNIT SELECT       |

| 10   | Masse      | 11   | UNIT FAULT        |

Über die Pin's 1 bis 8 werden dem Drucker die Daten übertragen und mit Pin 15 übergeben. Über die Pin's 11 bis 14 teilt der Drucker dem System seinen Status mit.

## Achtung:

Die Pin's 19 und 20 nicht mit der + 5 Volt-Leitung des Druckers verbinden. Kurzschlußgefahr.

## Stecker: S 4

Dieser Steckverbinder dient zum Anschluß eines Lautsprechers.

2

.

+

1

Die Position des Steckers entnehmen Sie bitte dem Lageplan.

| Pin: | Belegung: | Pin: | Belegung: |

|------|-----------|------|-----------|

| 1    | NF-Out    | 2    | + 5 Volt  |

## Belegung der I/O Ports: SpeedMaster 5.3

=====

Innerhalb des Systems werden 2, in Verbindung mit FLOPPY DS/DD 3, vollständig dekodierte Z-80 I/O Ports benötigt. Eine genaue Bestimmung der Adressen und eine Beschreibung der Funktionen entnehmen Sie bitte den folgenden Seiten.

| L.Nr. | Adre.: | Hex, Dez | Kurzbeschreibung:                |

|-------|--------|----------|----------------------------------|

| 1     | FE     | , 254    | System-Byte 0                    |

| 2     | FF     | , 255    | Bildschirmformat, Kassette, User |

| 3     | F9     | , 249    | Interruptsteuerung, FLOPPY DS/DD |

## Die Beschreibung der Ports im Einzelnen:

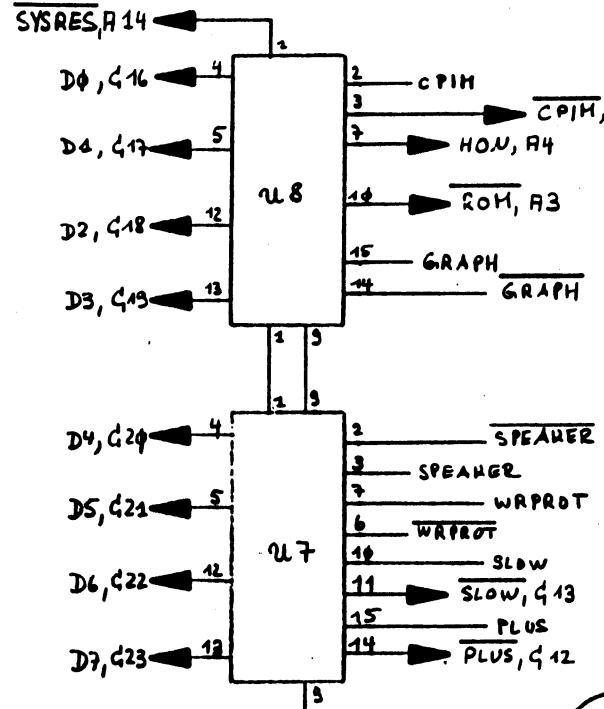

1. Über den Port FE, 254 (System-Byte 0) können Sie System-Parameter ändern. Da fast jede Änderung interne Systemabläufe beeinflußt, ist das System-Byte 0 nur mit äußerster Vorsicht zu behandeln.

Das System-Byte 0 kann gelesen und geschrieben werden. Die einzelnen BIT's haben dabei folgende Bedeutung:

## a. BIT 0 =&gt; I/O Freigabe BIT

Mit diesem BIT können Sie die Memory-Mapped I/O Baugruppen (siehe Seite 39) ein bzw. ausschalten.

BIT 0 = Low => Aus dem Hauptspeicher werden, abhängig von System-Byte 0, BIT 3 die angegebenen Speicherbereiche ausgeblendet und für Memory-Mapped I/O freigegeben:

3400 - 37DF, 13312 - 14303 => gesperrt

37E0 - 37FF, 14304 - 14335 => Disk I/O

3800 - 3BFF, 14336 - 15359 => Keyboard

3C00 - 3FFF, 15360 - 16383 => Video

BIT 0 = High => Die Memory-Mapped I/O Baugruppen und der Festwertspeicher (EPROM) sind gesperrt. Der Hauptspeicher ist, abhängig von System-Byte 0, BIT 3 und 7 durchgehend freigegeben.

## b. BIT 1 =&gt; Grafik An/Aus BIT

Mit diesem BIT können Sie die Grafikseite auf dem Monitor zur Anzeige bringen.

BIT 1 = Low => Es erfolgt keine Anzeige der Grafikseite.

BIT 1 = High => Die Grafikseite wird über den BIT Image-Mischer mit der normalen Videoinformation ODER verknüpft und zur Anzeige gebracht.

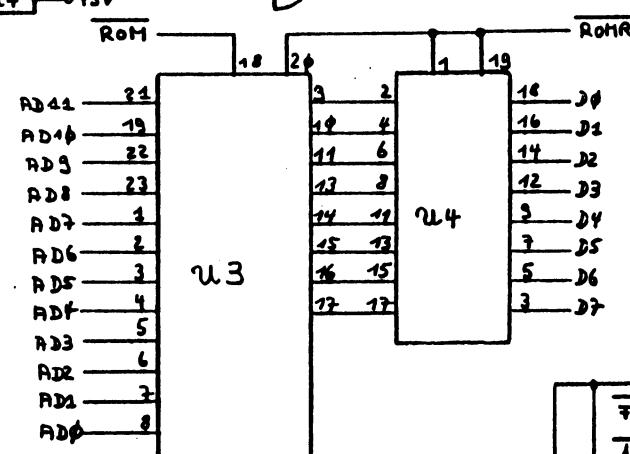

## c. BIT 2 =&gt; ROM BIT

Über dieses Bit erreichen Sie den Festwertspeicher (EPROM) des Systems.

BIT 2 = Low => Die Taktfrequenz des Systems wird auf 1.77 MHz herabgesetzt. Ist System-Byte 0, BIT 0 auf High, erfolgt keine weitere Änderung. Sonst wird der Festwertspeicher des Systems im Adressbereich 0000 - 2FFF, 0000 - 12287 freigegeben.

BIT 2 = High => Der Festwertspeicher ist gesperrt.

## d. BIT 3 =&gt; Grafik Schalt BIT

Mit diesem BIT können Sie die Grafikseite für Schreib- oder Lese-Zyklen freigeben.

BIT 3 = Low => Die Grafikseite ist gesperrt.

BIT 3 = High => Abhängig von System-Byte 0, BIT 7 wird im Bereich 0000 - 3FFF, 0000 - 16383 die Grafikseite freigegeben. Dabei werden automatisch die Memory-Mapped I/O Baugruppen, der Festwertspeicher und der Bereich 4000 - BFFF, 16384 - 49151 gesperrt.

## Beispiel:

Das System ist im 64 Zeichen / 16 Zeilen Modus wobei pro Zeile 12 Scann-Zeilen angezeigt werden (Power-On Wert). Dann errechnen sich die Grenzen der Grafikseiten wie folgt:

X-Grenzen:  $0 \leq X \leq 64 * 6 + 16 * 6 = 384 + 96 = 480$

Y-Grenzen:  $0 \leq Y \leq 16 * 12 = 192$

Das folgende Programm beschreibt ein Verfahren, um in diesem Modus einen beliebigen Punkt X, Y innerhalb der oben genannten Grenzen in Abhängigkeit eines Parameters zu setzen, löschen oder abzufragen. Das Beispiel soll lediglich die Möglichkeiten des Systems darstellen und erhebt keinen Anspruch auf optimale Auslegung. Zuerst jedoch eine Erklärung zu der Adressierung der Grafikseite.

Die Seite teilt sich in einen INNEREN (384 x 192) und einen AUSSEREN (96 x 192) Bereich auf, wobei pro Adressbyte je 6 BIT's sequenziell auf dem Monitor ausgelesen werden. Dabei gilt für die Adressierung:

## Innen: Bit's im Adressbyte:

|    |    |    |       |    |    |       |    |    |           |    |    |    |    |    |    |

|----|----|----|-------|----|----|-------|----|----|-----------|----|----|----|----|----|----|

| 15 | 14 | 13 | 12    | 11 | 10 | 09    | 08 | 07 | 06        | 05 | 04 | 03 | 02 | 01 | 00 |

| 0  | 0  | :  | Reihe | :  | :  | Zeile | :  | :  | PositionI | :  |    |    |    |    |    |

## Außen: Bit's im Adressbyte:

|    |    |    |    |    |     |    |       |    |     |    |           |    |    |    |    |

|----|----|----|----|----|-----|----|-------|----|-----|----|-----------|----|----|----|----|

| 15 | 14 | 13 | 12 | 11 | 10  | 09 | 08    | 07 | 06  | 05 | 04        | 03 | 02 | 01 | 00 |

| 0  | 0  | 1  | 1  | :  | LSB | :  | Zeile | :  | MSB | :  | PositionA | :  |    |    |    |

wobei:  $0 \leq \text{Reihe} \leq 11$ ,  $0 \leq \text{Zeile} \leq 15$ ,  $0 \leq \text{PositionI} \leq 63$

$: 0 \leq \text{PositionA} \leq 15$ ,  $\text{Reihe} = 4 * \text{MSB} + \text{LSB}$

```

*****

; Programm zur Generierung des X-Adressoffsets und der X-Bit-

; positionen (TABELB) und einer Y-Tabelle (TABELA).

; Das Programm wird bei INIT gestartet und führt einen Sprung

; ins DOS mit JP 402DH aus.

; Das HIMEM muß auf TABELB gesetzt sein.

*****

```

|        |      |           |                                     |

|--------|------|-----------|-------------------------------------|

|        | ORG  | START     | ; Die Startadresse muß > COOH sein  |

| INIT   | LD   | HL,TABELB | ; Startadresse für X-Positionen     |

|        | XOR  | A         | ; Lösche A-Register, Offset         |

| INIT01 | LD   | C,01H     | ; Setze BIT 0, ergibt Bitposition   |

|        | LD   | B,06H     | ; 6 Bit Zähler                      |

| INIT02 | LD   | (HL),A    | ; Offset als Adresse                |

|        | INC  | HL        | ; Nächste Tabellenposition          |

|        | LD   | (HL),C    | ; Speichere Bitposition             |

|        | INC  | HL        | ; Nächste Tabellenposition          |

|        | RLC  | C         | ; Erhöhe die Bitposition            |

|        | DJNZ | INIT02    | ; Durchlufe Schleife 6 mal          |

|        | INC  | A         | ; Erhöhe Offset                     |

|        | CP   | 50H       | ; Zeilenende erreicht ?             |

|        | JR   | NZ,INIT01 | ; Nein, berechne neuen Offset       |

|        | LD   | HL,TABELA | ; Startadresse für Y-Positionen     |

|        | LD   | B,00H     | ; B ist Zeilenzähler                |

| INIT03 | LD   | C,00H     | ; C ist Scann-Zeilenzähler          |

| INIT04 | LD   | A,C       | ; Lade aktuelle Scann-Zeile nach A  |

|        | SLA  | A         | ; Verschiebe den Scann-Zeilenzähler |

|        | SLA  | A         | ; um insgesamt 4 Bit nach links.    |

|        | SLA  | A         | ; Die Bit's 0 - 3 werden für die    |

|        | SLA  | A         | ; Zeilennummer gebraucht.           |

|        | ADD  | A,B       | ; Ersten 4 Bit ergeben Zeilennummer |

|        | LD   | (HL),A    | ; Speichere den Wert in Tabelle     |

|        | INC  | HL        | ; Nächste Tabellenposition          |

|        | INC  | C         | ; Nächste Scann-Zeile               |

|        | LD   | A,C       | ; Aktuelle Scann-Zeile nach A       |

|        | CP   | 0CH       | ; Alle 12 Scann-Zeilen fertig ?     |

|        | JR   | NZ,INIT04 | ; Nein, berechne weitere Werte      |

|        | INC  | B         | ; Erhöhe Zeilenzähler               |

|        | LD   | A,B       | ; Aktuelle Zeile nach A             |

|        | CP   | 10H       | ; Alle 16 Zeilen fertig ?           |

|        | JR   | NZ,INIT03 | ; Nein, berechne weitere Werte      |

|        | JP   | 402DH     | ; Fertig, zurück zum DOS =>         |

| TABELB | DEFS | 01EOH     | ; Platz für Bitpositionen           |

|        | DEFS | 01EOH     | ; Platz für X-Adressoffset          |

| TABELA | DEFS | 00COH     | ; Platz für Y-Tabelle               |

```

*****

; Der folgende Programmteil setzt voraus, daß das Programm-

; segment INIT einmal durchlaufen wurde, wobei die Tabellen ab

; Speicher TABELB erstellt wird.

; Eingangsparameter: (XKOOR) ist X-Position

; (YKOOR) ist Y-Position

; A-Register 2=SET, 1=RESET, 0=POINT

; Ausgangsparameter: keine, wenn A-Register 1 oder 2 war

; sonst: Punkt aus => HL=0, Punkt an => HL=1

*****

```

|       |      |            |                                   |

|-------|------|------------|-----------------------------------|

| PLOT  | DI   |            | ;Wichtig, Zero-Page ist gesperrt  |

|       | CP   | 0          | ;POINT-Funktion ?                 |

|       | JR   | Z,POINT    | ;Ja, ausführen =>                 |

|       | CP   | 1          | ;RESET-Funktion ?                 |

|       | JR   | Z,RESET    | ;Ja, ausführen =>                 |

| SET   | LD   | HL,(XKOOR) | ;Hole X-Position nach HL          |

|       | CALL | ADCAL      | ;Berechne relative Speicherpos.   |

|       | IN   | A,(OFEH)   | ;Inhalt vom System-Byte 0 lesen   |

|       | OR   | 08H        | ;Grafik Schalt BIT setzen         |

|       | OUT  | (OFEH),A   | ;Grafikseite freigeben            |

|       | LD   | A,(HL)     | ;Grafik Image holen               |

|       | OR   | B          | ;BIT setzen                       |

| OUTPL | LD   | (HL),A     | ;Grafik Image zurückschreiben     |

| EXIT  | IN   | A,(OFEH)   | ;Inhalt vom System-Byte 0 lesen   |

|       | AND  | 0F7H       | ;Grafik Schalt BIT löschen        |

|       | OUT  | (OFEH),a   | ;Grafikseite sperren              |

|       | EI   |            | ;Interrupts freigeben             |

|       | RET  |            | ;Zurück zum Hauptprogramm         |

| RESET | LD   | HL,(XKOOR) | ;Hole X-Position nach HL          |

|       | CALL | ADCAL      | ;Berechne relative Speicherpos.   |

|       | IN   | A,(OFEH)   | ;Inhalt vom System-Byte 0 lesen   |

|       | OR   | 08H        | ;Grafik Schalt BIT setzen         |

|       | OUT  | (OFEH),A   | ;Grafikseite freigeben            |

|       | LD   | A,B        | ;Bitposition nach A               |

|       | XOR  | OFFH       | ;und komplementieren              |

|       | LD   | B,A        | ;und zurück nach B                |

|       | LD   | A,(HL)     | ;Grafik Image holen               |

|       | AND  | B          | ;BIT löschen                      |

|       | JR   | OUTPL      | ;Zurückschreiben und UP verlassen |

| POINT | LD   | HL,(XKOOR) | ;Hole X-Position nach HL          |

|       | CALL | ADCAL      | ;Berechne relative Speicherpos.   |

|       | IN   | A,(OFEH)   | ;Inhalt vom System-Byte 0 lesen   |

|       | OR   | 08H        | ;Grafik Schalt BIT setzen         |

|       | OUT  | (OFEH),A   | ;Grafikseite freigeben            |

|       | LD   | A,(HL)     | ;Grafik Image holen               |

|       | AND  | B          | ;Testen ob BIT an oder aus        |

|       | LD   | HL,0000    | ;HL mit 0000 => BIT aus           |

|       | JR   | Z,EXIT     | ;BIT aus, UP verlassen            |

|       | INC  | HL         | ;BIT an, HL = 1                   |

|       | JR   | EXIT       | ;UP verlassen                     |

;

;

; Das Unterprogramm ADCAL berechnet aus der X-Position im HL-Registerpaar und der Y-Position in Speicherstelle YK00R die, nach dem auf Seite 32 dargestellten Verfahren, relative Adresse des Grafikspeichers.

;

; Im HL-Register wird die Adresse, im B-Register die Bitposition innerhalb der Adresse an den CALLER übergeben.

;

;

|       |      |           |                              |

|-------|------|-----------|------------------------------|

| ADCAL | LD   | BC,TABELB | ;BC zeigt auf Tabellenanfang |

|       | ADD  | HL,HL     | ;X-Position mal 2            |

|       | ADD  | HL,BC     | ;HL zeigt auf X-Offset       |

|       | LD   | A,(HL)    | ;Hole X-Offset nach A        |

|       | CP   | 40H       | ;Innen oder Außen ?          |

|       | JP   | P,AUSSEN  | ;Außen, ( INT(X/6) > 63 )    |

| INNEN | CALL | VERT      | ;Berechne Vertikales Segment |

|        |      |            |                                   |

|--------|------|------------|-----------------------------------|

|        | SRL  | H          | ;Bitkombinationen in H und L      |

|        | RR   | L          | ;müssen um jeweils 2 Stellen      |

|        | SRL  | H          | ;nach rechts geschoben werden, um |

|        | RR   | L          | ;die echte Adresse zu erhalten.   |

|        | RET  |            | ;Zurück zum Hauptprogramm         |

| VERT   | INC  | HL         | ;HL zeigt auf Bitposition         |

|        | LD   | B, (HL)    | ;Bitposition nach B               |

|        | LD   | HL, TABELA | ;HL zeigt auf Y-Tabelle           |

|        | DEFB | 0011H      | ;Mit YKOOR => LD DE, YKOOR        |

| YKOOR  | DEFW | 0000H      | ;Speicherstelle YKOOR             |

|        | ADD  | HL, DE     | ;HL zeigt auf Zeilenoffset        |

|        | LD   | H, (HL)    | ;Hole Zeilenoffset nach H         |

|        | LD   | L, A       | ;L = Zeichenposition              |

|        | SLA  | L          | ;Schiebe L um zwei Stellen        |

|        | SLA  | L          | ;nach links                       |

|        | RET  |            | ;Zurück zum Hauptprogramm         |

| AUSSEN | CALL | VERT       | ;Berechne Vertikales Segment      |

|        | SLA  | L          | ;Schiebe L um weitere 2 Stellen   |

|        | SLA  | L          | ;nach links                       |

|        | RLC  | H          | ;Verschiebe H um zwei Stellen     |

|        | RLC  | H          | ;nach links                       |

|        | PUSH | BC         | ;Rette Bitposition auf dem STACK  |

|        | LD   | B, 04H     | ;Für 4 Verschiebeoperationen      |

| AUSEN1 | SRL  | H          | ;Verschiebe H nach rechts         |

|        | RR   | L          | ;Verschiebe L nach rechts         |

|        | DJNZ | AUSEN1     | ;Durchlufe Schleife 4 mal         |

|        | POP  | BC         | ;Hole Bitposition zurück          |

|        | LD   | A, H       | ;Hole MSB-Segment nach A          |

|        | ADD  | A, 30H     | ;Setze BIT 12 und 13              |

|        | LD   | H, A       | ;HL ist echte Adresse             |

|        | RET  |            | ;Zurück zum Hauptprogramm         |

| XKOOR  | DEFW | 0000H      | ;Speicherstelle für X-Koordinate  |

|        | END  | INIT       | ;Auto-Start nach INIT             |

Um mit diesem Programm zu arbeiten, müssen Sie den Source-Code in den Assembler eingeben und assemblieren. Danach setzen Sie das HIMEM auf TABELB und rufen den Object-Code von DOS aus auf und initialisieren damit die Tabellen.

Nun können Sie Ihre gewählten X-, Y-Positionen in die Speicherstellen XKOOR und YKOOR einschreiben, das A-Register mit 0, 1 oder 2 laden und einen CALL PLOT ausführen.

Achtung:

Da beim Freigeben der Grafikseite der Hauptspeicherbereich von 4000 - BFFF, 16384 - 49151 gesperrt wird, ist darauf zu achten, daß der STACK-Pointer in den Bereich von C000 - FFFF, 49152 - 65535 gelegt wird und das Programm selbst auch in diesem Bereich abgelegt ist.

Bitte bedenken Sie, daß Sie nur dann etwas von der Grafikseite auf dem Monitor sehen, wenn System-Byte 0, BIT 1 auf High ist.

## e. BIT 4 =&gt; Sound BIT

Über dieses BIT haben Sie die Möglichkeit, einen am Stecker S 4 angeschlossenen Lautsprecher abzuschalten.

BIT 4 = Low => Der Stecker S 4 ist freigegeben.

BIT 4 = High => Der Stecker S 4 ist gesperrt.

## f. BIT 5 =&gt; Schreibschutz BIT

Mit diesem BIT haben Sie die Möglichkeit einen bestimmten Bereich des Hauptspeichers als "Pseudo-ROM" zu deklarieren.

BIT 5 = Low => Der Systemspeicher ist schreib- und lesbar.

BIT 5 = High => Ist System-Byte 0, BIT 0 oder BIT 3 auf High hat BIT 5 keine Funktion. Sonst wird der Bereich 0000 - 2FFF, 0000 - 12287 als "Pseudo-ROM" geschaltet, d. h. eine Schreiboperation auf diesen Bereich wird nicht ausgeführt.

## g. BIT 6 =&gt; Slow-Down BIT

Über dieses BIT können Sie die Taktrate der CPU ändern.

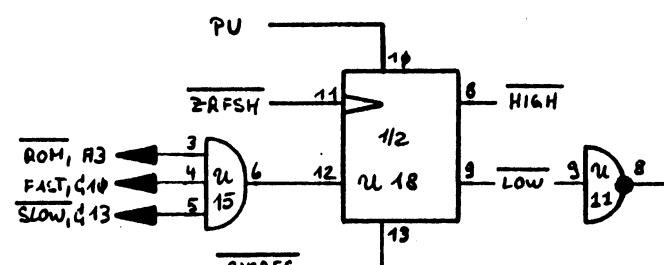

BIT 6 = Low => Ist der "Feuerknopf" gedrückt oder System-Byte 0, BIT 2 auf Low, ergibt sich eine Taktrate von 1.77 MHz, sonst arbeitet das System mit 5.35 MHz.

BIT 6 = High => Die Taktrate der CPU ist, unabhängig vom System-Byte 0, BIT 2 oder des "Feuerknopfes" immer 1.77 MHz.

## h. BIT 7 =&gt; Expansions BIT

In Verbindung mit entsprechender Hard-Ware kann mittels diesem BIT z. B. eine Speichererweiterung (RAM 2.0) realisiert werden.

BIT 7 = Low => Es gelten die unter Punkt a., d. und f. aufgeführten Hauptspeicherbelegungen.

BIT 7 = High => Der Hauptspeicherbereich 0000 - BFFF, 0000 - 49151 ist gesperrt. Zusatzbaugruppen können innerhalb dieses Adressbereiches alle Daten, die die CPU benötigt auf den BUS legen, wobei die ZBG darauf achten müssen, daß System-Byte 0, BIT 2 auf High liegt. Die Grafikseite ist gesperrt und der Schreibschutz muß von den ZBG über den BUS erkannt werden.

2. Über den Port FF, 255 können der Kassettenport, der Video-

kontroller und die USER-TTL-Eingänge kontrolliert werden.

Der Port kann gelesen und geschrieben werden, wobei gilt:

Lesen von FF, 255

a. BIT 0 = Low => Pin 7 von Stecker S1 hat TTL-Low Pegel

BIT 0 = High => Pin 7 von Stecker S1 hat TTL-High Pegel

b. BIT 1 = Low => Pin 6 von Stecker S1 hat TTL-Low Pegel

BIT 1 = High => Pin 6 von Stecker S1 hat TTL-High Pegel

c. BIT 6 = Low => Das Videoformat ist in 1:2 Darstellung

BIT 6 = High => Das Videoformat ist in 1:1 Darstellung

d. BIT 7 = Low => Der Kassettenport ist zurückgesetzt.

BIT 7 = High => Über Stecker S1, Pin 4 ist ein Impuls er-

kannt worden. (Muß softwareseitig zurück-

gesetzt werden. Siehe unten.)

Die BIT's 2 bis 5 haben einen zufälligen Wert.

Schreiben von FF, 255

a. BIT 1 : BIT 0 : Spannung an Pin 5 von Stecker S1

|   |   |   |   |          |

|---|---|---|---|----------|

| 0 | : | 0 | : | 0.4 Volt |

| 0 | : | 1 | : | 0.8 Volt |

| 1 | : | 0 | : | 0.0 Volt |

| 1 | : | 1 | : | 0.4 Volt |

b. BIT 2 = Low => Pin 1 und Pin 3 von Stecker S1 sind nicht

miteinander verbunden.

BIT 2 = High => Pin 1 und Pin 3 von Stecker S1 werden über

das Reed-Relais miteinander kurzgeschlossen.

c. BIT 3 = Low => Das Videoformat ist in der 1:1 Darstellung.

BIT 3 = High => Das Videoformat ist in der 1:2 Darstellung,

d. h.: die Zeichenbreite in X-Richtung wird

verdoppelt, wobei sich die Anzahl der

Zeichen/Zeile halbiert. Es werden auto-

matisch nur noch die Zeichen ausgelesen, die

in einer Speicherzelle mit gerader Adresse

stehen. Das gleiche gilt sinngemäß auch für

die Grafik.

Die BIT's 4 bis 7 können einen beliebigen Wert haben. Bei jedem

Schreibzyklus wird der Kassettenport zurückgesetzt.

Der Port F9, 249 ist nur in Verbindung mit der Karte FLOPPY DS/DD verfügbar. Der Port kann gelesen und geschrieben werden, wobei nur die BIT's 2 und 3 von Bedeutung sind.

3. Über den Port F9, 249 können die Interruptanforderungen der einzelnen Baugruppen umgeleitet bzw. unterbunden werden. Dabei gelten folgende Zustände:

a. BIT 3 : BIT 2 : Baugruppe, die den Interrupt anfordert

---

|   |   |   |   |                                            |

|---|---|---|---|--------------------------------------------|

| 0 | : | 0 | : | System Interrupt, alle 25 ms               |

| 0 | : | 1 | : | Floppy-Kontroller                          |

| 1 | : | 0 | : | Externe Baugruppen vom BUS                 |

| 1 | : | 1 | : | Z-80-B SIO/0, Z-80-B PIO (in Vorbereitung) |

Die Anforderung wirkt auf den Z-80-B INT Eingang und ist damit maskierbar (EI, DI).

Für alle Einstellungen muß Interrupt Mode 1 gewählt werden.

**Memory-Mapped I/O: SpeedMaster 5.3**

Innerhalb des Systems werden verschiedene Bereiche des Hauptspeichers, wie schon unter Abschnitt 1 a., Seite 31 und 1 h., Seite 36 erwähnt, für Memory-Mapped I/O herangezogen. Diese etwas aufwendige Art des I/O's ist für die Kompatibilität mit den Systemen TRS-80, GENIE I/II und GENIE III erforderlich, um die reichhaltige Software, sei es unter G-DOS, NEWDOS 80 oder CP/M, voll nutzen zu können. Die I/O Baugruppen werden im einzelnen beschreiben:

**1. Erweiterungsbereich: 3400 - 37DF, 13312 - 14303**

Dieser Bereich ist für Erweiterungen reserviert.

**2. Disk I/O Baugruppe**

Der Adressbereich von 37E0 - 37EF, 14304 - 14319 dient im wesentlichen zum Abwickeln des Diskettenbetriebs. Dabei ist der Bereich in 4 Blöcke zu je 4 Byte zusammengefaßt; die Adressen 37F0 - 37FF, 14320 - 14335 bilden ein Echo. Die angegebenen Stecker beziehen sich auf die Karten FLOPPY 5/8 A bzw. FLOPPY DS/DD. Die einzelnen Blöcke haben dabei folgende Bedeutung:

Schreiben von 37E0 - 37E3, 14304 - 14307 (FLOPPY 5/8 A)

- a. BIT 0 - 3 = Low => Die Motor-On-Leitung des Steckers S1 und S2 wird aktiv.

- b. BIT 0 = High => wie a., aber Drive Select für Drive 0 wird, je nach Stellung von S3 oder den eingestellten PDRIVE Parametern, an S1 oder S2 aktiv.

Sofern die Startwerte nicht verändert wurden, gilt:

S3 Pin 1 und 2 verbunden => S1 (5")

S3 Pin 3 und 4 verbunden => S2 (8")

- c. BIT 1 = High => wie b., aber Drive 1

- d. BIT 2 = High => wie b., aber Drive 2

- e. BIT 3 = High => wie a., aber die Side Select Leitung an S1 und S2 wird aktiv.

- f. BIT 4 - 7 = High => wie a.

**Achtung:**

Der Programmierer hat dafür Sorge zu tragen, daß jeweils nur EIN Laufwerk selektiert wird, da es sonst zu Datenverlust auf den Disketten kommen kann.

## Schreiben von 37E0 - 37E3, 14304 - 14307 (FLOPPY DS/DD)

-

- a. BIT 0 - 4 = Low => Die Motor-On-Leitung des Steckers S1 und S2 wird aktiv.

- b. BIT 0 = High => wie a., aber Drive Select für Drive 0 wird, je nach Stellung von S3 oder den eingestellten PDRIVE Parametern, an S1 oder S2 aktiv.

Sofern die Startwerte nicht verändert wurden, gilt:

S3 Pin 4 und 9 verbunden => S1 (5")

S3 Pin 3 und 10 verbunden => S2 (8")

- c. BIT 1 = High => wie b., aber Drive 1

- d. BIT 2 = High => wie b., aber Drive 2

- e. BIT 3 = High => wie b., aber Drive 3, wenn S3 Pin 6 und 7 verbunden. Wenn S3 Pin 5 und 8 verbunden sind, wird zusätzlich die Side Select Leitung an S1 und S2 aktiv.

- f. BIT 4 = High => wenn S3 Pin 6 und 7 verbunden sind wird die Side Select Leitung an S1 und S2 aktiv, wenn S3 Pin 5 und 8 verbunden sind wie a.

- g. BIT 5 - 7 = High => wie a.

## Achtung:

-----

Der Programmierer hat dafür Sorge zu tragen, daß, je nach Stellung von S3, nur EIN Laufwerk selektiert wird, da es sonst zu Datenverlust auf den Disketten kommen kann.

## Beispiel:

-----

```

SELD0V LD A,01H ;Select Drive 0, vordere Seite

LD (37EOH),A ;Kommando zum Kontroller

RET      ;Zurück zum Hauptprogramm

SELD0H LD A,09H ;Select Drive 0, hintere Seite für

LD (37EOH),A ;FLOPPY 5/8 A

RET      ;

SELD0H LD A,11H ;Select Drive 0, hintere Seite für

LD (37EOH),A ;FLOPPY DS/DD; S3 Pin 6 und 7 ver-

RET      ;bunden.

```

Lesen von 37E0 - 37E3, 14304 - 14307

-----

Durch Lesen von 37E0 - 37E3, 14304 - 14307 wird immer das Interrupt Flip-Flop zurückgesetzt (25 ms Interrupt). Durch Überprüfung der oberen 2 BIT erhalten Sie folgende Statusinformation:

- a. BIT 6 = Low => Floppy-Kontroller Interrupt gelöscht

BIT 6 = High => Floppy-Kontroller Interrupt gesetzt

- b. BIT 7 = Low => Interrupt Flip-Flop gelöscht

BIT 7 = High => Interrupt Flip-Flop gesetzt

Durch Ansprechen der Speicherstellen 37E4 - 37E7, 14308 - 14311 werden Freigabeleitungen an den BUS-Erweiterungssteckern VG4 - VG13 aktiv. Dabei gilt:

Lesen 37E4 - 37E7, 14308 - 14311 => Leitung C 5 der Buchsen VG4 - VG13 nimmt Low-Pegel an.

-----

Schreiben 37E4 - 37E7, 14308 - 14311 => Leitung C 8 der Buchsen VG4 - VG13 nimmt Low-Pegel an.

Diese Speicherstellen und Leitungen stehen im Prinzip zur freien Verfügung, obwohl wir uns vorbehalten mögliche Erweiterungen über diese Speicherstellen zu betreiben.

Über den Bereich 37E8 - 37EB, 14312 - 14315 können Sie einen an Stecker S3 der I/O Karte angeschlossenen Drucker betreiben. Dabei gilt:

Schreiben von 37E8 - 37EB, 14312 - 14315

-----

Die über die Speicherstellen übergebenen Daten werden am Stecker S3 parallel zur Verfügung gestellt und gleichzeitig wird die STROBE-Leitung (Pin 15 von S3) aktiv, d. h. der Drucker übernimmt die Daten.

Lesen von 37E8 - 37EB, 14312 - 14315

-----

Über die oberen 4 BIT können Sie die Statusinformation des Druckers bestimmen. Die einzelnen BIT's haben folgende Bedeutung:

- BIT 4 => Direkte Funktion des Eingangs UNIT FAULT , S3:11

- BIT 5 => Direkte Funktion des Eingangs UNIT SELECT, S3:12

- BIT 6 => Direkte Funktion des Eingangs PAPER EMPTY, S3:13

- BIT 7 => Direkte Funktion des Eingangs BUSY , S3:14

**Beispiel:**

```

PRINT LD A,C      ;Übergabe des zu druckenden Zeichens

LD (37E8H),A ;Zeichen zum Drucker

LD A,PARA1   ;PARA1 ist Druckerabhängiger Zeitwert

LOOP  DEC A      ;A=A-1

JR NZ,LOOP  ;Wenn A<>0, springe nach LOOP

SCANN LD A,(37E8H);Druckerstatus lesen

OR 0FH      ;PARA2 hängt von den angeschlossenen

CP PARA2   ;Steuerleitungen ab. (S3:11-14)

JR NZ,SCANN;Warten bis Drucker fertig

RET         ;zurück zum Hauptprogramm

```

Über die Adressen 37EC - 37FF, 14316 - 14319 werden alle Diskettenzugriffe ausgeführt. Dabei gilt:

37EC, 14316 => Kommando/Status Register

37ED, 14317 => TRACK - Register

37EE, 14318 => SECTOR - Register

37EF, 14319 => DATA - Register

Weitere Informationen über die Programmierung der Floppy-Kontroller SAB X791 entnehmen Sie bitte einschlägiger Literatur.

Es gilt ferner:

Schreiben von FE, 254 nach 37EC, 14316 => Single Density

Schreiben von FF, 255 nach 37EC, 14316 => Double Density

Schreiben von 80, 128 nach 37EE, 14318 => S1 aktiv (5")

Schreiben von C0, 192 nach 37EE, 14318 => S2 aktiv (8")

Das oben gesagte gilt sinngemäß auch für den Bereich 37F0 - 37FF, 14320 - 14335.

**3. Keyboard Baugruppe**

Innerhalb des Hauptspeichers meldet sich das Keyboard im Adressbereich 3800 - 38FF, 14336 - 14591. Dabei gibt es noch 3 Echos bei 3900 - 39FF, 14592 - 14847, 3A00 - 3AFF, 14848 - 15103 und 3B00 - 3BFF, 15104 - 15359. Da es sich um eine reine INPUT Baugruppe handelt, kann der Bereich nur gelesen werden. Ein Schreibbefehl "auf" das Keyboard wird nicht ausgeführt. Bei dem verwendeten Keyboard handelt es sich um eine sogenannte "Offene X-Y-Matrix", d. h. jedes Zeichen muß nach einem bestimmten Verfahren berechnet werden. Es hat sich gezeigt, daß man gerade dieses Verfahren nicht mit einem ganz genau festgelegten Programm lösen kann; daher verweisen wir an dieser Stelle auf die Literatur, z. B. das ROM-Listing.

Für die Matrixbelegung ergibt sich folgendes Bild:

| Adr/Bit : | 0 | :   | 1 | :   | 2 | :   | 3 | :   | 4 | :    | 5 | :   | 6 | :   | 7 | :   |   |

|-----------|---|-----|---|-----|---|-----|---|-----|---|------|---|-----|---|-----|---|-----|---|

| 3801H     | : | S   | : | A   | : | B   | : | C   | : | D    | : | E   | : | F   | : | G   | : |

| 3802H     | : | H   | : | I   | : | J   | : | K   | : | L    | : | M   | : | N   | : | O   | : |

| 3804H     | : | P   | : | Q   | : | R   | : | S   | : | T    | : | U   | : | V   | : | W   | : |

| 3808H     | : | X   | : | Y   | : | Z   | : | Ä   | : | Ö    | : | Ü   | : | ß   | : | EOF | : |

| 3810H     | : | 0   | : | !/1 | : | "/2 | : | #/3 | : | \$/4 | : | %/5 | : | &/6 | : | '/7 | : |

| 3820H     | : | (/8 | : | )/9 | : | */: | : | +/: | : | ,/〈  | : | -/= | : | ./> | : | //? | : |

| 3840H     | : | ENT | : | CLE | : | BRE | : | P.O | : | P.U  | : | P.L | : | P.R | : | SPB | : |

| 3880H     | : | SHI | : | :   | : | :   | : | :   | : | :    | : | :   | : | P 1 | : | P 2 | : |

Dabei bedeutet: ENT = ENTER, CLE = CLEAR, BRE = BREAK

: P.O = Pfeil oben, P.U = Pfeil unten

: P.L = Pfeil links, P.R = Pfeil rechts

Beispiel:

Ein Programm, welches zum Beispiel das Keyboard nach der Taste "S" abfragt, stellt sich etwa folgendermaßen dar:

|      |     |            |                                |

|------|-----|------------|--------------------------------|

| KEYS | LD  | A, (3804H) | ;Dritte Matrix-Zeile nach A    |

|      | AND | 08H        | ;Maskieren BIT 3 => Spalte "S" |

|      | JR  | Z,KEYS     | ;Warte bis "S" gedrückt wird   |

|      | LD  | A, 'S'     | ;ASCII-Wert für "S" nach A     |

|      | RET |            | ;Zurück zum Hauptprogramm      |

Achtung:

Bei den Tastenmodulen des Keyboards handelt es sich um hochwertige SIEMENS Module mit integrierter Diode, so daß echter N-Key-Rollover Betrieb möglich ist.

Die rastende Taste mit der Bezeichnung "LSP" (Feuerknopf) dient zur permanenten Herabsetzung des Systemtaktes auf 1.77 MHz, unabhängig von irgendwelchen BIT-Kombinationen des System-Bytes 0.

#### 4. Video Baugruppe

Der Speicherbereich 3C00 - 3FFF, 15360 - 16383 wird von der Video-Baugruppe als Bildwiederholspeicher verwaltet. Dabei wird beginnend bei Adresse 3C00, 15360 für die linke obere Ecke zeilenweise der Speicherinhalt in BIT-Kombinationen des Zeichen-ROM's umgesetzt und als Zeichen auf dem Monitor dargestellt, so daß sich für die untere rechte Ecke, bei einem Format von 64 x 16, die Speicherstelle 3FFF, 16383 ergibt. Wird über das Systé-Byte 0 der Hauptspeicherbereich durchgehend freigegeben, bleibt die Wiederholfunktion zwar erhalten, aber der Videospeicher kann nun nicht mehr geändert werden.

**BUS-Belegung: SpeedMaster 5.3**

=====

VIDEO-Slot's

Über die BUS-Stecker VG1 - VG3 haben Sie die Möglichkeit, das System Ihren Wünschen entsprechend selbst zu erweitern.

Für die BUS-Belegung der VG-Leisten VG1 - VG3 ergibt sich, von oben gesehen, folgendes Bild:

| Reihe A |               | Reihe C |             |

|---------|---------------|---------|-------------|

| =====   |               | =====   |             |

| PIN     | Belegung      | PIN     | Belegung    |

| 1       | + 12 Volt     | 1       | Masse       |

| 2       | (R) WAITHOLD2 | 2       | GA00        |

| 3       | AMUX          | 3       | GA01        |

| 4       | HON           | 4       | GA02        |

| 5       | GRAPHIC       | 5       | GA03        |

| 6       | VIDEO         | 6       | GA04        |

| 7       | ENABLE        | 7       | GA05        |

| 8       | 32CH          | 8       | GA06        |

| 9       | LATCH         | 9       | GA07        |

| 10      | SHIFT         | 10      | GA08        |

| 11      | (T) (Z) RFSH  | 11      | GA09        |

| 12      | (T) (Z) CLOCK | 12      | GA10        |

| 13      | (R) HGRVID    | 13      | GA11        |

| 14      | SYSRES        | 14      | GA12        |

| 15      | (T) (Z) MREQ  | 15      | GA13        |

| 16      | (T) (Z) OUT   | 16      | (T) (Z) DO  |

| 17      | (R) WAITHOLD  | 17      | (T) (Z) D1  |

| 18      | (Z) WAIT      | 18      | (T) (Z) D2  |

| 19      | VERT          | 19      | (T) (Z) D3  |

| 20      | 10M           | 20      | (T) (Z) D4  |

| 21      | HORT          | 21      | (T) (Z) D5  |

| 22      | (T) (Z) WR    | 22      | (T) (Z) D6  |

| 23      | (T) (Z) RD    | 23      | (T) (Z) D7  |

| 24      | (T) (Z) A0    | 24      | (T) (Z) A15 |

| 25      | (T) (Z) A1    | 25      | (T) (Z) A14 |

| 26      | (T) (Z) A2    | 26      | (T) (Z) A13 |

| 27      | (T) (Z) A3    | 27      | (T) (Z) A12 |

| 28      | (T) (Z) A4    | 28      | (T) (Z) A11 |

| 29      | (T) (Z) A5    | 29      | (T) (Z) A10 |

| 30      | (T) (Z) A6    | 30      | (T) (Z) A9  |

| 31      | (T) (Z) A7    | 31      | (T) (Z) A8  |

| 32      | - 5 Volt      | 32      | + 5 Volt    |

**Achtung:**

=====

Alle mit (Z) gekennzeichneten PIN's sind Z-80 oder nach ZILOG Spezifikationen abgeleitete Signale (Output: TTL-Pegel, Input: je nach Type).

Alle mit (T) gekennzeichneten PIN's können mittels des Signals ENABLE im dem TRI-State Bereich gebracht werden.

Alle mit (R) gekennzeichneten PIN's sind reserviert und sollten nicht benutzt werden.

In den Slot's VG1 - VG3 müssen die Karten VIDEO 1.2 und GRAPHIC 1.5 stecken. Die Karten werden in den Slot's VG4 - VG13 zerstört !!!

An den unten aufgeführten PIN's steht Ihnen die jeweils angegebene Spannung zur Verfügung. Die Ausgänge des Netzteils sind kurzschlußfest.

PIN A 1 => + 12 Volt, 1.0 Amp.

PIN C32 => + 5 Volt, 4.0 Amp.

PIN A32 => - 5 Volt, 0.1 Amp.

PIN C 1 => gemeinsame Masse

Für alle anderen PIN's gilt => Output: TTL-Pegel

Input : je nach Type

Die PIN's im einzelnen:

Reihe A:

PIN 2 : Output. Diese Leitung zeigt dem Wait-Zyklen-Generator (WZG) durch High-Pegel an, daß die Karte GRAPHIC 1.5 für einen Datenaustausch noch nicht bereit ist.

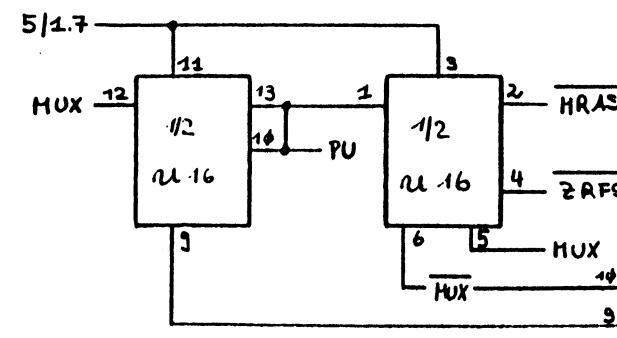

PIN 3 : Output. Nimmt diese Leitung Low-Pegel an, so liegen an Reihe C, Pin 2 bis 15 die CPU-Adressen A0 bis A13, bei High Pegel die Bildwiederholadressen GA00 bis GA13.

PIN 4 : Output: Dieser Pin zeigt dem BIT-IMAGE-Mischer der Karte VIDEO 1.2 durch High-Pegel an, daß das über Reihe a, Pin 13 anliegende Signal mit der Video-information gemischt werden soll.

Der Pegel ist direkt mit System-Byte 0, BIT 1 gekoppelt.

PIN 5 : Output. Ist System-Byte 0, BIT 7 auf Low und BIT 3 auf High, nimmt diese Leitung im Adressbereich 0000 - 3FFF 00000 - 16383 Low-Pegel an.

PIN 6 : Output. Ist System-Byte 0, BIT 3 auf Low und BIT 0 auf Low, nimmt diese Leitung im Adressbereich 3000 - 3FFF, 15360 - 16383 Low-Pegel an.

PIN 7 : Input. Mittels dieser Leitung können Zusatzbaugruppen (ZBG) alle mit (T) gekennzeichneten PIN's in den TRI-State Bereich bringen, und somit den externen Daten- und Adress-BUS übernehmen.

Auf den ZBG sollte diese Leitung als Open-Collector ausgelegt sein, damit mehrere ZBG eine Anforderung stellen können.

PIN 8 : Output. Diese Leitung zeigt der Karte VIDEO 1.2 den Zustand von Port FF, 255 BIT 3 in negierter Form an.

PIN 9 : Output. Dieser Pin gibt durch Low-Pegel das HGR-Schieberegister der Karte GRAPHIC 1.5 zur neuen Datenübernahme aus dem HGR-Wiederholspeicher frei.

PIN 10 : Output. An diesem steht die Video-Taktrate zur Verfügung.

Reihe a, Pin 8 = Low => 5.35 MHz

Reihe a, Pin 8 = High => 10.70 MHz

PIN 11 : Output. Geht RFSH zusammen mit MREQ auf Low, können die unteren 7 BIT des Adressbusses als Refresh-Adresse für dynamische RAM's benutzt werden.

PIN 12 : Output. An diesem Pin stellt das System den momentanen CPU Takt zur Verfügung.

PIN 13 : Output. Über diese Leitung stellt die Karte GRAPHIC 1.5 dem BIT-IMAGE-Mischer ihre Grafikinformation bereit. Siehe auch Reihe a, Pin 4

PIN 14 : Output. Diese Leitung geht immer dann auf Low-Pegel, wenn beide RESET-Tasten auf dem Keyboard gedrückt werden oder die CPU einen HALT-Befehl ausführt. Beim Einschalten des Systems bleibt die Leitung für ca. 1 Sekunde auf Low und nimmt dann automatisch High-Pegel an.

PIN 15 : Output. Dieser Pin zeigt durch Low-Pegel an, daß auf dem Adressbus eine gültige Adresse für Schreib- oder Lese-Zyklen anliegt.

PIN 16 : Output. Diese Leitung zeigt durch Low-Pegel an, daß IOREQ und WR der CPU auf Low liegen (Port-Write).

PIN 17 : Output. Diese Leitung zeigt dem WZG durch High-Pegel an, daß entweder die Karte GRAPHIC 1.5 oder VIDEO 1.2 für einen Datenaustausch noch nicht bereit ist.

PIN 18 : Input. Ein Low-Pegel an dieser Leitung zeigt der CPU an, daß der adressierte Speicher- oder I/O Bereich für einen Datentransfer noch nicht bereit ist. Die CPU fügt solange WAIT-Zyklen ein, bis die Leitung wieder einen High-Pegel annimmt. Die Leitung sollte als Open-Collector ausgelegt sein.

Achtung:

=====

Wird die Leitung zu lange auf Low gesetzt, kann es zu Datenverlust im Hauptspeicher kommen, da die CPU während dieser Zeit keinen Refresh ausführt.

PIN 19 : Output. An diesem Pin liegt das Vertikal-Anfangssignal der Karte VIDEO 1.2 (nicht Vertikal-SYNC!).

PIN 20 : Output. An dieser Leitung kann das Videotaktsignal mit konstant 10.70 MHz abgegriffen werden.

PIN 21 : Output. An diesem Pin liegt das Horizontal-Anfangssignal der Karte VIDEO 1.2 (nicht Horizontal-SYNC!).

PIN 22 : Output. Diese Leitung zeigt durch Low-Pegel an, daß MREQ und WR der CPU auf Low liegen (Memory-WRITE).

PIN 23 : Output. Diese Leitung zeigt durch Low-Pegel an, daß MREQ und RD der CPU auf Low liegen (Memory-READ).

An den PIN's 24 bis 31 liegen die Z-80 Adressen A0 - A7.

**Reihe C:**

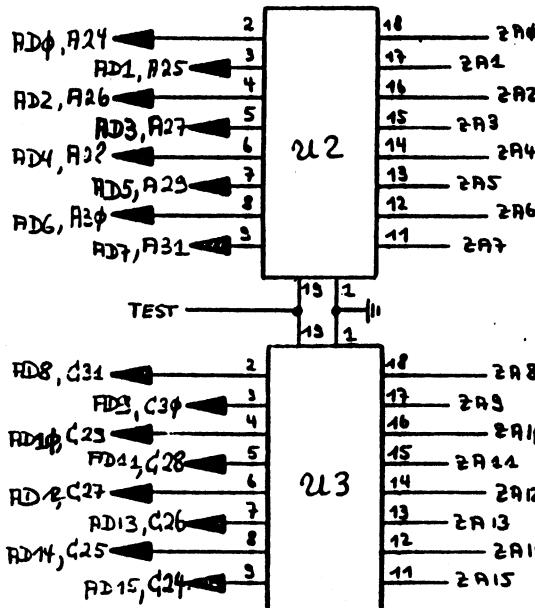

An den PIN's 2 bis 15 liegen je nach Pegel von Reihe a, Pin 3 entweder die CPU Adressen A0 bis A13 oder die Bildwiederholadressen GA00 bis GA13.

An den PIN's 16 bis 23 liegt der Z-80 Datenbus D0 bis D7.

An den PIN's 24 bis 31 liegen die Z-80 Adressen A15 bis A8.

**Achtung:**

Alle BUS-Signale, die einen TTL-Pegel haben und als Output deklariert sind, können mit durchschnittlich 5 Eingängen belastet werden. Für die mit (T) gekennzeichneten Signale gilt ein Lastfaktor von 40.