Programmierung der

**Z80**

**RODNAY ZAKS**

# **Programmierung des Z80**

5

6

7

# **Programmierung des Z80**

**Rodnay Zaks**

---

**Anmerkung:**

Z80 ist ein geschütztes Warenzeichen von ZILOG Inc., USA.

Originalausgabe in Englisch

Titel der englischen Ausgabe: Programming the Z80

Original Copyright © 1980 by SYBEX Inc., Berkeley, USA

**Deutsche Übersetzung: Bernd Ploss**

Umschlag: Daniel Le Noury

Satz: tgr typo-grafik-repro gmbH., Remscheid

Gesamtherstellung: Druckerei Hub. Hoch, Düsseldorf

Der Verlag hat alle Sorgfalt walten lassen, um vollständige und akkurate Informationen zu publizieren. SYBEX-Verlag GmbH, Düsseldorf, übernimmt keine Verantwortung für die Nutzung dieser Informationen, auch nicht für die Verletzung von Patent- und anderen Rechten Dritter, die daraus resultieren. Hersteller behalten das Recht, Schaltpläne und technische Charakteristika ohne Bekanntgabe an die Öffentlichkeit zu ändern. Für genaue technische Daten auf dem neuesten Stand wird der Leser an die Hersteller verwiesen.

ISBN 3-88745-006-X

1. Auflage 1982

2. Auflage 1982

3. Auflage 1983

4. Auflage 1983

5. Auflage 1984

6. Auflage 1984

Alle deutschsprachigen Rechte vorbehalten. Kein Teil des Werkes darf in irgendeiner Form (Druck, Fotokopie, Mikrofilm oder einem anderen Verfahren) ohne schriftliche Genehmigung des Verlages reproduziert oder unter Verwendung elektronischer Systeme verarbeitet, vervielfältigt oder verbreitet werden.

Printed in Germany

Copyright © 1982, SYBEX-Verlag GmbH., Düsseldorf

---

# Dankwort

Der Entwurf eines Textbuches über Programmierung ist immer schwierig. Ein solches Buch aber so zu konzipieren, daß es als Einführung in die Programmierung taugt und trotzdem fortgeschrittene Konzepte präsentiert, ohne daß Hardware- und Softwareaspekte außer acht gelassen werden, ist eine Herausforderung. Der Autor möchte sich hier für die vielen Vorschläge zu Verbesserungen und Änderungen des Buches bei O. M. Barlow, Dennis L. Feick, Richard D. Reid, Stanley E. Erwin, Philip Hooper, Dennis B. Kitsz, R. Ratke und Jim Crocker bedanken. Sein besonderer Dank gilt Chris Williams für seine Beiträge zu dem Z80 Instruktions-Set und dem Kapitel über Datenstrukturen.

Alle weiteren Vorschläge zur Verbesserung oder Änderung des Buches sollten an den Verlag geschickt werden.

Die Tabellen zu den Hexadezimal-Kodes der Z80-Instruktionen in Kapitel 4 sind mit Genehmigung von Zilog Inc, USA, nachgedruckt. Tabellen 2.26 und 2.27 wurden mit Genehmigung von Intel Corporation, USA, abgedruckt.

## Inhaltsverzeichnis

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| <b>I.</b>    | <b>Grundbegriffe</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 17  |

|              | Einführung, Was ist Programmierung?, Flußdiagramme, Darstellung von Information                                                                                                                                                                                                                                                                                                                                                                                                                            |     |

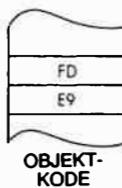

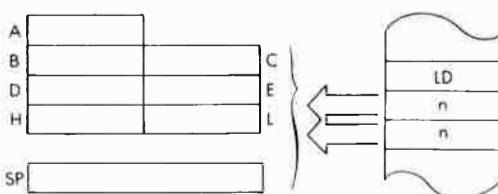

| <b>II.</b>   | <b>Z80 Hardware Organisation</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 43  |

|              | Einführung, Systemarchitektur, Interne Organisation des Z80, Befehlsformate, Befehlausführung durch den Z80, Zusammenfassung                                                                                                                                                                                                                                                                                                                                                                               |     |

| <b>III.</b>  | <b>Grundlegende Techniken der Programmierung</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 89  |

|              | Einführung, Arithmetische Programme, Multiplikation von BCD-Zahlen, Division von Dualzahlen, Zusammengefaßte Darstellung der Befehle, Unterprogramme, Zusammenfassung                                                                                                                                                                                                                                                                                                                                      |     |

| <b>IV.</b>   | <b>Der Befehlssatz des Z80</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 147 |

|              | Einführung, Klassen von Befehlen, Zusammenfassung, Beschreibung der einzelnen Befehle                                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| <b>V.</b>    | <b>Adressierungstechniken</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 429 |

|              | Einführung, Mögliche Arten der Adressierung, Die Adressierungsformen des Z80, Der Gebrauch der Z80-Adressierungsformen, Zusammenfassung                                                                                                                                                                                                                                                                                                                                                                    |     |

| <b>VI.</b>   | <b>Ein-/Ausgabetechniken</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 449 |

|              | Einführung, Eingabe und Ausgabe, Parallele wortweise Übertragung, Serielle bitweise Übertragung, Zusammengefaßte Darstellung der Peripherie, Verwaltung von Ein- und Ausgabe, Zusammenfassung                                                                                                                                                                                                                                                                                                              |     |

| <b>VII.</b>  | <b>Ein-/Ausgabegeräte</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 497 |

|              | Einführung, Die Standard-PIO, Das interne Steuerregister, Programmierung einer PIO, Die Zilog-Z80-PIO                                                                                                                                                                                                                                                                                                                                                                                                      |     |

| <b>VIII.</b> | <b>Beispiel für Anwendungen</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 507 |

|              | Einführung, Löschen eines Speicherbereichs, Abfrage von Ein-/Ausgabegeräten, Eingabe von Zeichen, Test eines Zeichens, Test eines Zeichenbereiches, Erzeugen des Paritybits, Codeumwandlung: ASCII nach BCD, Hexadezimal nach ASCII, Suchen des größten Elementes in einer Tabelle, Summe von n Elementen, Berechnung einer Prüfsumme, Zählen der Nullen, Übertragung von Blöcken, Transfer eines Blocks von BCD-Zahlen, Vergleich zweier vorzeichenbehafteter 16-Bit-Zahlen, Bubble-Sort, Zusammenfassung |     |

|                                                                                                                                                                                                       |                                   |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----|

| <b>IX.</b>                                                                                                                                                                                            | <b>Datenstrukturen</b>            | 525 |

| 1.                                                                                                                                                                                                    | Teil – Theorie                    |     |

| Einführung, Zeiger, Listen, Suchen und Sortieren, Zusammenfassung                                                                                                                                     |                                   |     |

| 2.                                                                                                                                                                                                    | Teil – Beispiele zum Entwurf      |     |

| Einführung, Darstellung der Daten in der Liste, Eine einfache Liste, Alphabetische Liste, Verkettete Liste, Zusammenfassung                                                                           |                                   |     |

| <b>X.</b>                                                                                                                                                                                             | <b>Entwicklung von Programmen</b> | 563 |

| Einführung, Grundlegende Entscheidungen, Unterstützende Software, Wie man schrittweise ein Programm entwickelt, Alternativen bei der Hardware, Der Assembler, Bedingte Assemblierung, Zusammenfassung |                                   |     |

| <b>XI.</b>                                                                                                                                                                                            | <b>Schluß</b>                     | 585 |

| Die technologische Entwicklung, Der nächste Schritt                                                                                                                                                   |                                   |     |

| <br><b>Anhang A</b>                                                                                                                                                                                   |                                   | 587 |

| Tabelle zur Umwandlung von Hexadezimalzahlen                                                                                                                                                          |                                   |     |

| <b>Anhang B</b>                                                                                                                                                                                       |                                   | 588 |

| ASCII-Tabelle                                                                                                                                                                                         |                                   |     |

| <b>Anhang C</b>                                                                                                                                                                                       |                                   | 589 |

| Tabelle relativer Sprungdistanzen                                                                                                                                                                     |                                   |     |

| <b>Anhang D</b>                                                                                                                                                                                       |                                   | 590 |

| Umwandlung dezimal nach BCD                                                                                                                                                                           |                                   |     |

| <b>Anhang E</b>                                                                                                                                                                                       |                                   | 591 |

| Der Befehlssatz des Z80                                                                                                                                                                               |                                   |     |

| <b>Anhang F</b>                                                                                                                                                                                       |                                   | 598 |

| Äquivalente Befehle: Z80–8080                                                                                                                                                                         |                                   |     |

| <b>Anhang G</b>                                                                                                                                                                                       |                                   | 599 |

| Äquivalente Befehle: 8080–Z80                                                                                                                                                                         |                                   |     |

| <b>Index</b>                                                                                                                                                                                          |                                   | 601 |

## Verzeichnis der Abbildungen

|            |                                                                |    |

|------------|----------------------------------------------------------------|----|

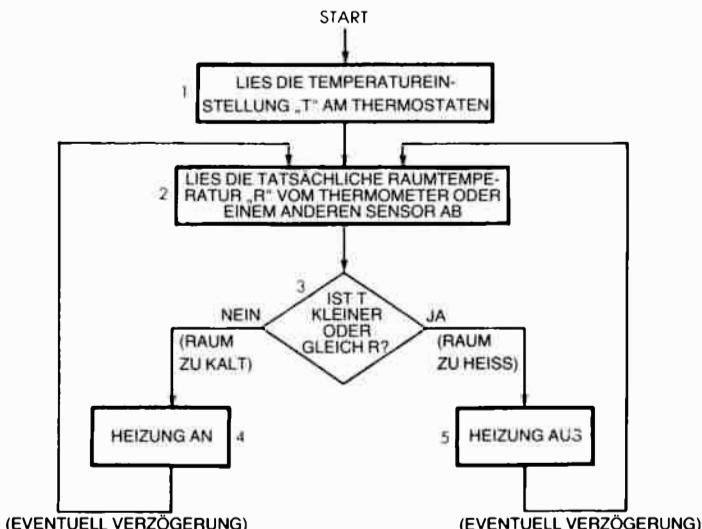

| Abb. 1.1:  | Flußdiagramm zur Konstanthaltung der Raumtemperatur . . . . .  | 19 |

| Abb. 1.2:  | Dezimal-Dual-Tabelle . . . . .                                 | 22 |

| Abb. 1.3:  | Tabelle der Zweierkomplemente . . . . .                        | 28 |

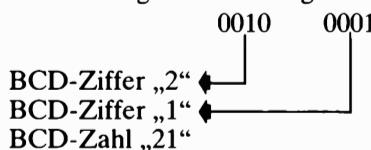

| Abb. 1.4:  | BCD Tabelle . . . . .                                          | 34 |

| Abb. 1.5:  | Typische Gleitkommadarstellung . . . . .                       | 36 |

| Abb. 1.6:  | ASCII-Umwandlungs-Tabelle . . . . .                            | 38 |

| Abb. 1.7:  | Oktale Symbole . . . . .                                       | 39 |

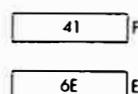

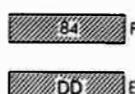

| Abb. 1.8:  | Hexadezimalkode . . . . .                                      | 41 |

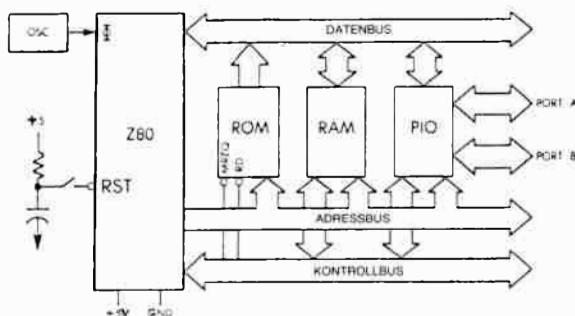

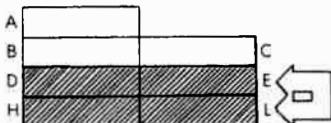

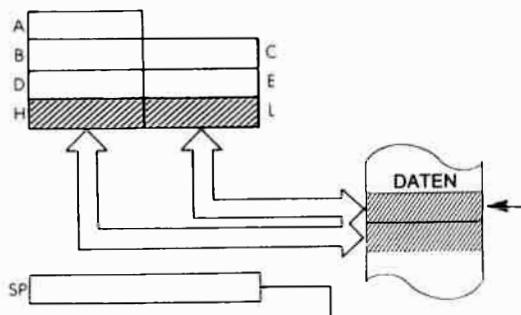

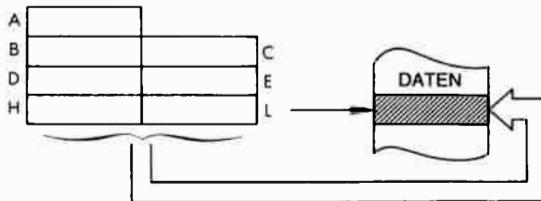

| Abb. 2.1:  | Z80-Standardsystem . . . . .                                   | 44 |

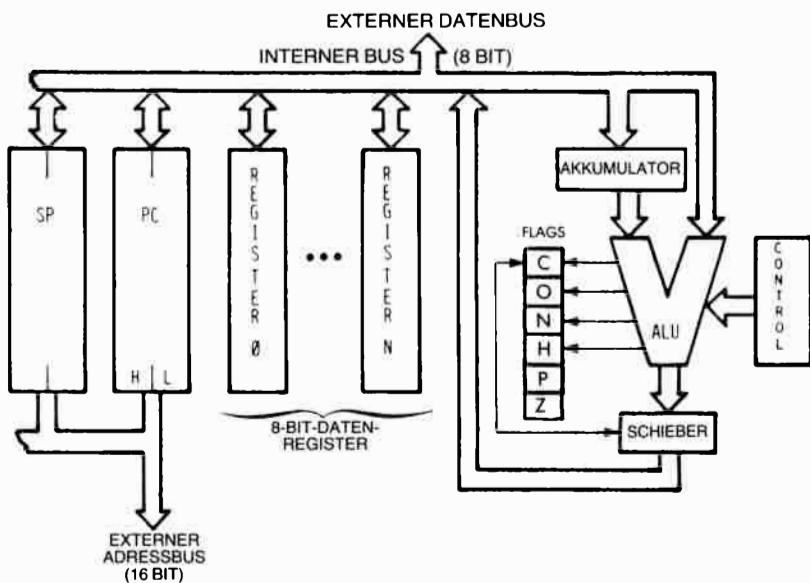

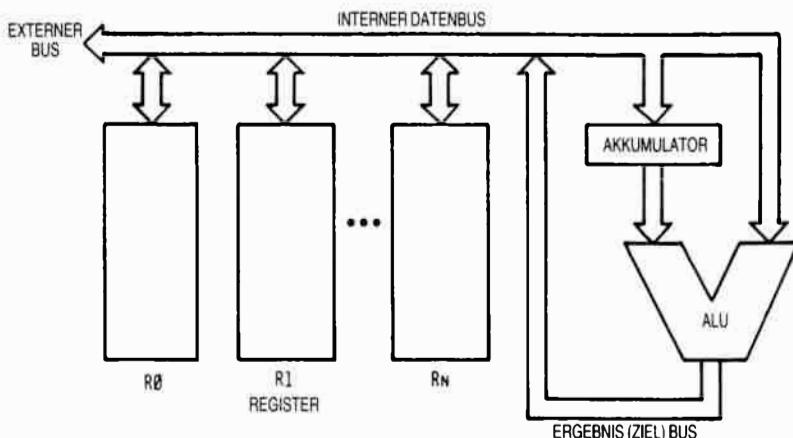

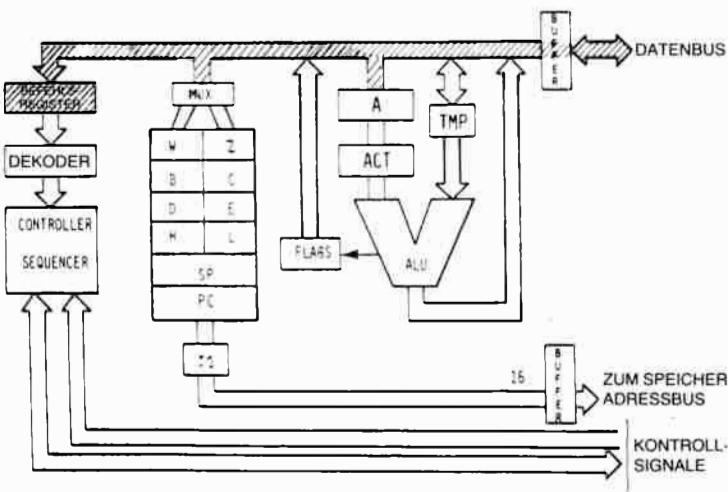

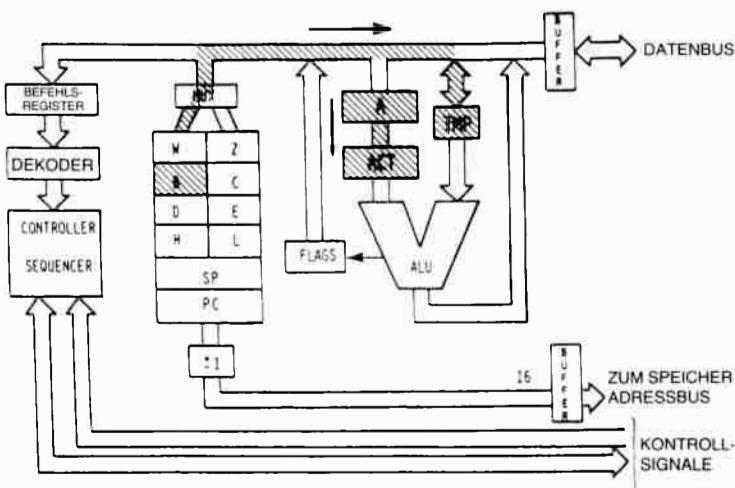

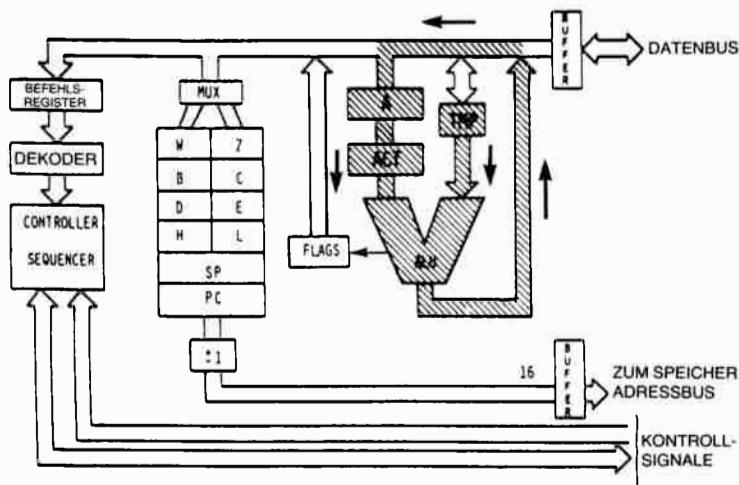

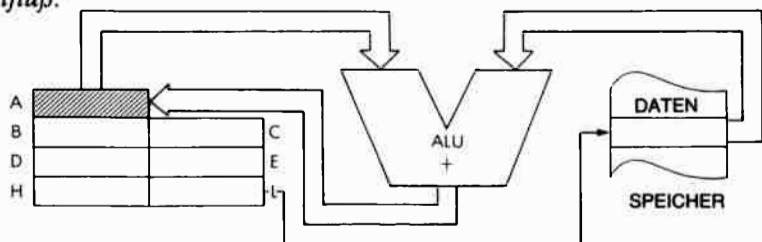

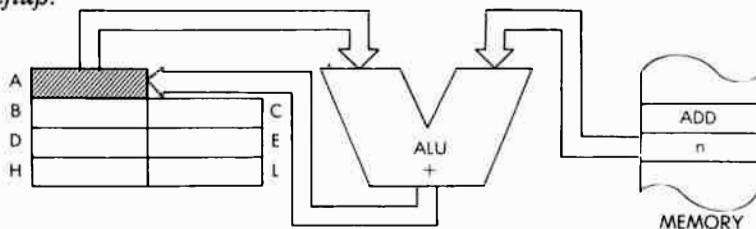

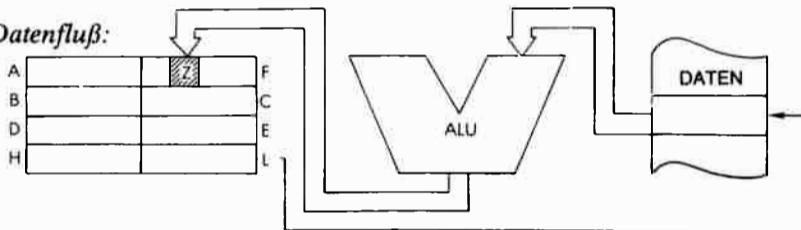

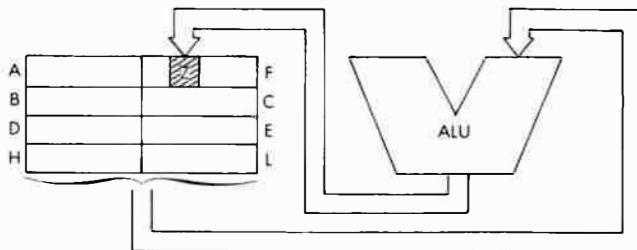

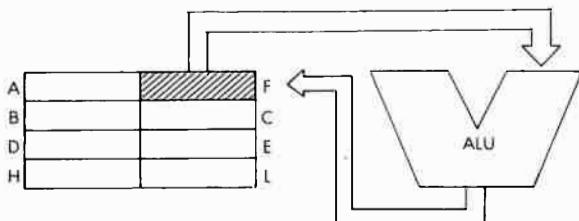

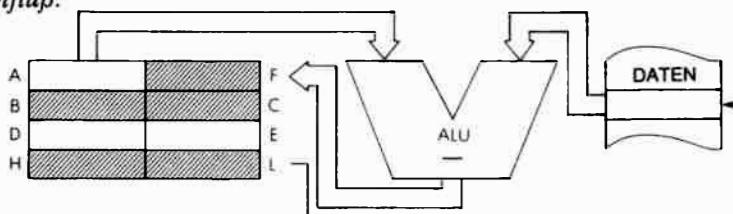

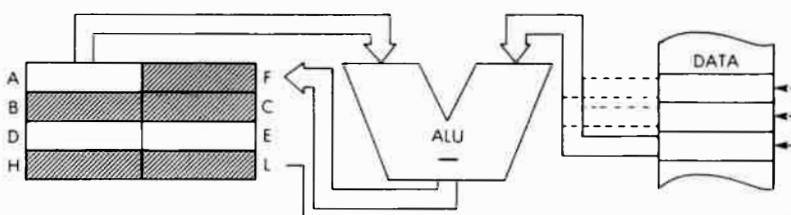

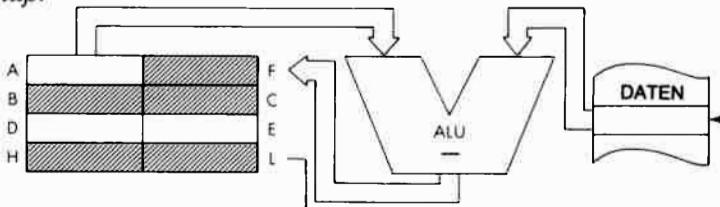

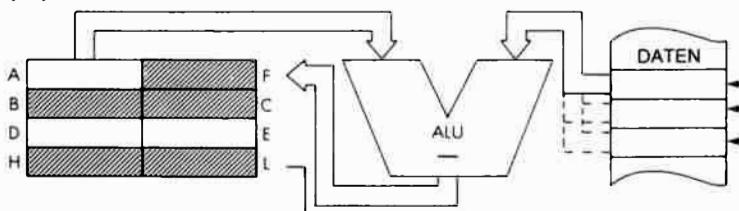

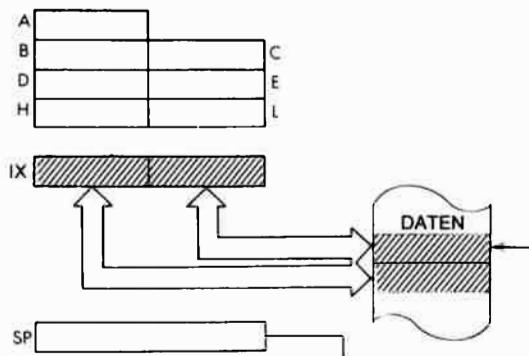

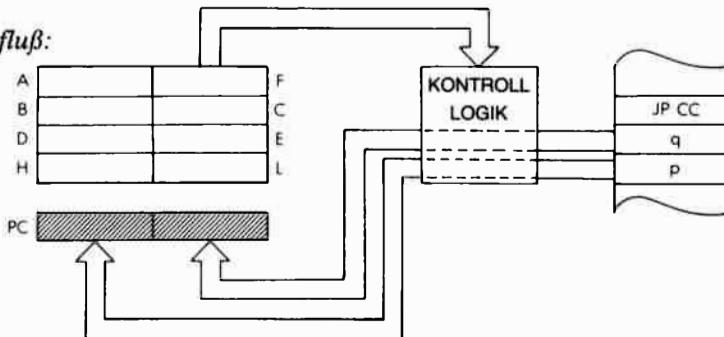

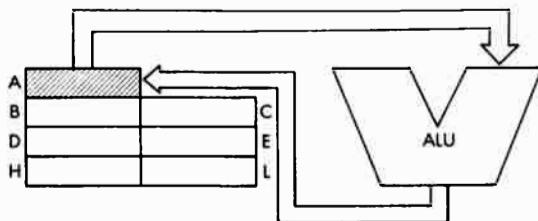

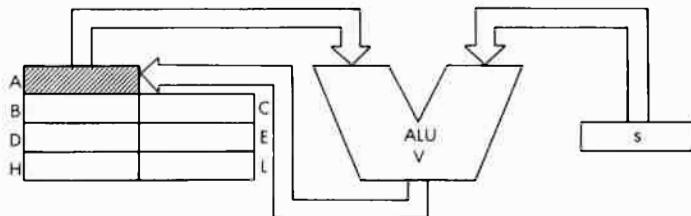

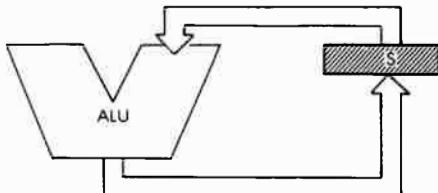

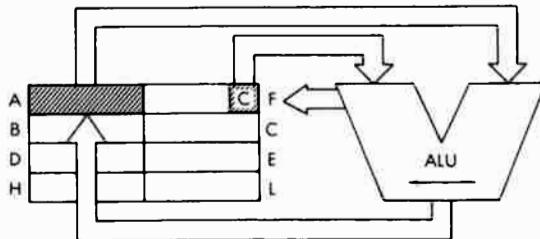

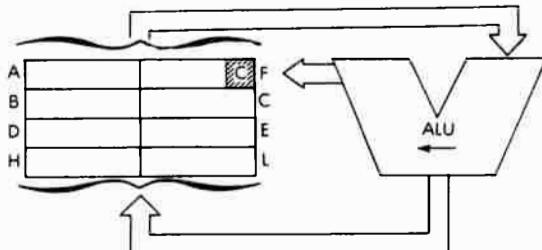

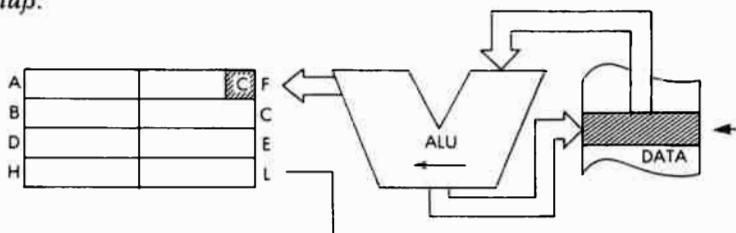

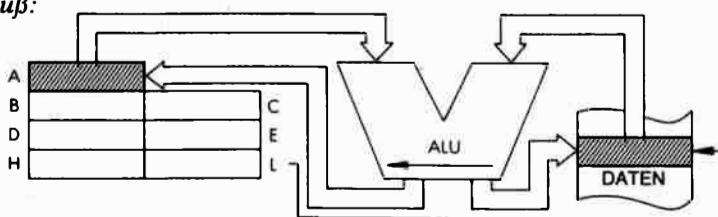

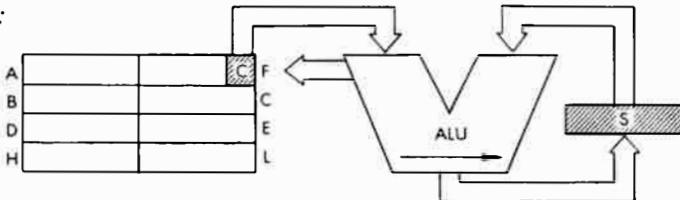

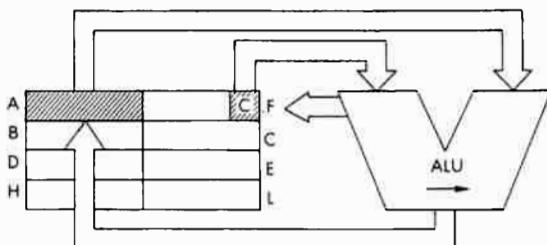

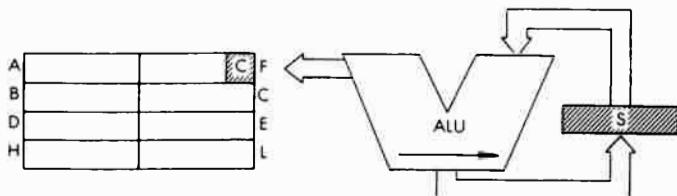

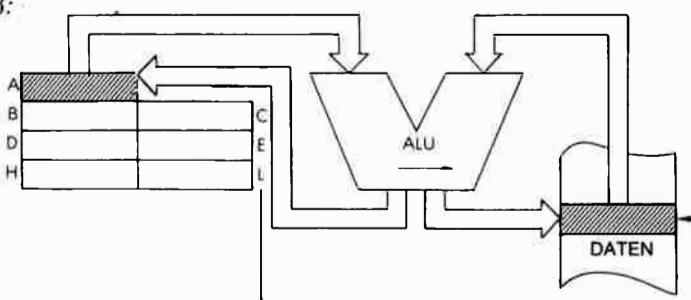

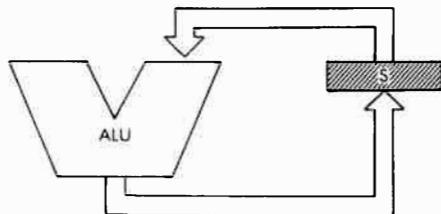

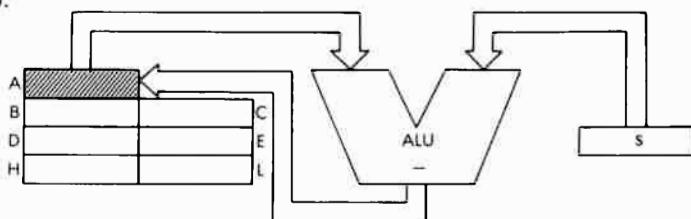

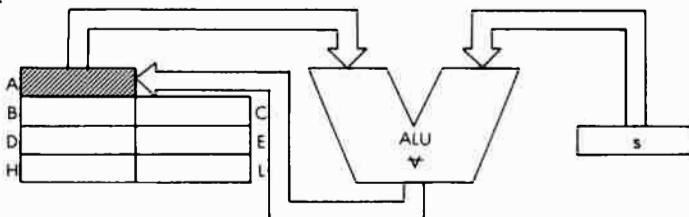

| Abb. 2.2:  | „Standardarchitektur“ eines Mikroprozessors . . . . .          | 46 |

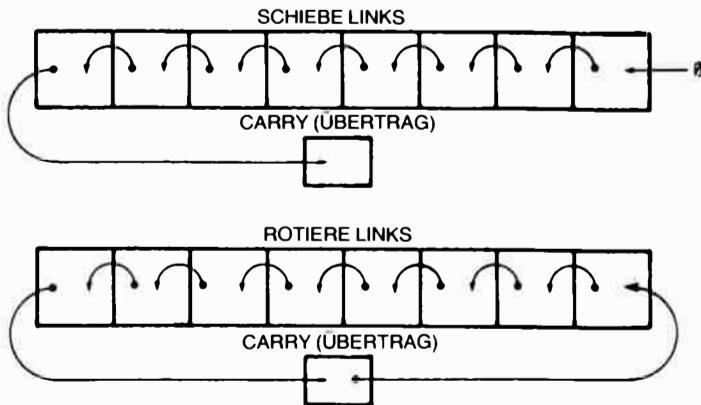

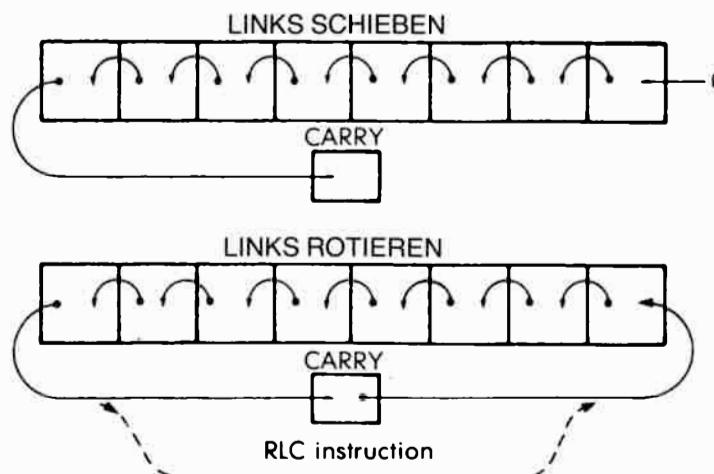

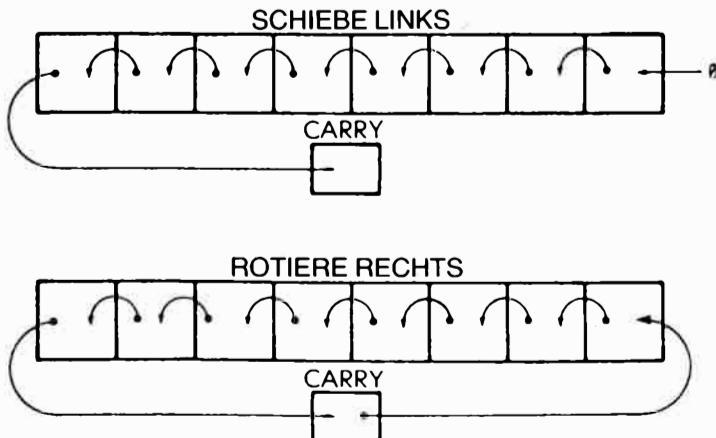

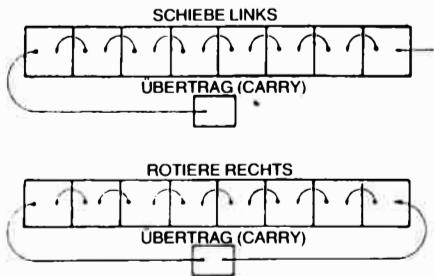

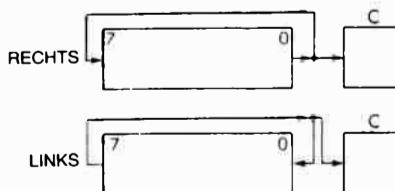

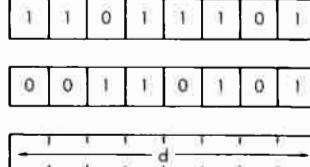

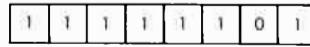

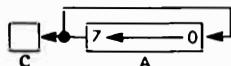

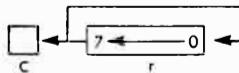

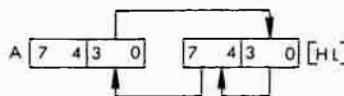

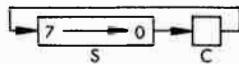

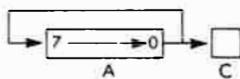

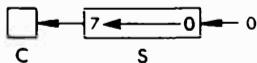

| Abb. 2.3:  | Schieben und Rotieren . . . . .                                | 47 |

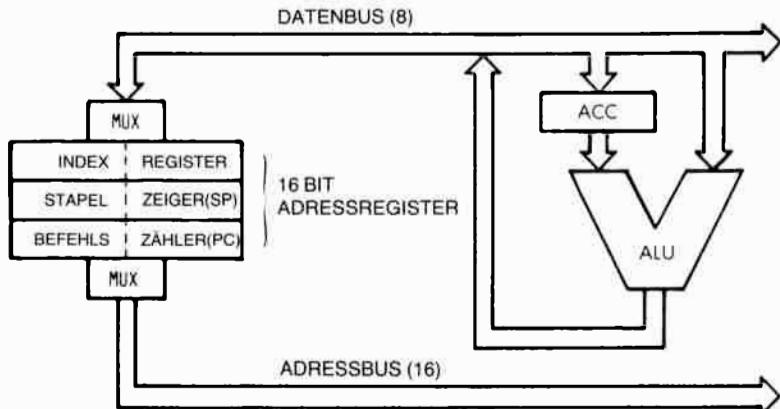

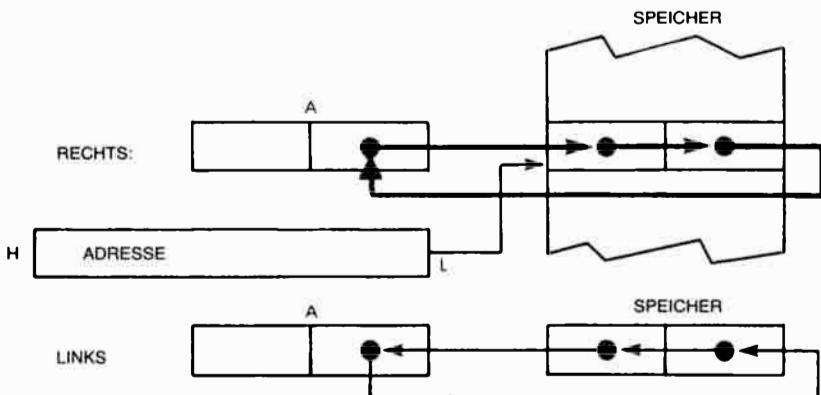

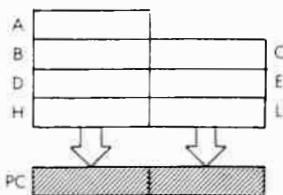

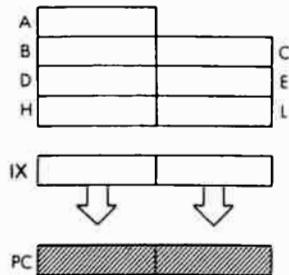

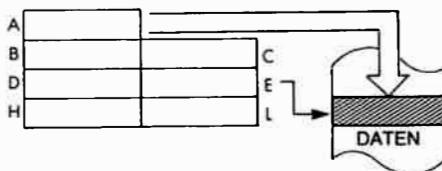

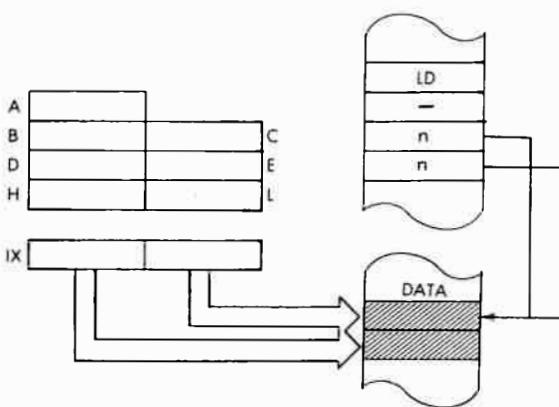

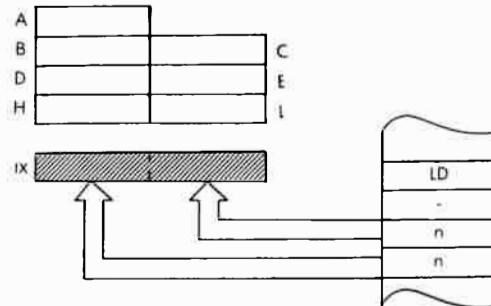

| Abb. 2.4:  | Die 16-Bit-Adresse register erzeugen den Adreßbus . . . . .    | 48 |

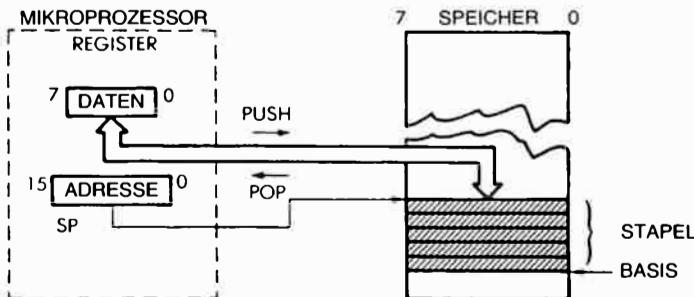

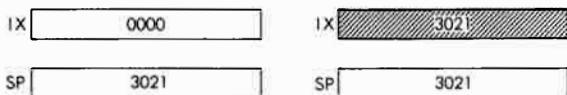

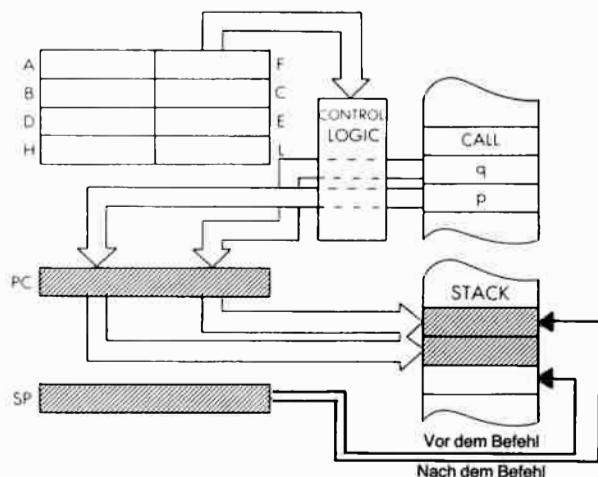

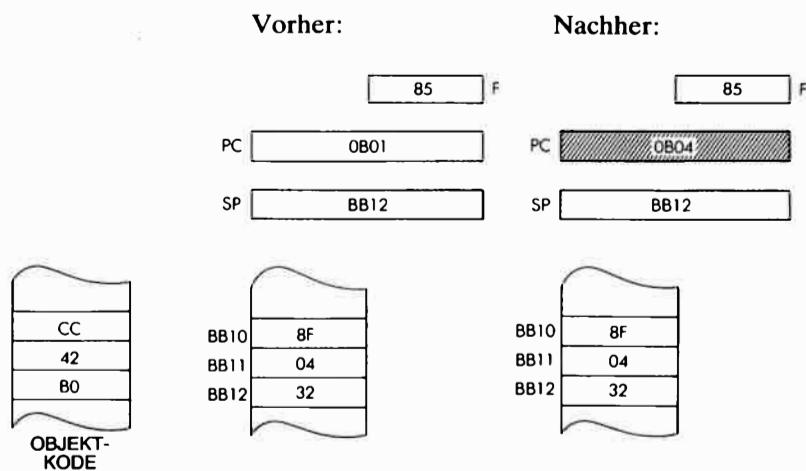

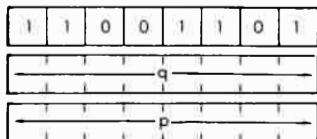

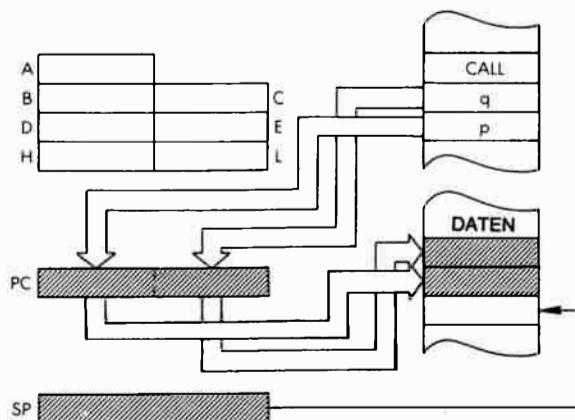

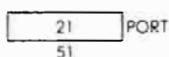

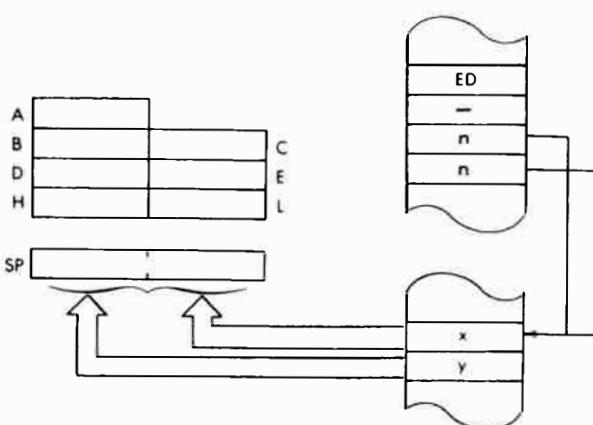

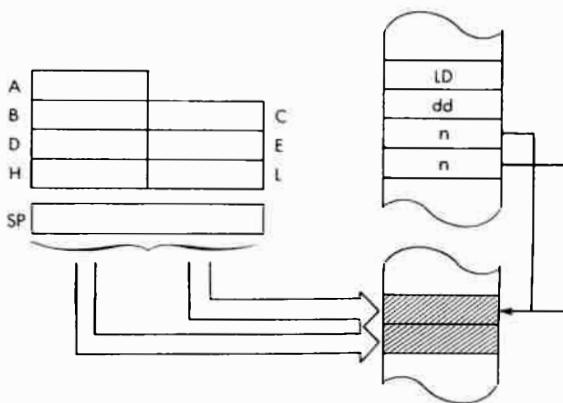

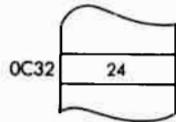

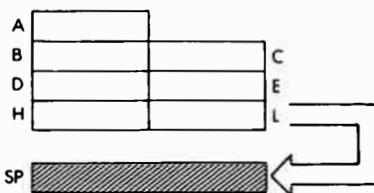

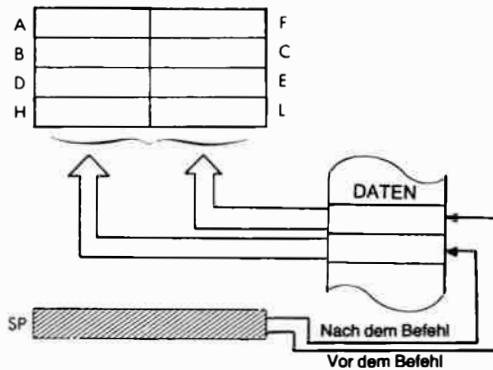

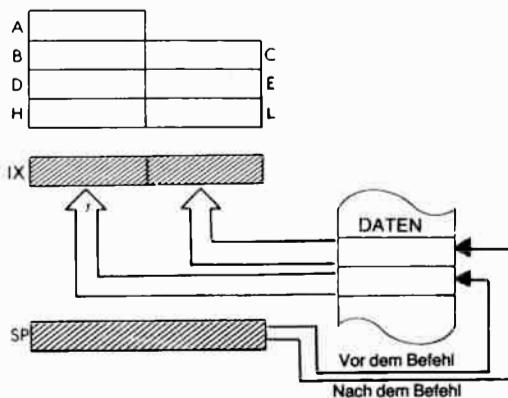

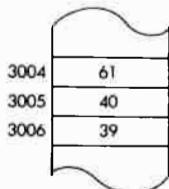

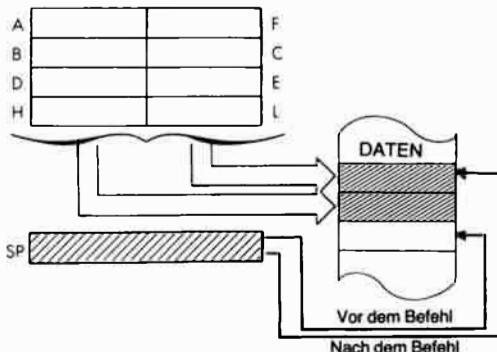

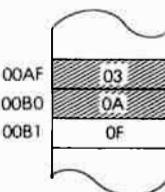

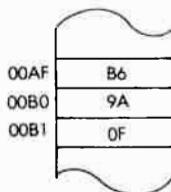

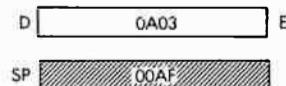

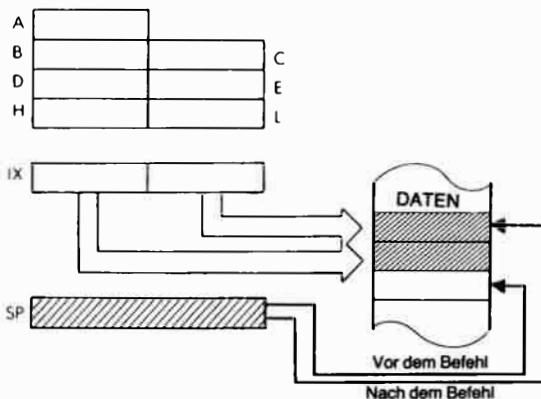

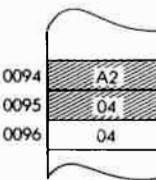

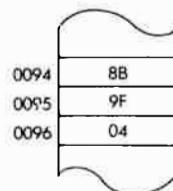

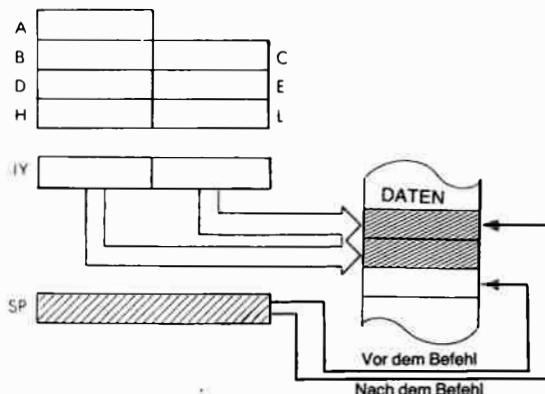

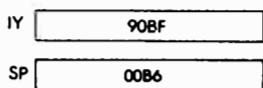

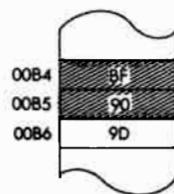

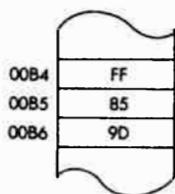

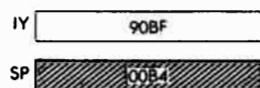

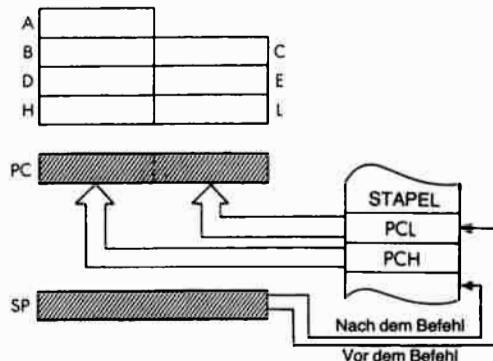

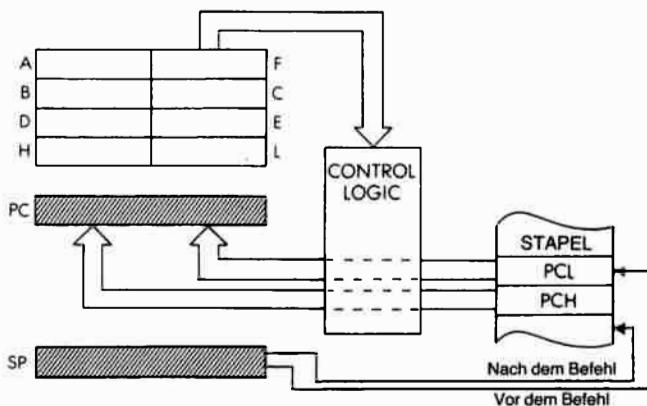

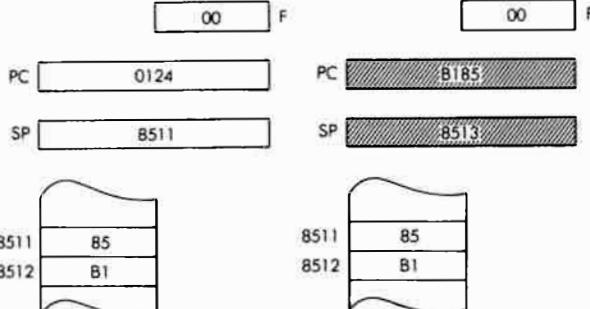

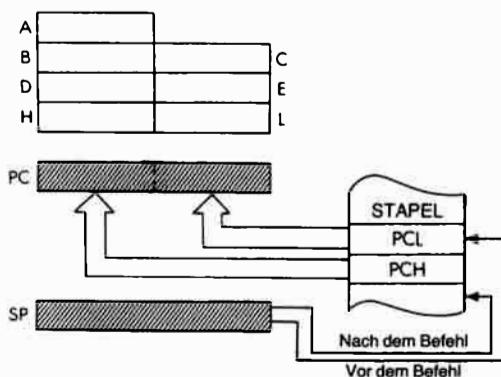

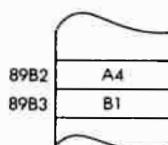

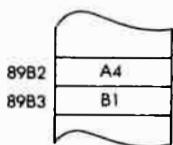

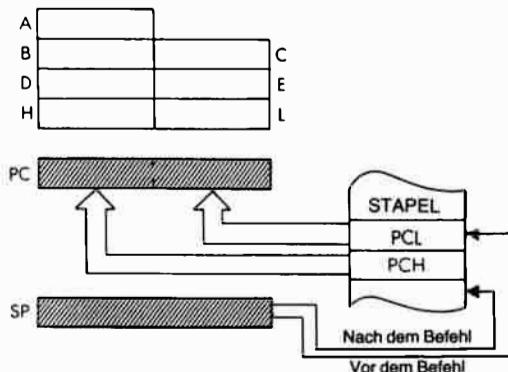

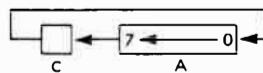

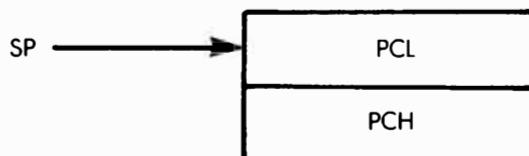

| Abb. 2.5:  | Die beiden Befehle zur Manipulation des Stapels . . . . .      | 51 |

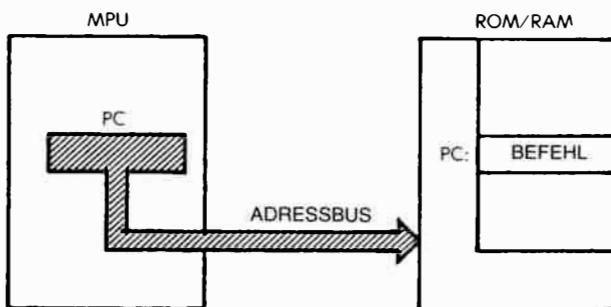

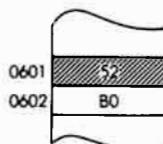

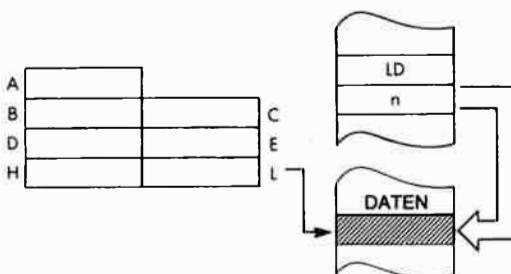

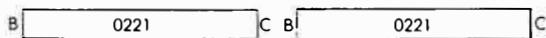

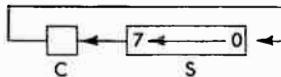

| Abb. 2.6:  | Einen Befehl aus dem Speicher holen . . . . .                  | 52 |

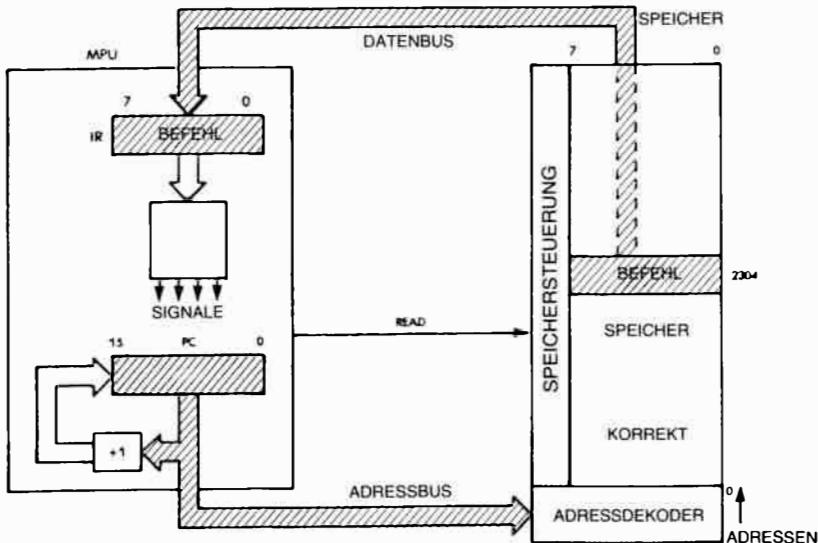

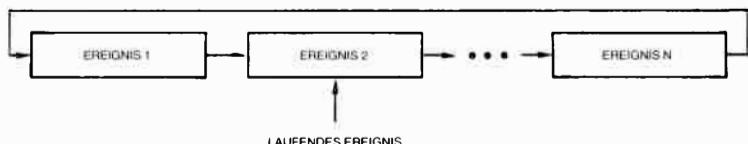

| Abb. 2.7:  | Automatische Abfolge . . . . .                                 | 52 |

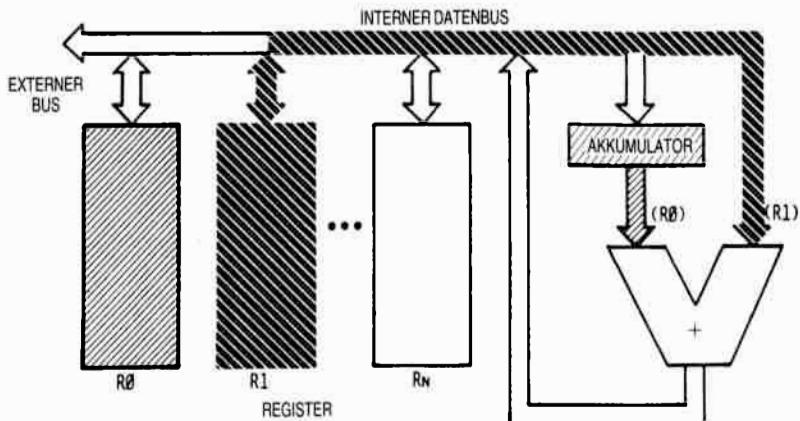

| Abb. 2.8:  | Architektur mit einem einzelnen Bus . . . . .                  | 53 |

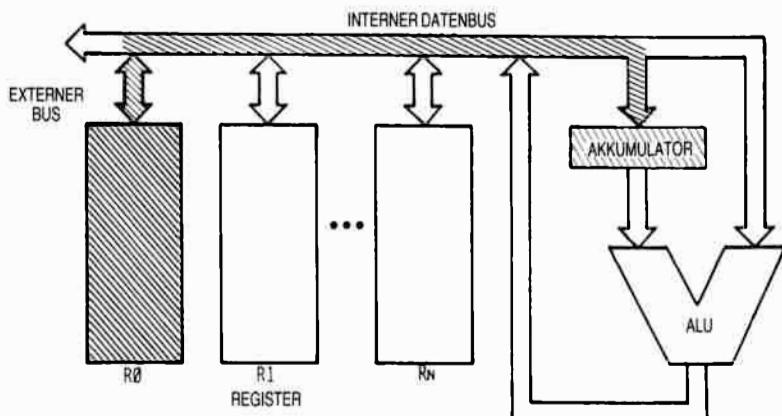

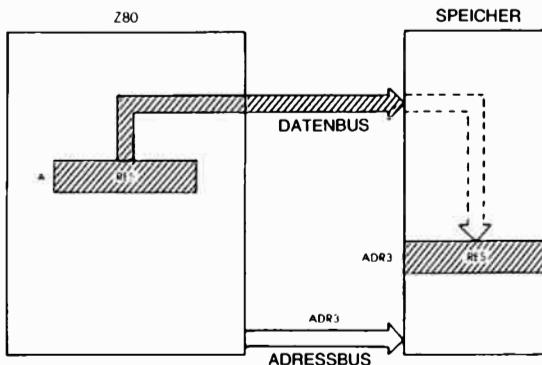

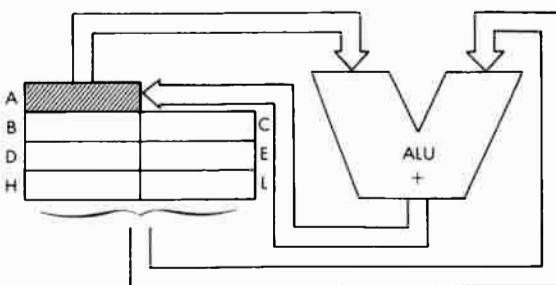

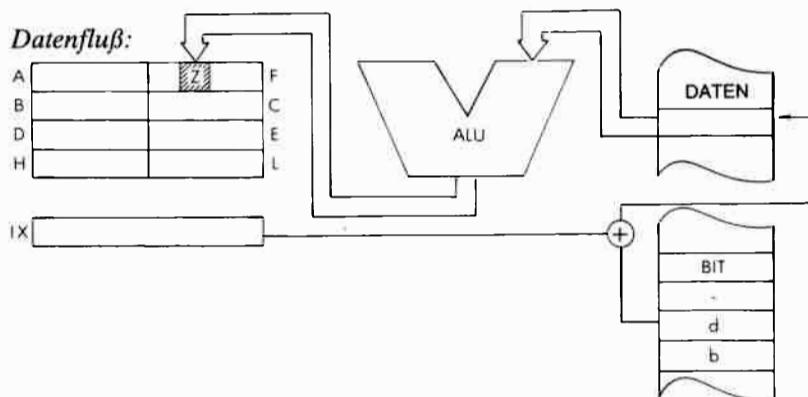

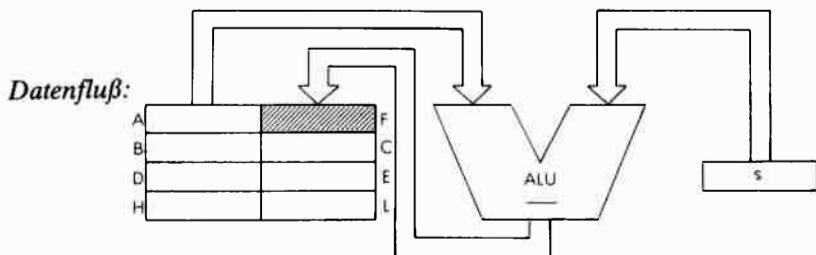

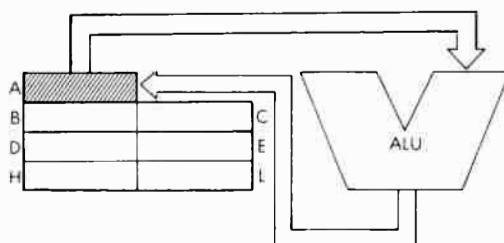

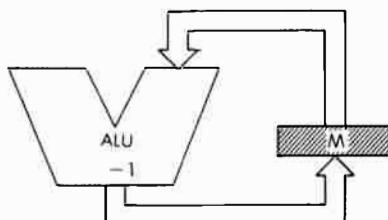

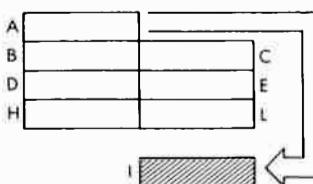

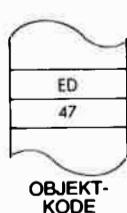

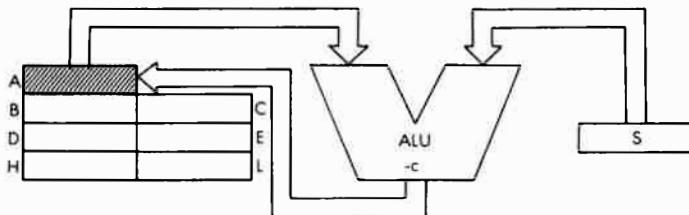

| Abb. 2.9:  | Ausführung einer Addition – R0 in den Akku . . . . .           | 54 |

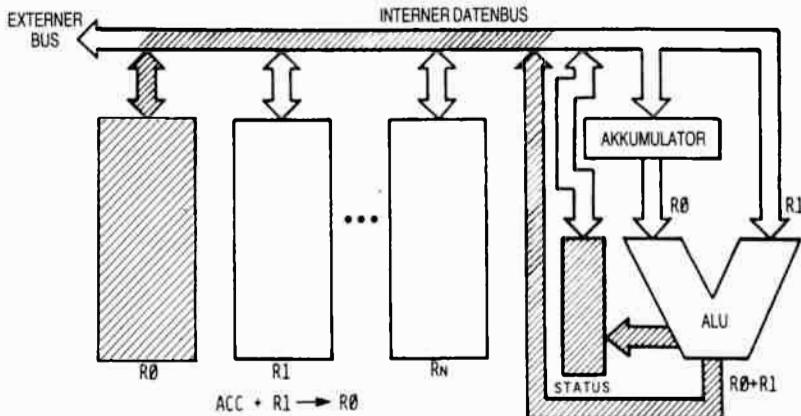

| Abb. 2.10: | Addition – Zweites Register R1 in die ALU . . . . .            | 54 |

| Abb. 2.11: | Das Ergebnis wird erzeugt und kommt nach R0 . . . . .          | 55 |

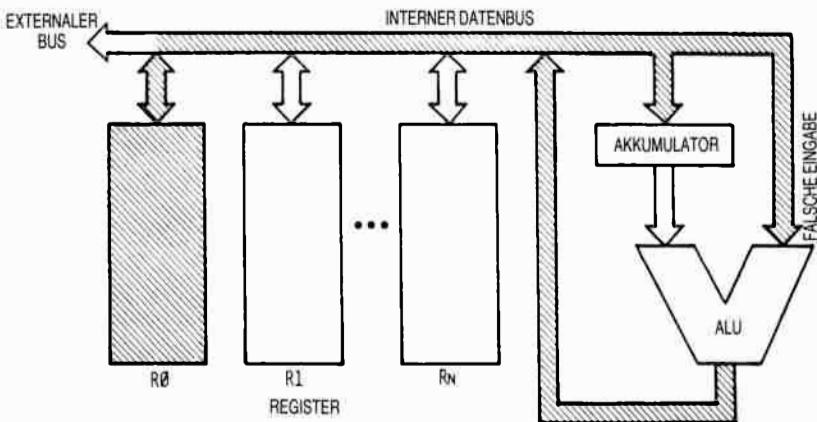

| Abb. 2.12: | Der kritische Wettlauf . . . . .                               | 56 |

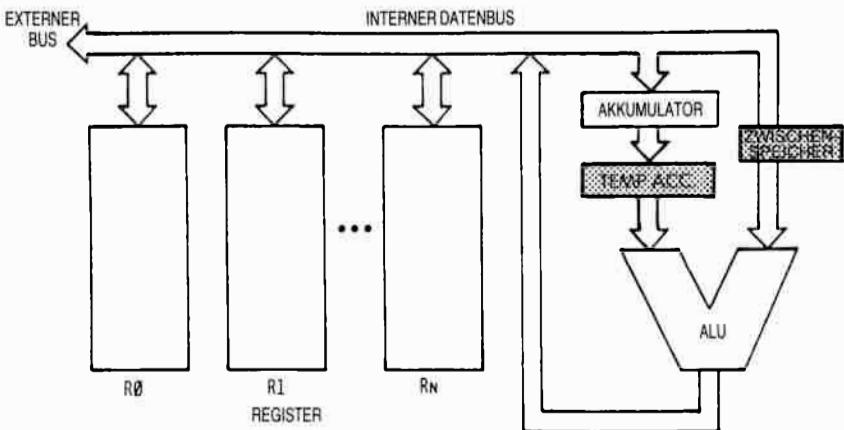

| Abb. 2.13: | Zwei Puffer werden benötigt . . . . .                          | 56 |

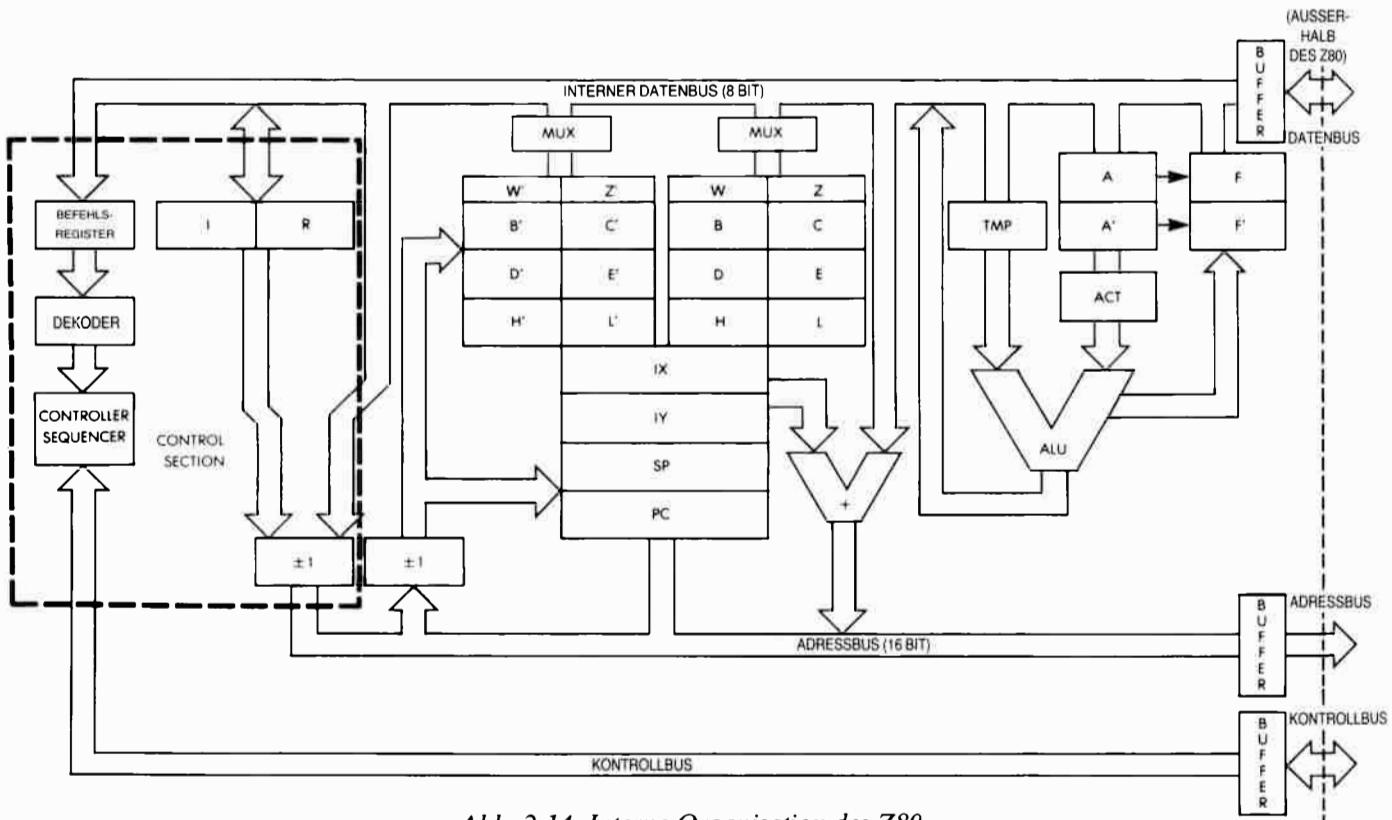

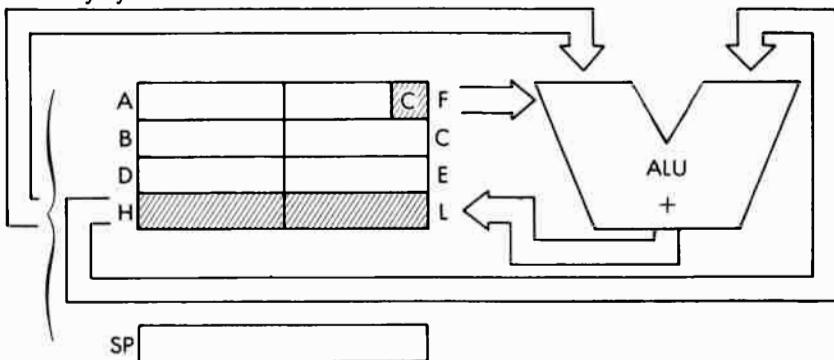

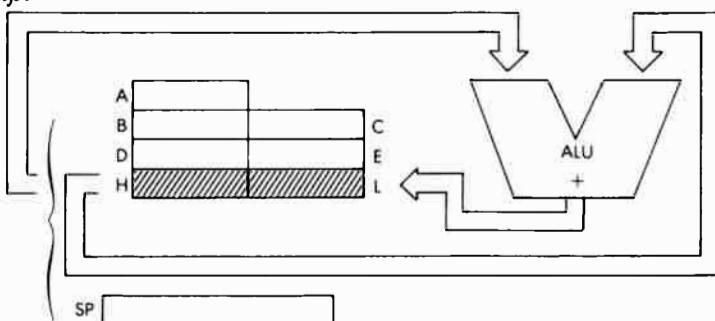

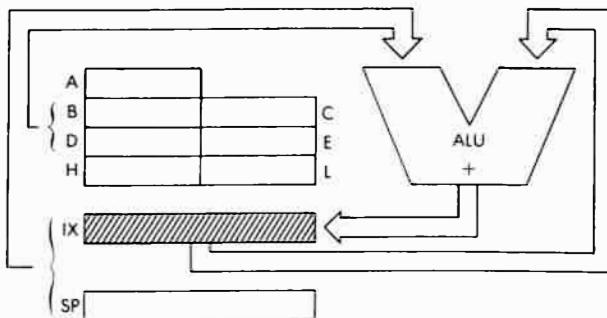

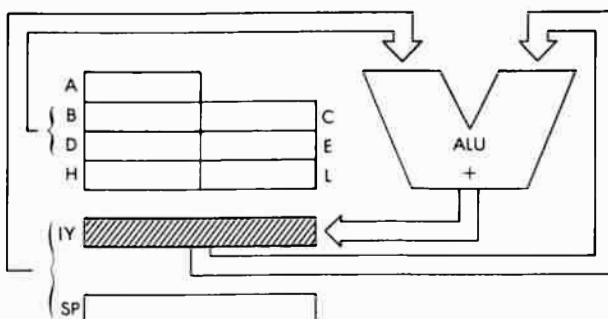

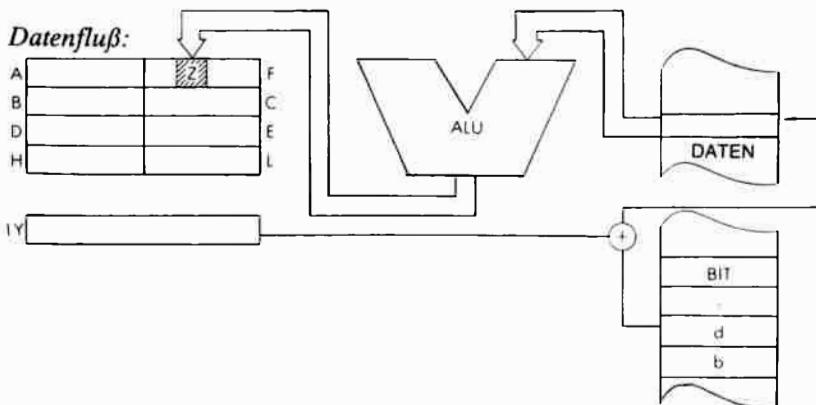

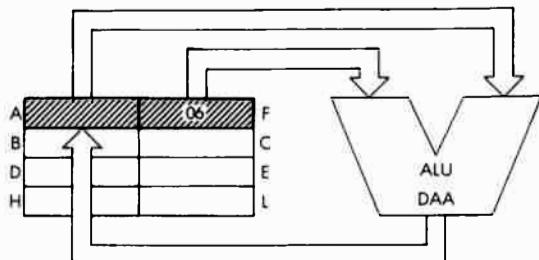

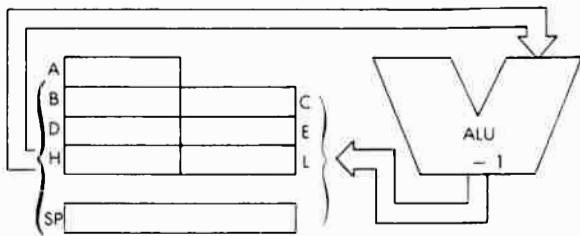

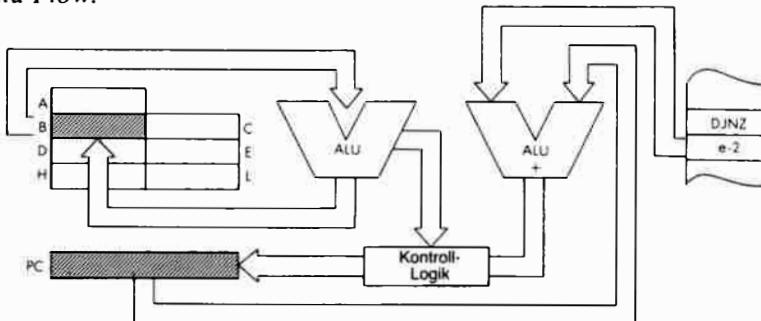

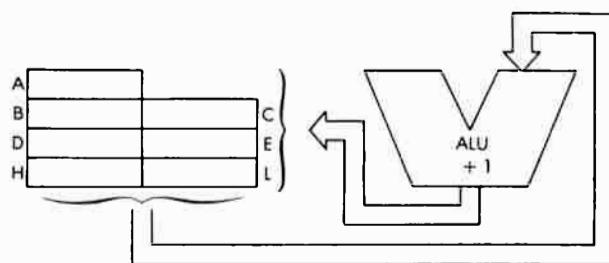

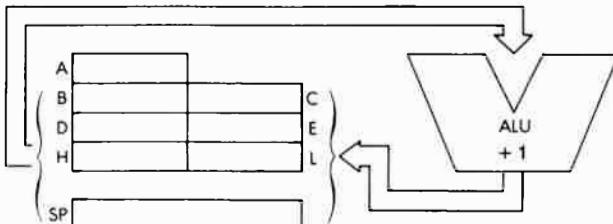

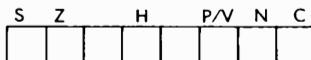

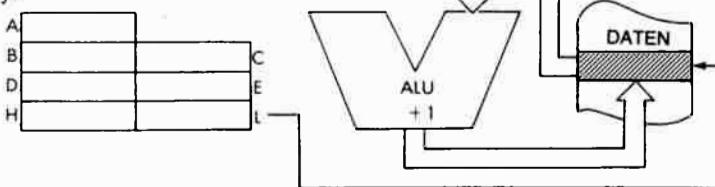

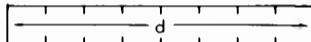

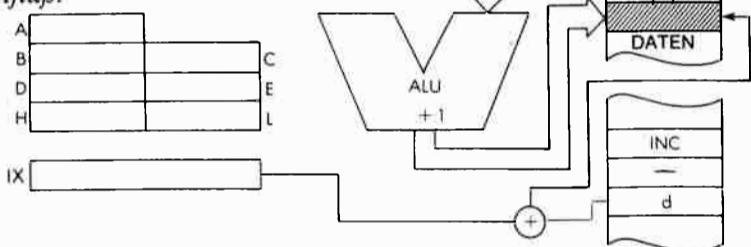

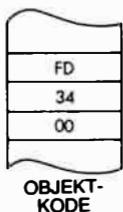

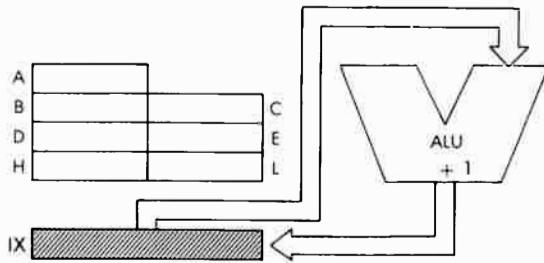

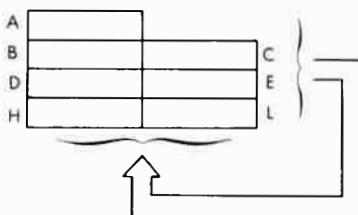

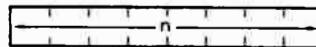

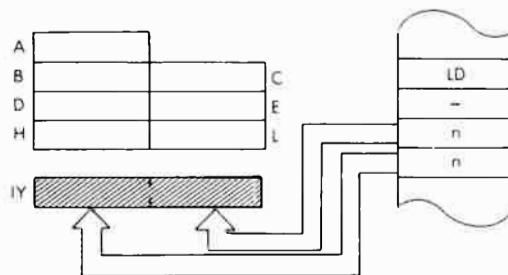

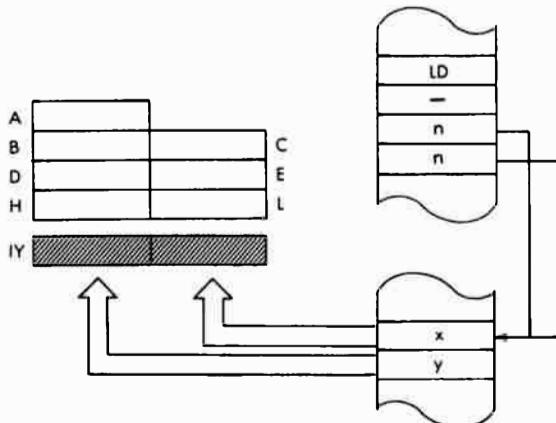

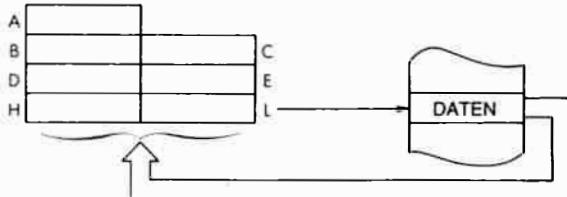

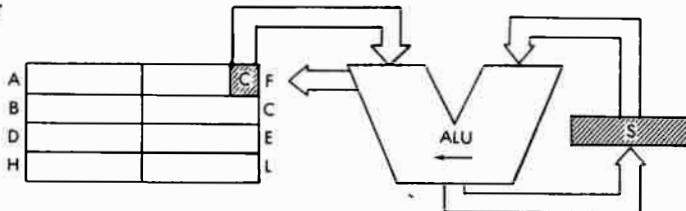

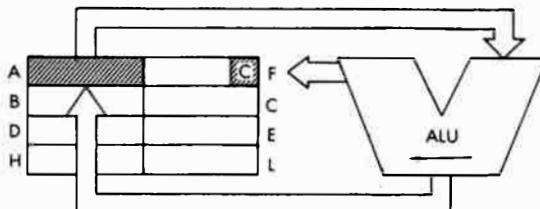

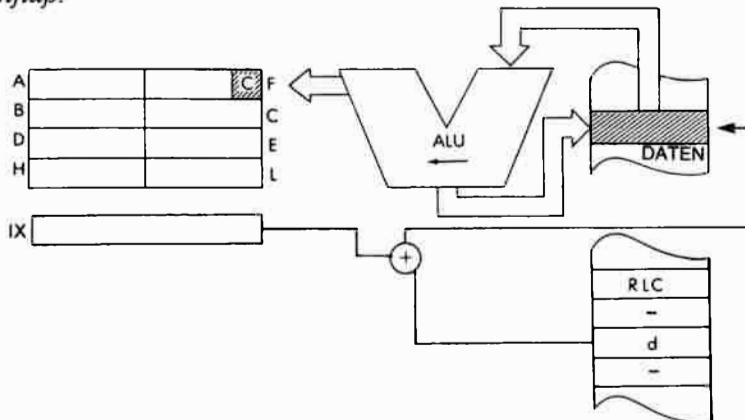

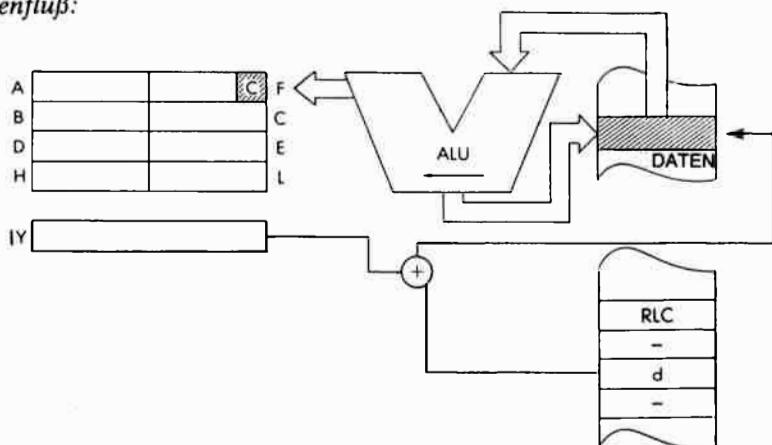

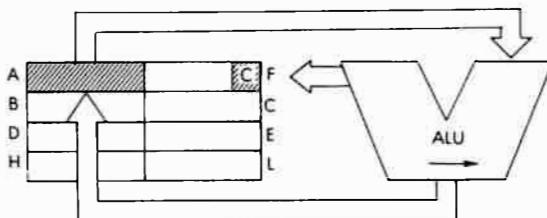

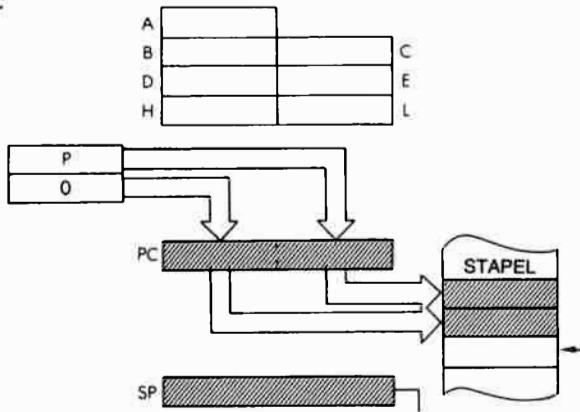

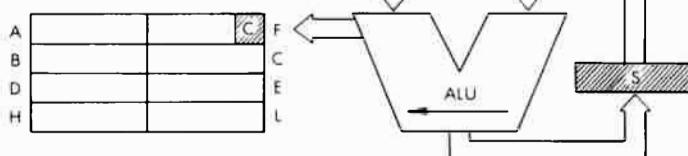

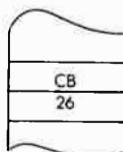

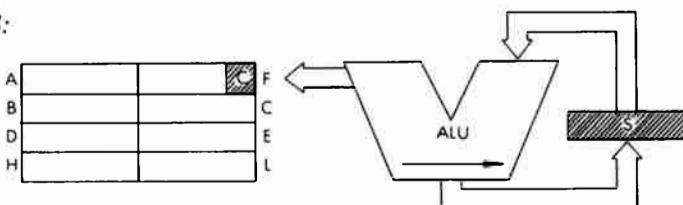

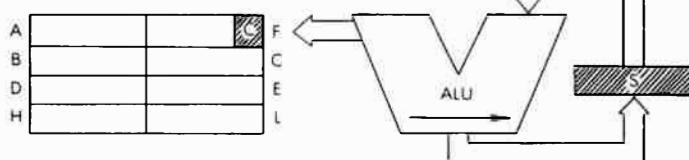

| Abb. 2.14: | Interne Organisation des Z80 . . . . .                         | 61 |

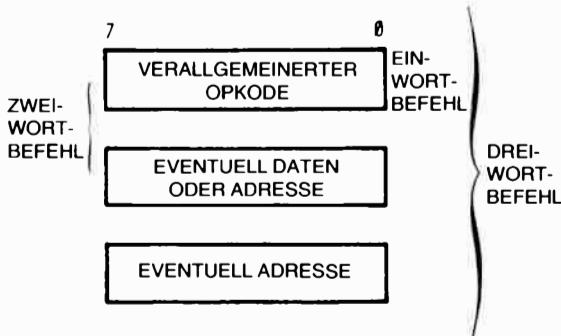

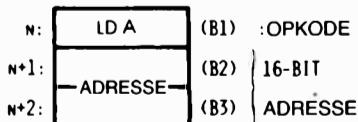

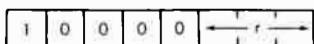

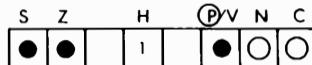

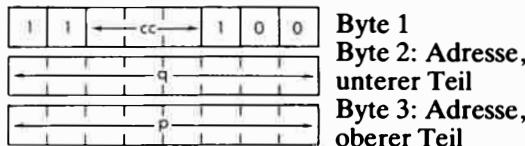

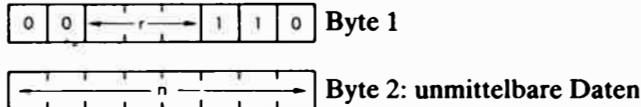

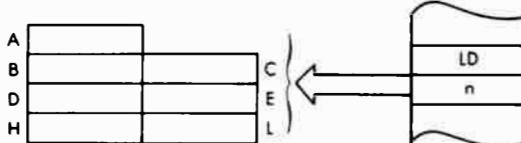

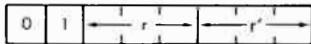

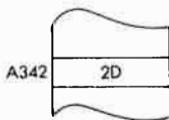

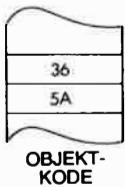

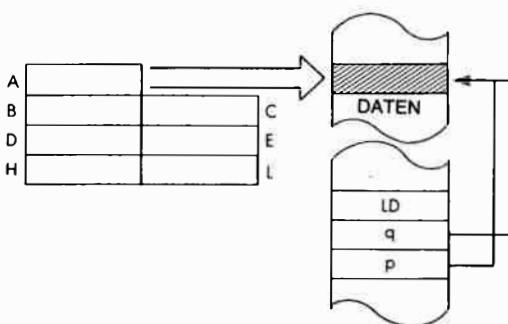

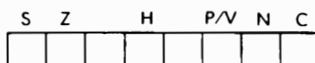

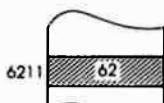

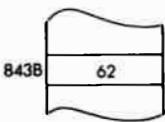

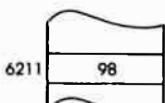

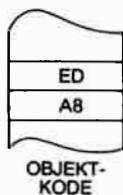

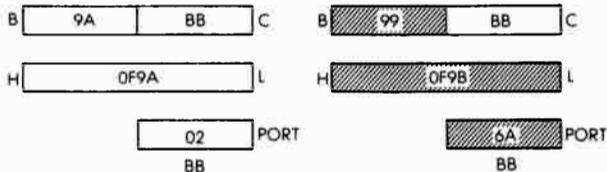

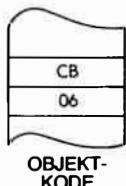

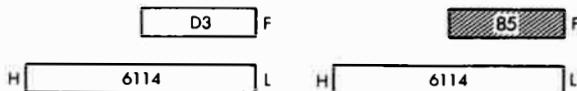

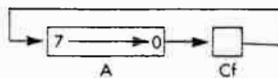

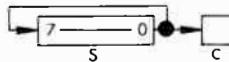

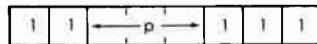

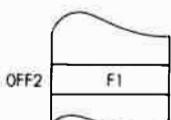

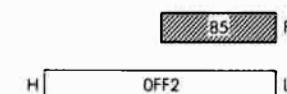

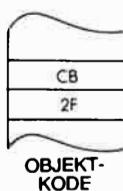

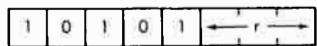

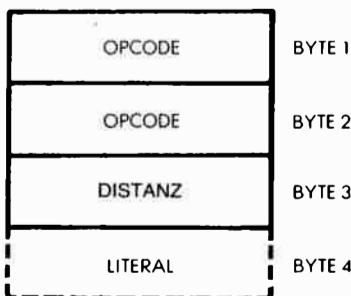

| Abb. 2.15: | Typisches Befehlsformat . . . . .                              | 63 |

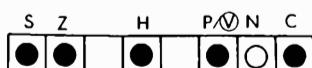

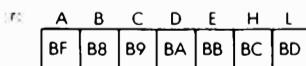

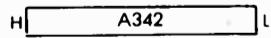

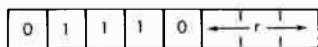

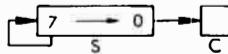

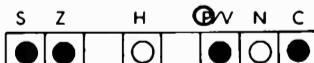

| Abb. 2.16: | Die Kodes der Register . . . . .                               | 64 |

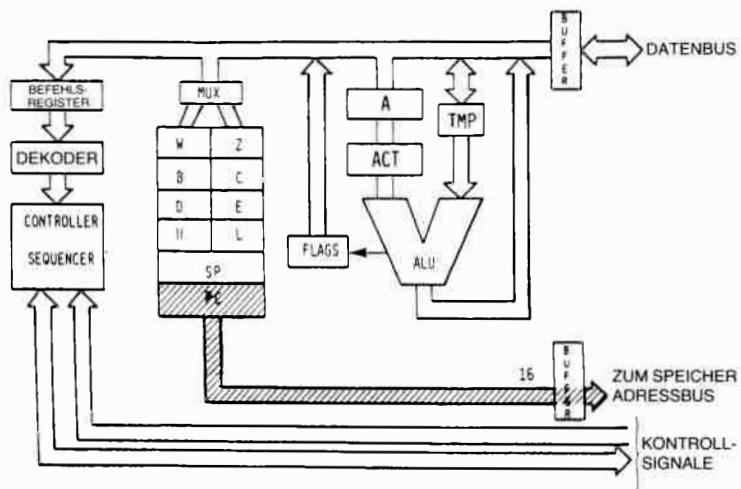

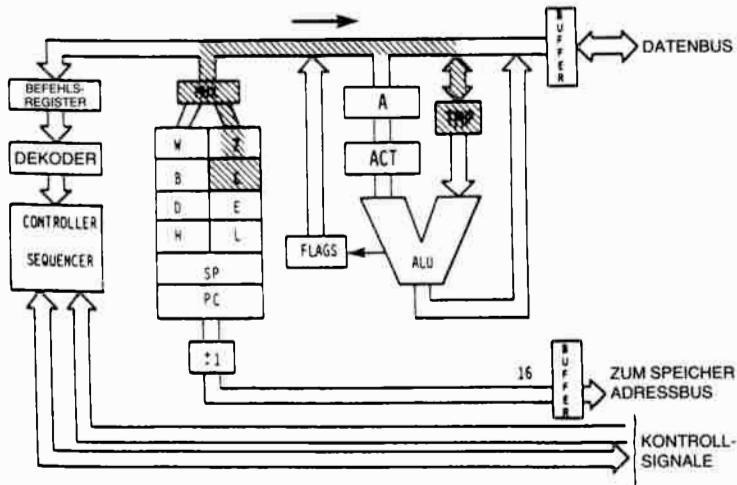

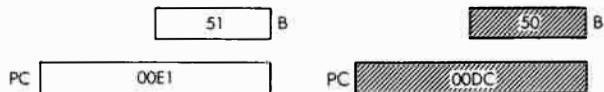

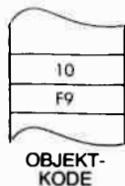

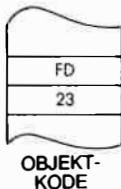

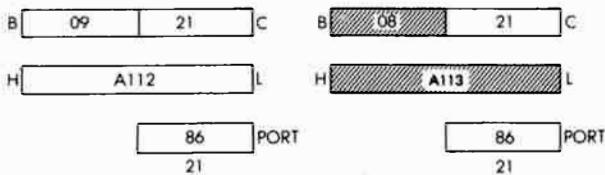

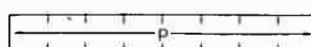

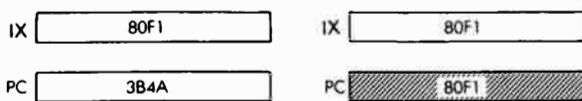

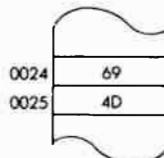

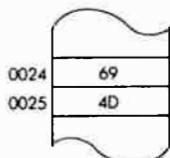

| Abb. 2.17: | Instruction Fetch – (PC) wird zum Speicher geschickt . . . . . | 66 |

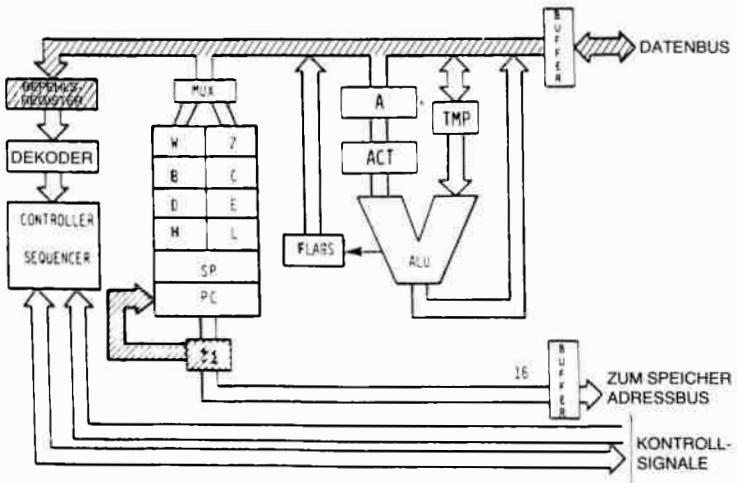

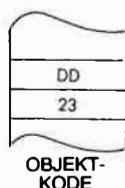

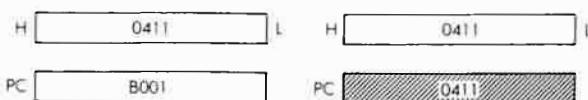

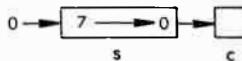

| A b. 2.18: | PC wird inkrementiert . . . . .                                | 66 |

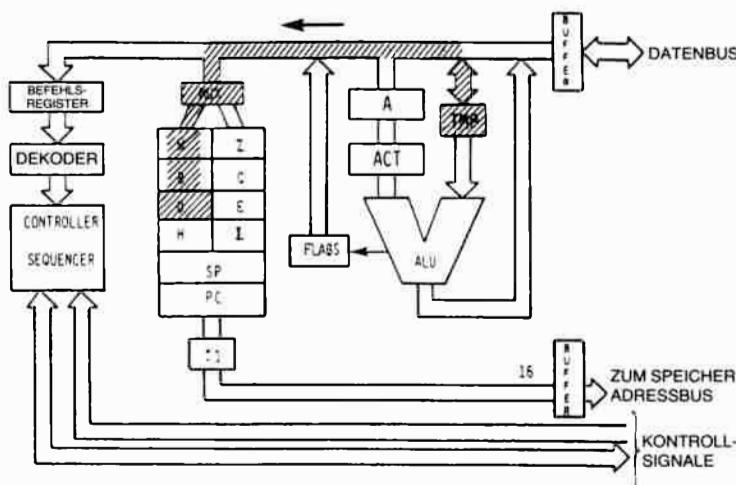

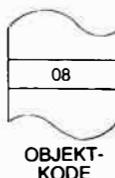

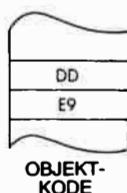

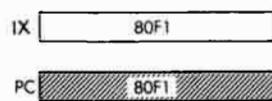

| Abb. 2.19: | Der Befehl kommt aus dem Speicher ins IR . . . . .             | 67 |

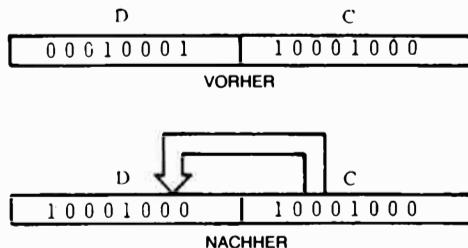

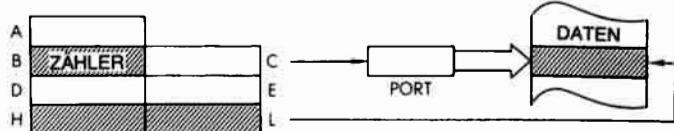

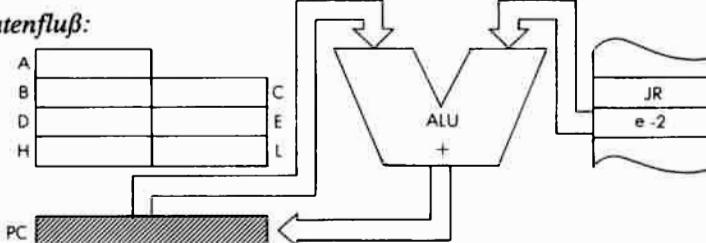

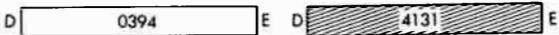

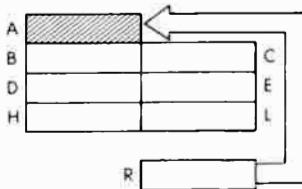

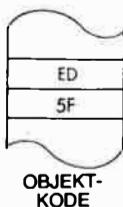

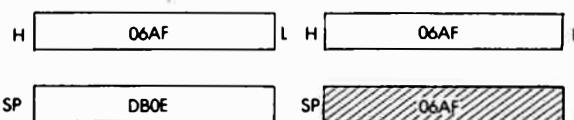

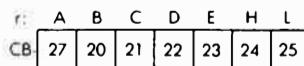

| Abb. 2.20: | Übertragung von C nach D . . . . .                             | 68 |

| Abb. 2.21: | Der Inhalt von C wird ins TMP abgelegt . . . . .               | 68 |

| Abb. 2.22: | Der Inhalt von TMP wird nach D übertragen . . . . .            | 69 |

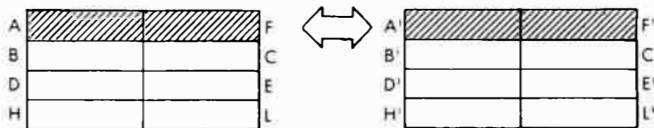

| Abb. 2.23: | Zwei Transfers werden gleichzeitig ausgeführt . . . . .        | 71 |

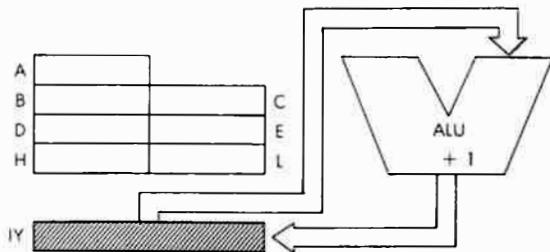

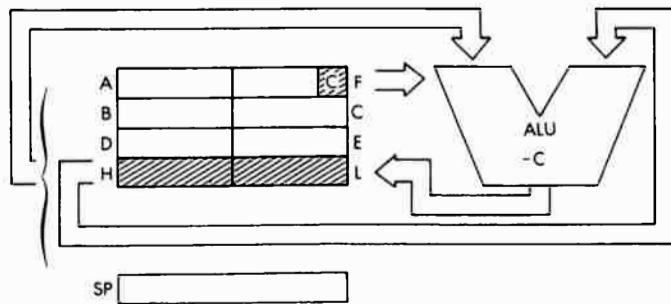

| Abb. 2.24: | Das Ende von ADD . . . . .                                     | 72 |

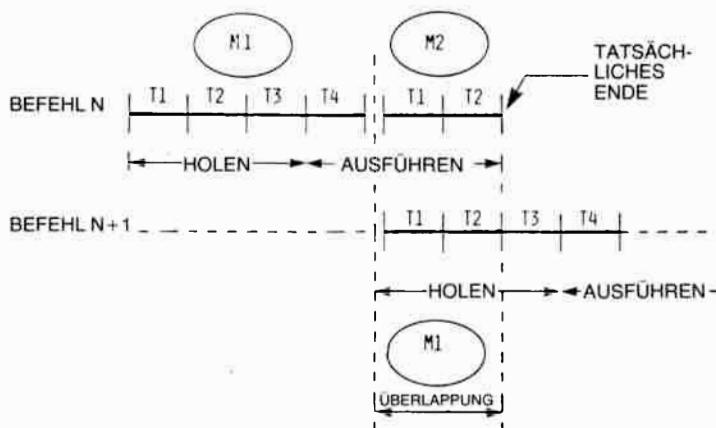

| Abb. 2.25: | Fetch-Execute-Überlappung während T1–T2 . . . . .              | 73 |

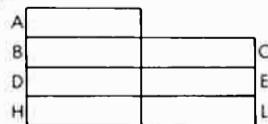

| Abb. 2.26: | Abkürzungen von INTEL . . . . .                                | 74 |

| Abb. 2.27: | Intel Befehlsformate . . . . .                                 | 76 |

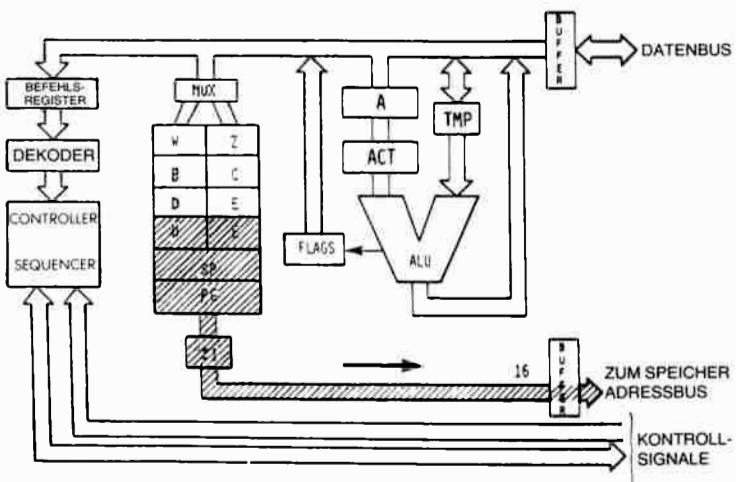

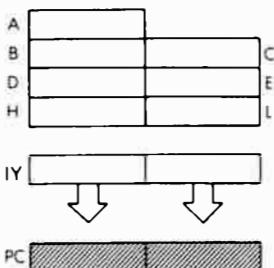

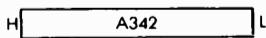

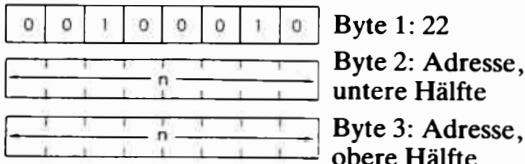

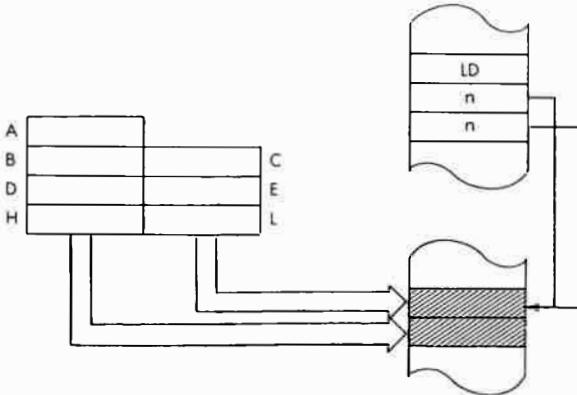

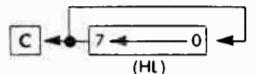

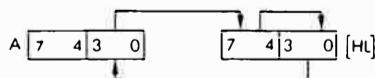

| Abb. 2.28: | Übertragung des Inhalts von HL zum Adreßbus . . . . .          | 80 |

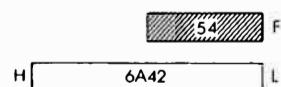

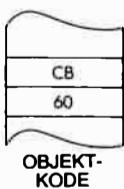

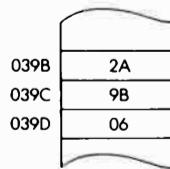

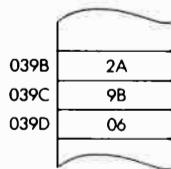

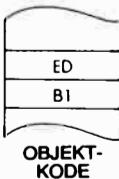

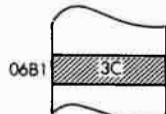

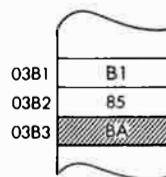

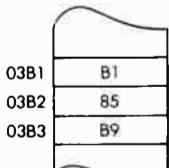

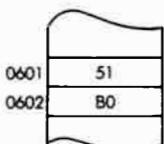

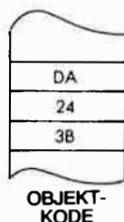

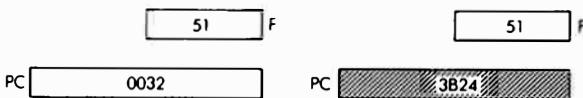

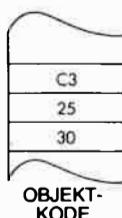

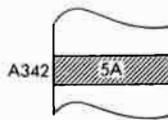

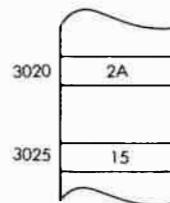

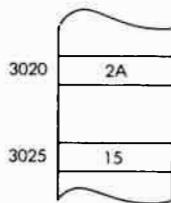

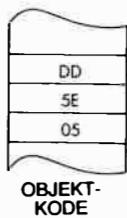

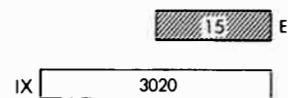

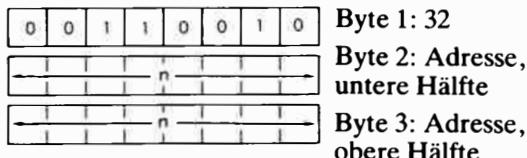

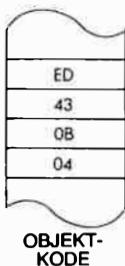

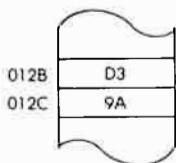

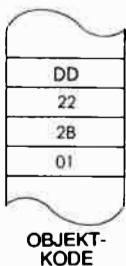

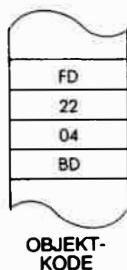

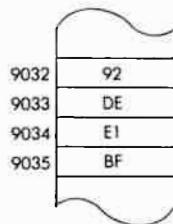

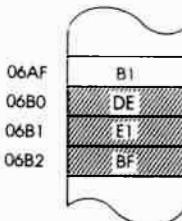

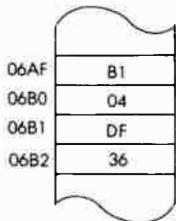

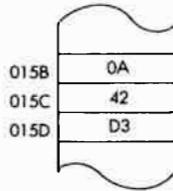

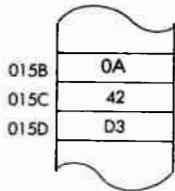

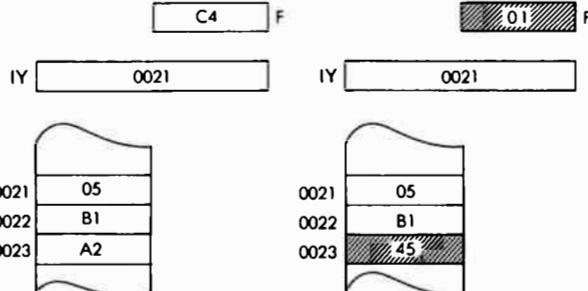

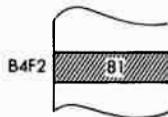

| Abb. 2.29: | LD A,(Adresse) ist ein Dreiwortbefehl . . . . .                | 81 |

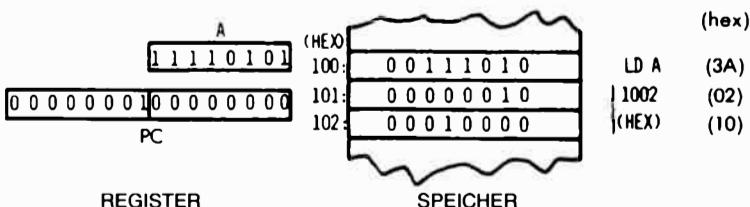

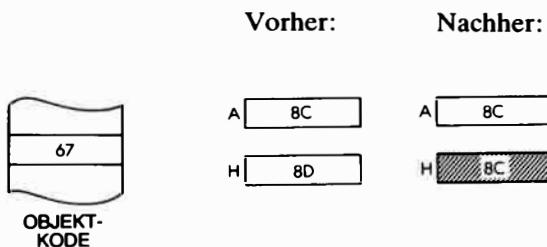

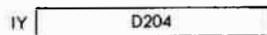

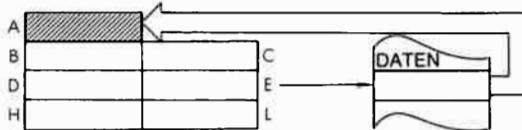

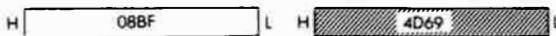

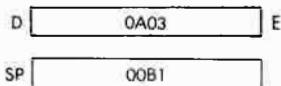

| Abb. 2.30: | Vor der Ausführung von LD A . . . . .                          | 81 |

| Abb. 2.31: | Nach der Ausführung von LD A . . . . .                         | 82 |

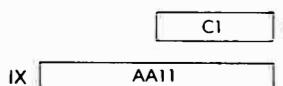

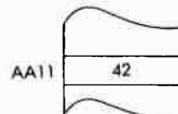

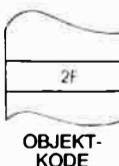

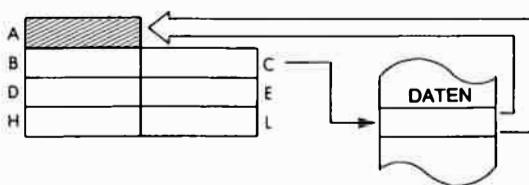

| Abb. 2.32: | Das zweite Byte des Befehls gelangt nach Z . . . . .           | 82 |

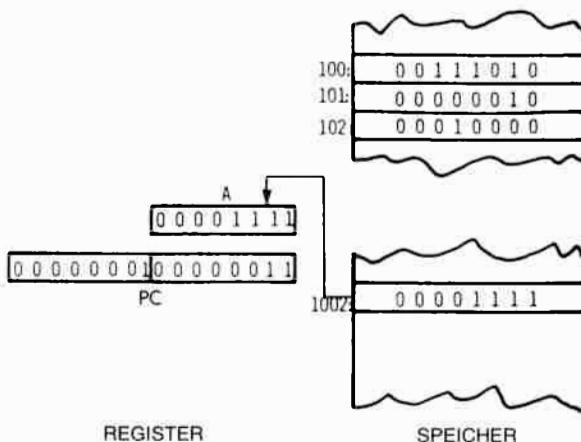

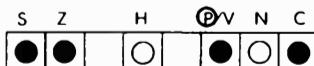

| Abb. 2.33: | Anschlußbelegung der Z80 MPU . . . . .                         | 85 |

|            |                                                                        |     |

|------------|------------------------------------------------------------------------|-----|

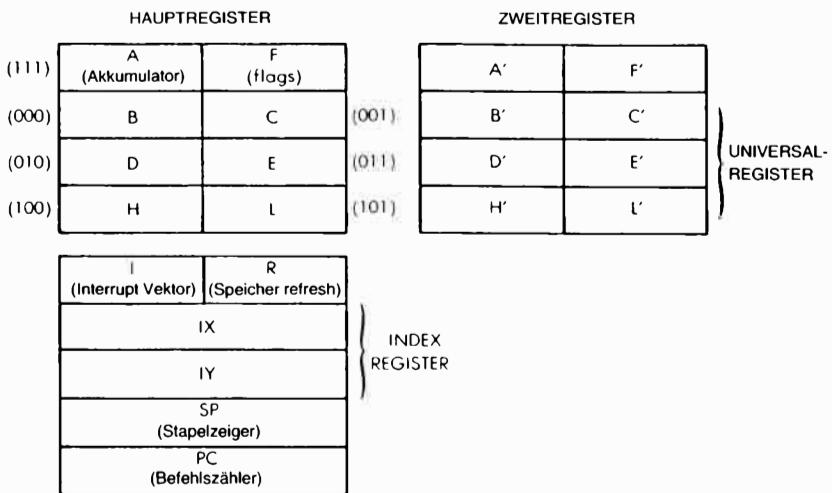

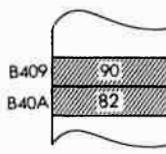

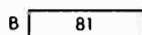

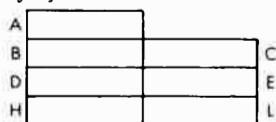

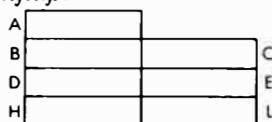

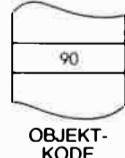

| Abb. 3.0:  | Die Register des Z80                                                   | 90  |

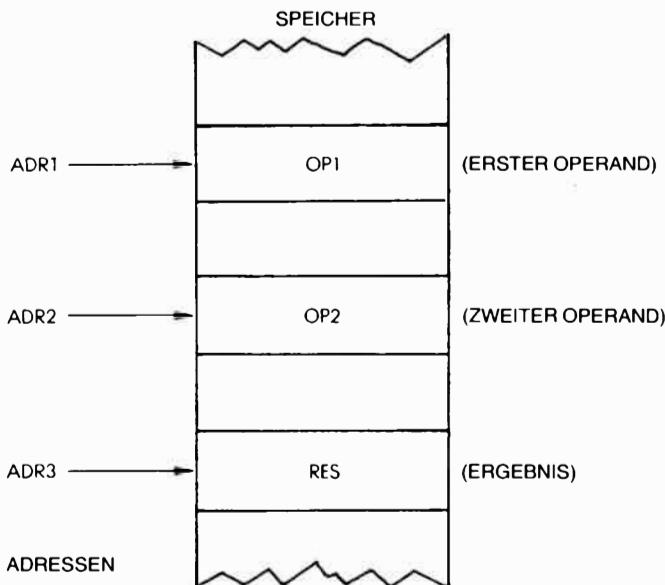

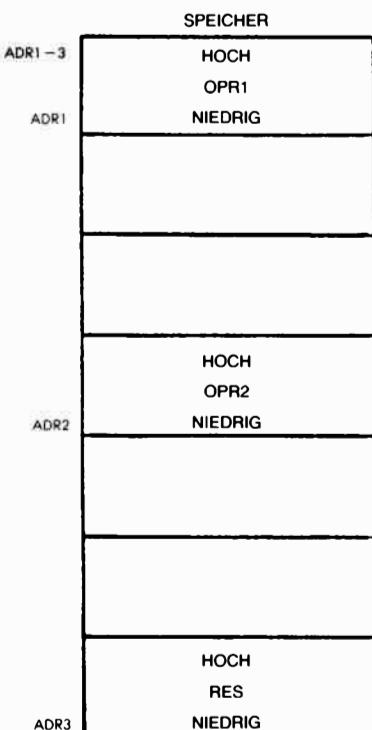

| Abb. 3.1:  | Acht-Bit-Addition RES = OP1 + OP2                                      | 91  |

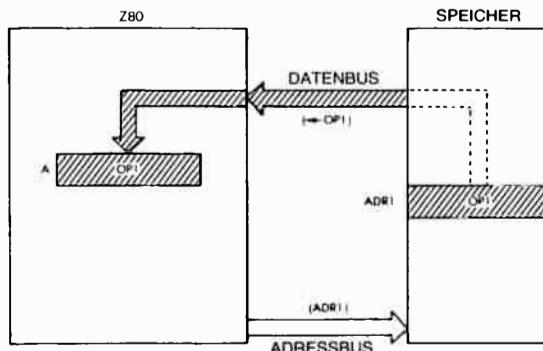

| Abb. 3.2:  | LD A,(ADR1): OP1 wird aus dem Speicher geladen                         | 92  |

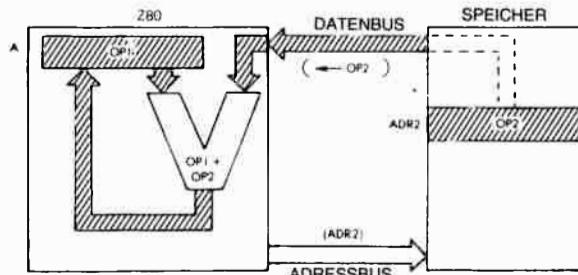

| Abb. 3.3:  | ADD A,(HL)                                                             | 92  |

| Abb. 3.4:  | LD (ADR3),A (Lege den Akkumulator im Speicher ab)                      | 93  |

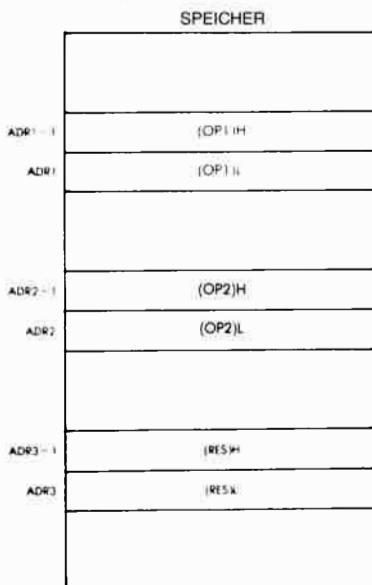

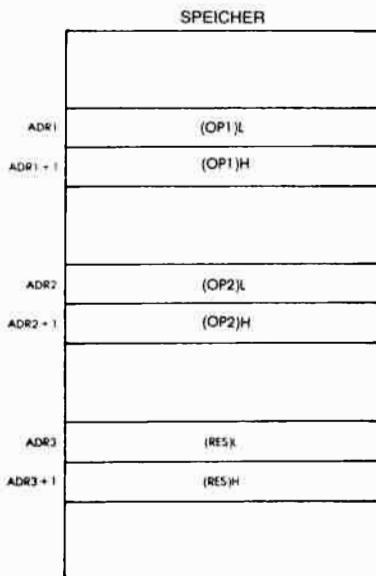

| Abb. 3.5:  | 16-Bit-Addition – die Operanden                                        | 94  |

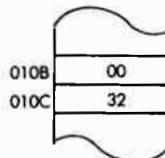

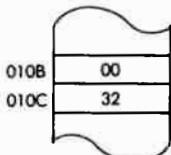

| Abb. 3.6:  | Speicherung der Operanden in umgekehrter Reihenfolge                   | 96  |

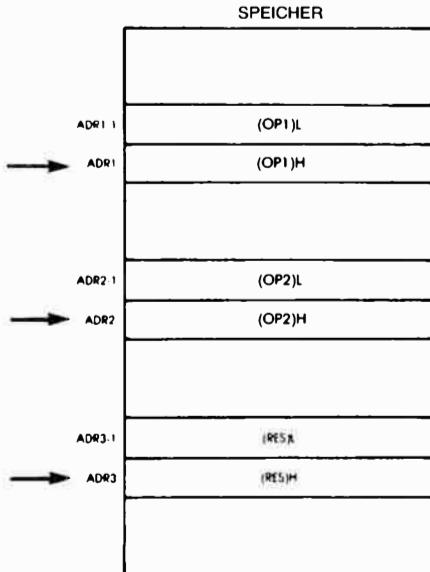

| Abb. 3.7:  | Zeiger auf das obere Byte                                              | 97  |

| Abb. 3.8:  | Eine 32-Bit-Addition                                                   | 98  |

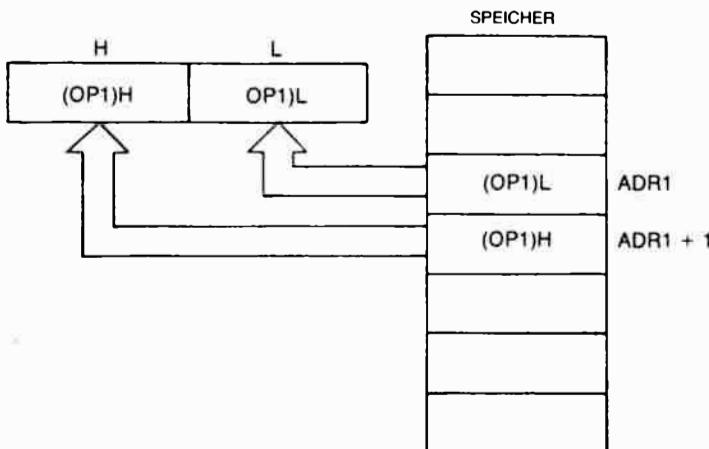

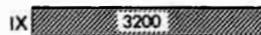

| Abb. 3.9:  | 16-Bit-Ladebefehl – LD HL,(ADR1)                                       | 99  |

| Abb. 3.10: | Speicherung von BCD-Ziffern                                            | 102 |

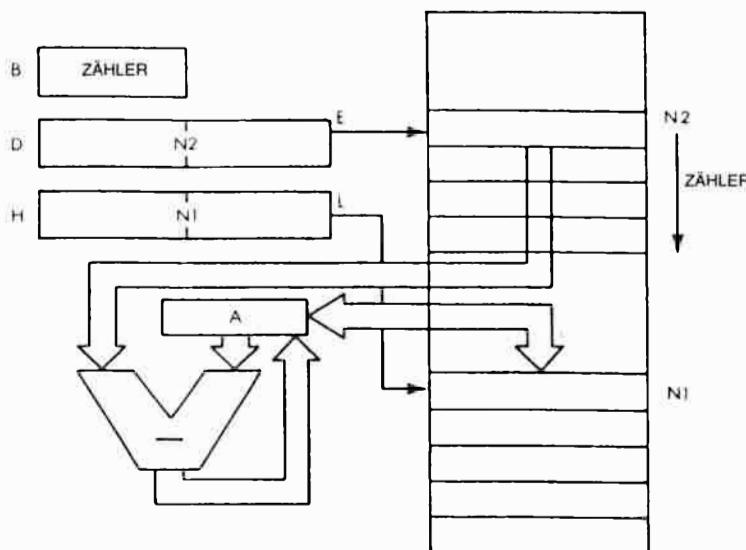

| Abb. 3.11: | Gepackte BCD-Subtraktion: N1←N2 – N1                                   | 105 |

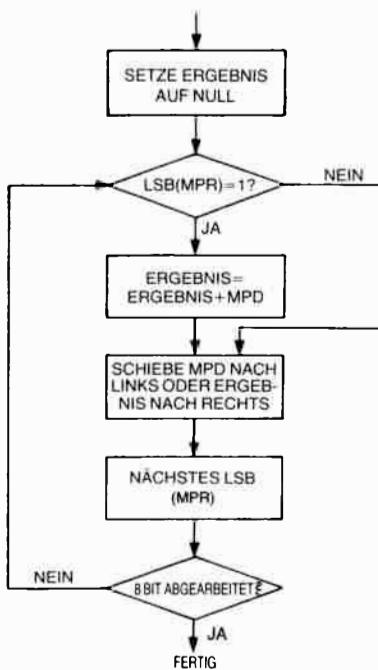

| Abb. 3.12: | Der grundlegende Algorithmus für die Multiplikation – ein Flußdiagramm | 107 |

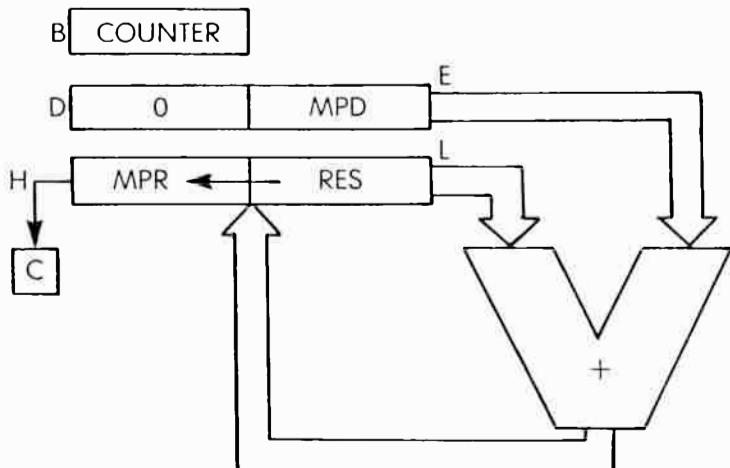

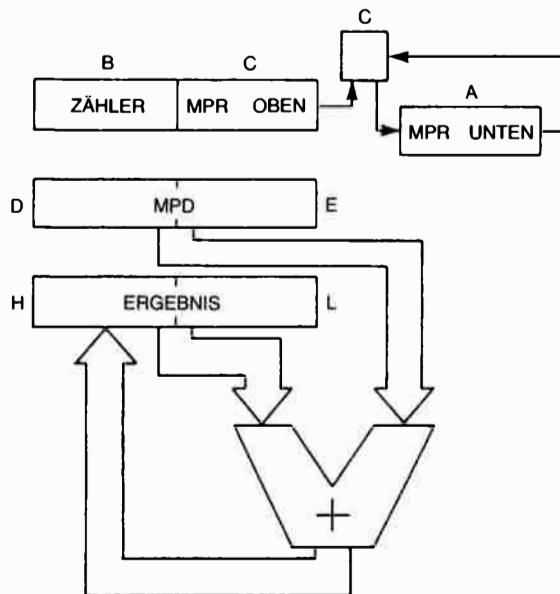

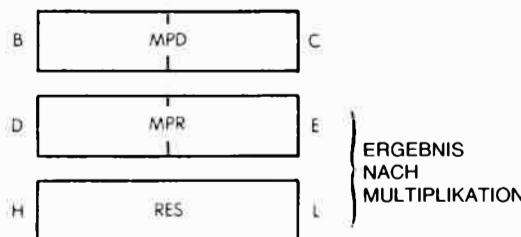

| Abb. 3.13: | 8 x 8 Bit Multiplikationsprogramm                                      | 108 |

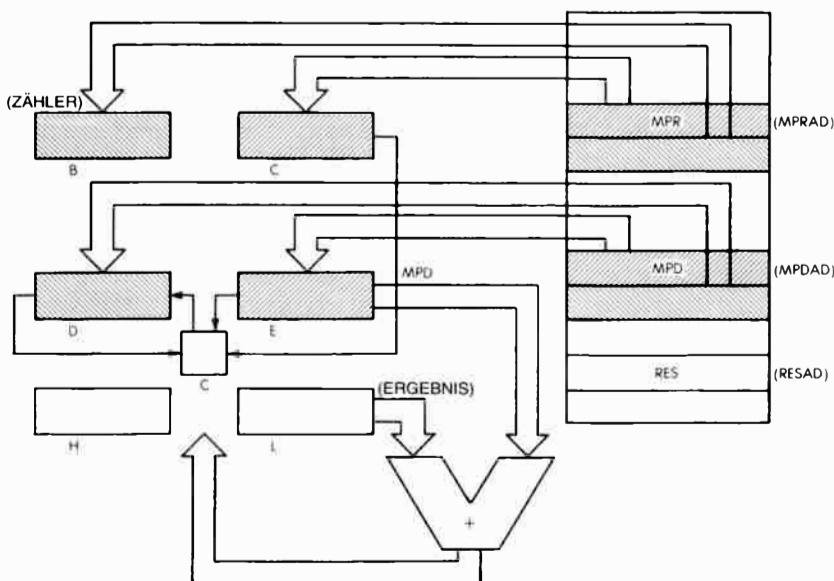

| Abb. 3.14: | 8 x 8 Bit Multiplikation – die Register                                | 109 |

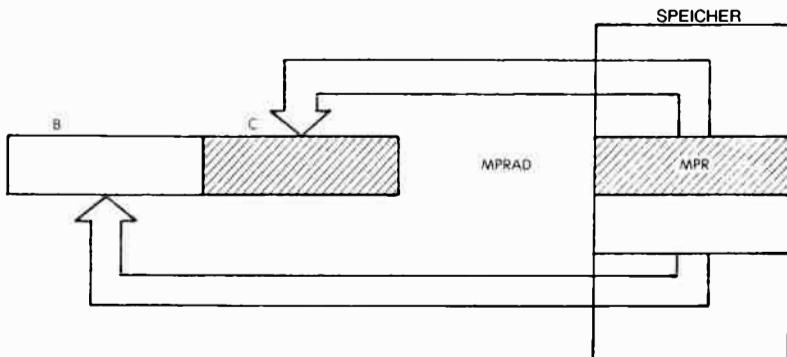

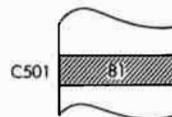

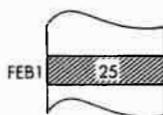

| Abb. 3.15: | LD BC,(MPRAD)                                                          | 110 |

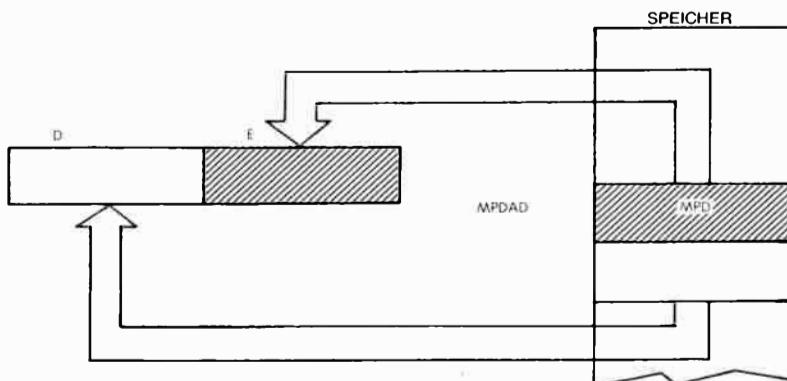

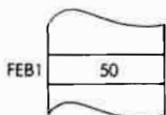

| Abb. 3.16: | LD DE,(MPDAD)                                                          | 111 |

| Abb. 3.17: | Schieben und Rotieren                                                  | 113 |

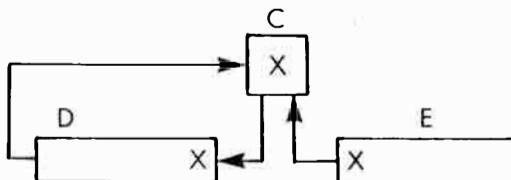

| Abb. 3.18: | Von E nach D Schieben                                                  | 114 |

| Abb. 3.19: | Tabelle zur Multiplikationsaufgabe                                     | 115 |

| Abb. 3.20: | Multiplikation: Nach dem ersten Befehl                                 | 116 |

| Abb. 3.21: | Multiplikation: Nach zwei Befehlen                                     | 117 |

| Abb. 3.22: | Multiplikation: Nach fünf Befehlen                                     | 117 |

| Abb. 3.23: | Ein Durchlauf durch die Schleife                                       | 118 |

| Abb. 3.24: | Verbesserte Multiplikation, Schritt 1                                  | 119 |

| Abb. 3.25: | Register zur verbesserten Multiplikation                               | 120 |

| Abb. 3.26: | Verbesserte Multiplikation, Schritt 2                                  | 121 |

| Abb. 3.27: | 16 x 16 Bit Multiplikation – die Register                              | 122 |

| Abb. 3.28: | 16 x 16 Bit Multiplikationsprogramm                                    | 123 |

| Abb. 3.29: | 16 x 16 Bit Multiplikation mit 32-Bit-Ergebnis                         | 125 |

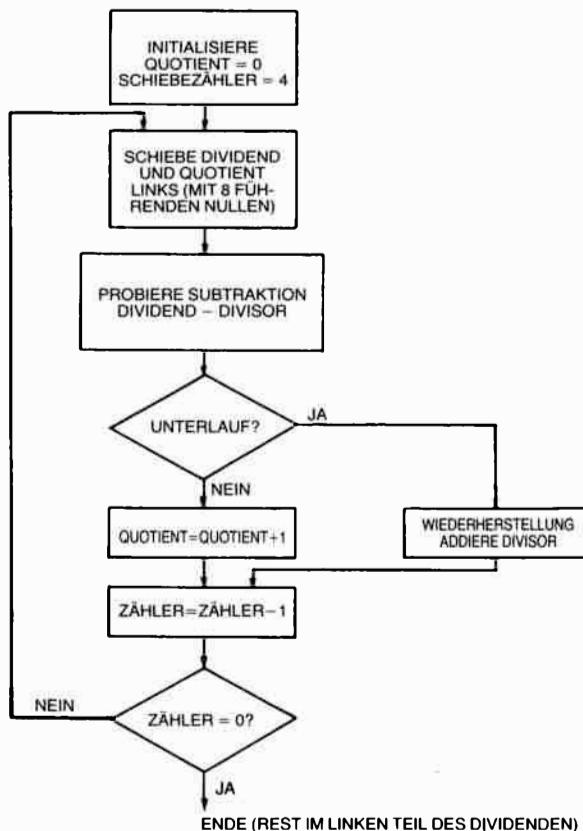

| Abb. 3.30: | Flußdiagramm für duale 8-Bit-Division                                  | 126 |

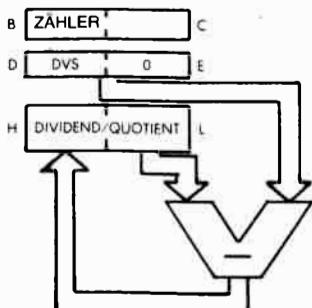

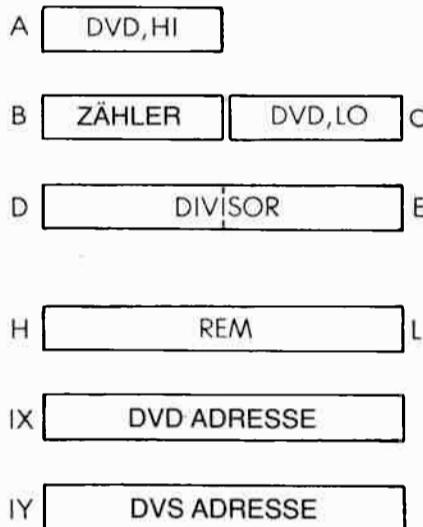

| Abb. 3.31: | 16 / 8 Bit Division – die Register                                     | 126 |

| Abb. 3.32: | 16 / 8 Bit Divisionsprogramm                                           | 127 |

| Abb. 3.33: | Formular für das Divisionsprogramm                                     | 129 |

| Abb. 3.34: | Nicht-wiederherstellende Division – die Register                       | 130 |

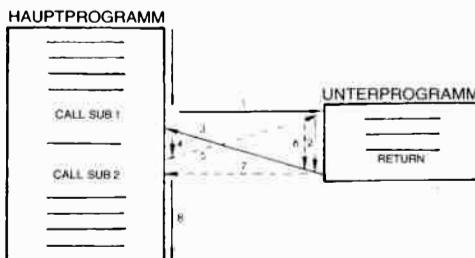

| Abb. 3.35: | Unterprogrammaufrufe                                                   | 135 |

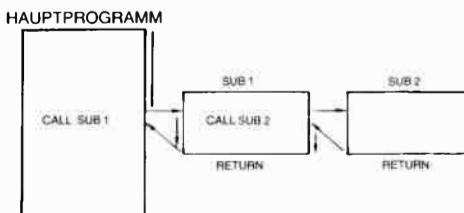

| Abb. 3.36: | Verschachtelte Aufrufe                                                 | 137 |

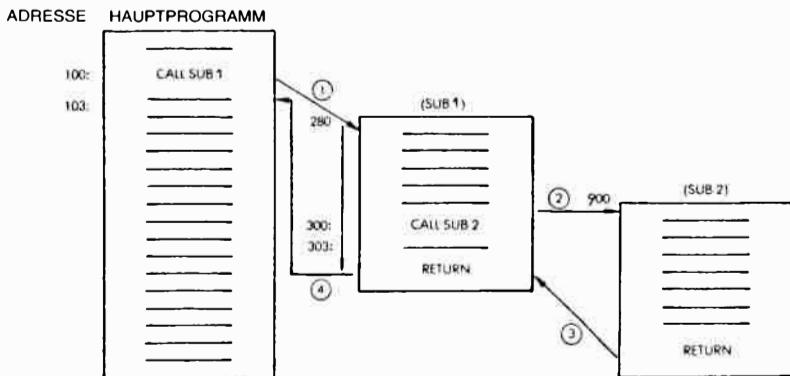

| Abb. 3.37: | Die Unterprogrammaufrufe                                               | 138 |

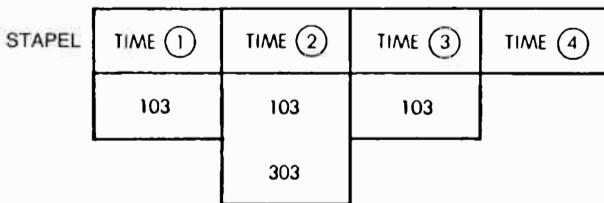

| Abb. 3.38: | Der Stapel zu verschiedenen Zeitpunkten                                | 138 |

| Abb. 3.39: | Multiplikation: eine vollständige Aufzeichnung                         | 143 |

| Abb. 3.40: | Das Multiplikationsprogramm (hexadezimal)                              | 145 |

| Abb. 3.41: | Zwei Durchläufe durch die Schleife                                     | 145 |

| Abb. 4.1:  | Schieben und Rotieren                                                  | 148 |

---

|             |                                                                                 |     |

|-------------|---------------------------------------------------------------------------------|-----|

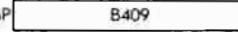

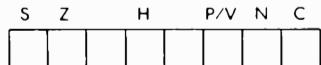

| Abb. 4.2:   | Acht-Bit-Ladebefehle – LD . . . . .                                             | 152 |

| Abb. 4.3:   | 16-Bit-Ladebefehle – 'LD', 'PUSH' und 'POP' . . . . .                           | 153 |

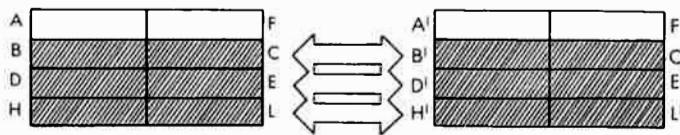

| Abb. 4.4:   | Austausch 'EX' und 'EXX' . . . . .                                              | 154 |

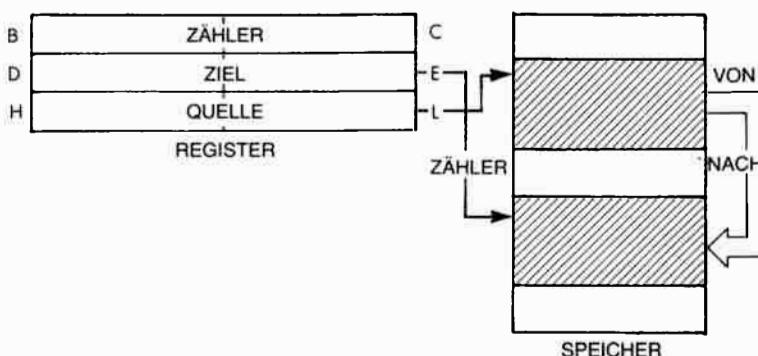

| Abb. 4.5:   | Blocktransferbefehle . . . . .                                                  | 155 |

| Abb. 4.6:   | Blocksuchbefehle . . . . .                                                      | 156 |

| Abb. 4.7:   | Acht-Bit Arithmetik und Logik . . . . .                                         | 157 |

| Abb. 4.8:   | 16-Bit Arithmetik und Logik . . . . .                                           | 158 |

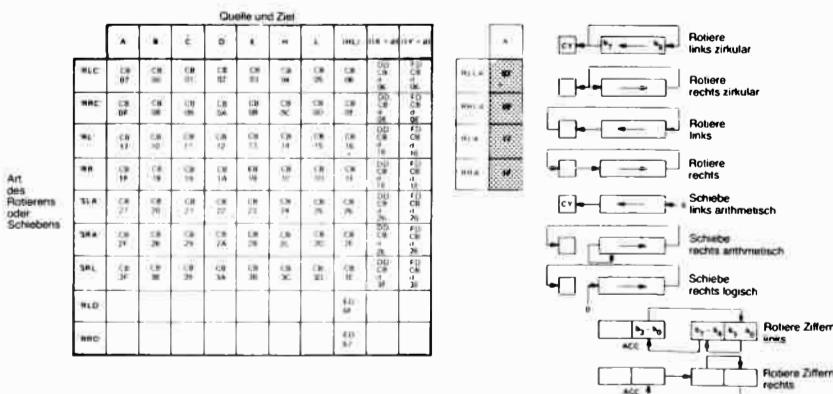

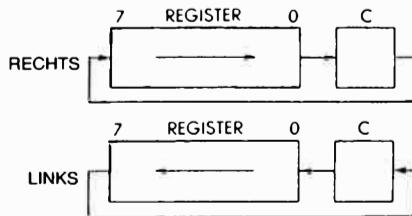

| Abb. 4.9:   | Schieben und Rotieren . . . . .                                                 | 161 |

| Abb. 4.10:  | Rotieren und Schieben . . . . .                                                 | 161 |

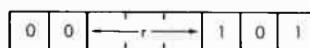

| Abb. 4.11:  | Neun-Bit-Rotation . . . . .                                                     | 162 |

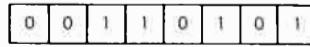

| Abb. 4.12:  | Acht-Bit-Rotation . . . . .                                                     | 162 |

| Abb. 4.13:  | Rotieren von Ziffern . . . . .                                                  | 163 |

| Abb. 4.14:  | Bitmanipulationen . . . . .                                                     | 164 |

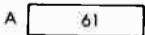

| Abb. 4.15:  | Universelle Operationen mit AF . . . . .                                        | 165 |

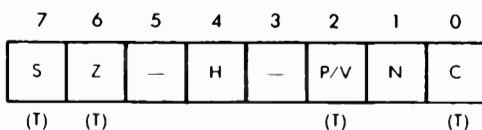

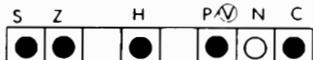

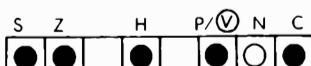

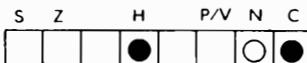

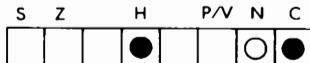

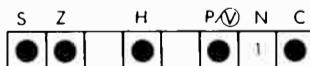

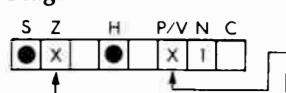

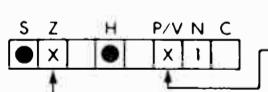

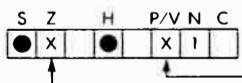

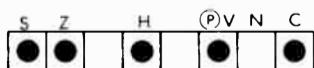

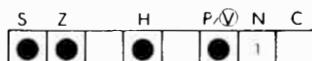

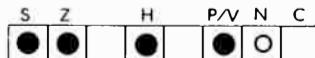

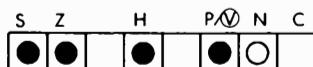

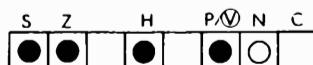

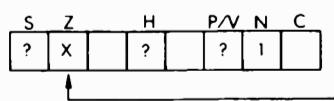

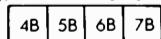

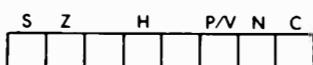

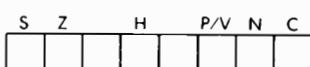

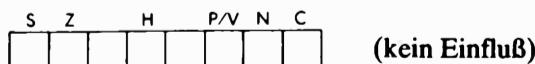

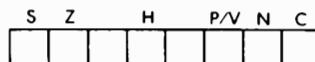

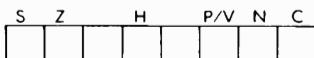

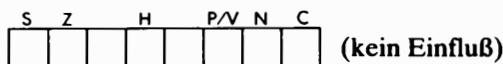

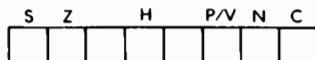

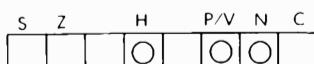

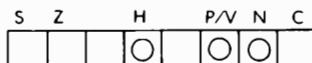

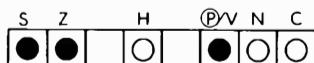

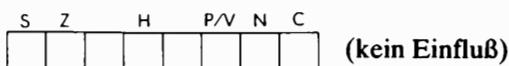

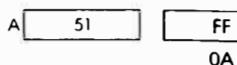

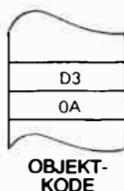

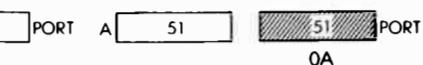

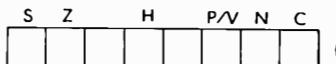

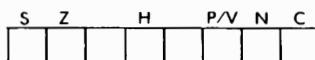

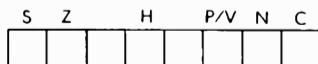

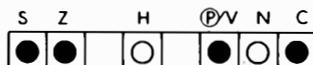

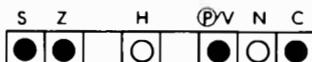

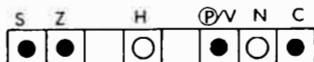

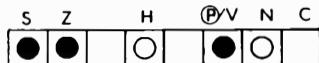

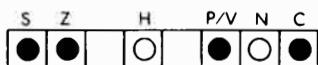

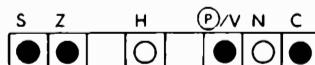

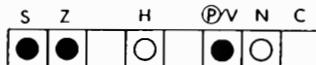

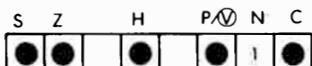

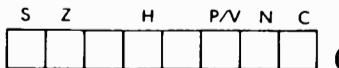

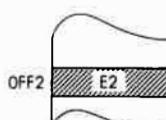

| Abb. 4.16:  | Das Flagregister . . . . .                                                      | 165 |

| Abb. 4.17:  | Zusammenfassung der Arbeitsweise der Flags . . . . .                            | 170 |

| Abb. 4.18:  | Sprungbefehle . . . . .                                                         | 172 |

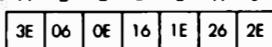

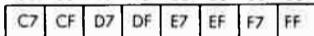

| Abb. 4.19:  | Restart-Befehle . . . . .                                                       | 173 |

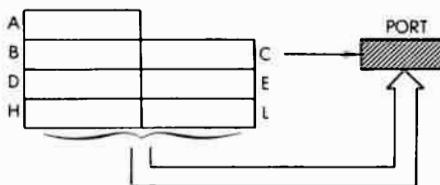

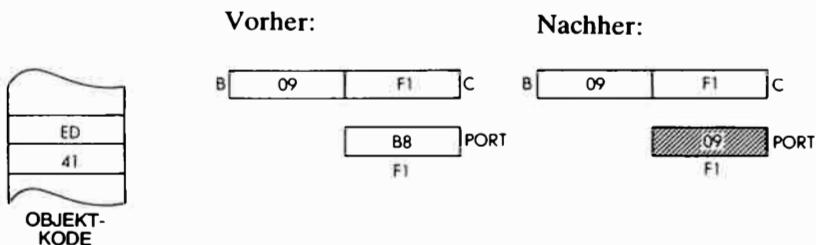

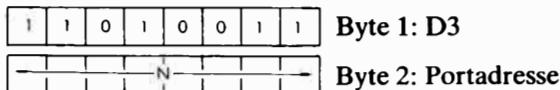

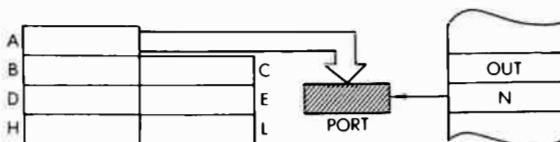

| Abb. 4.20:  | Die Ausgabebefehle . . . . .                                                    | 175 |

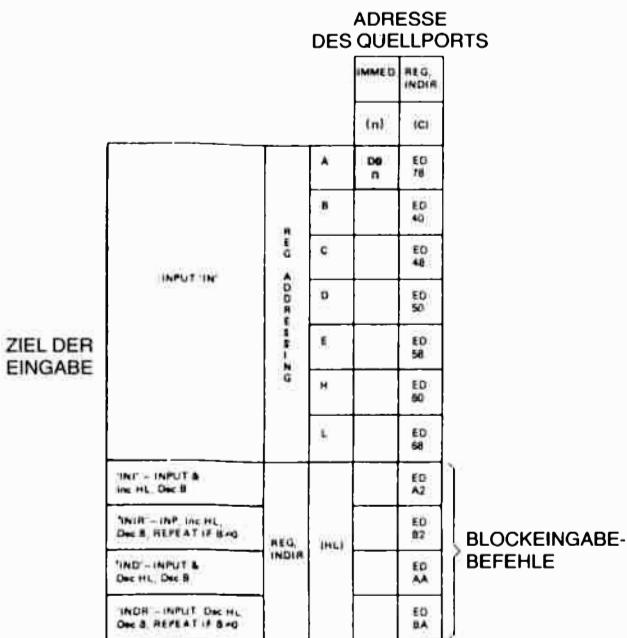

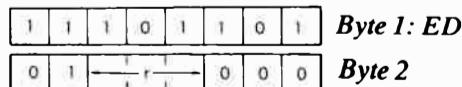

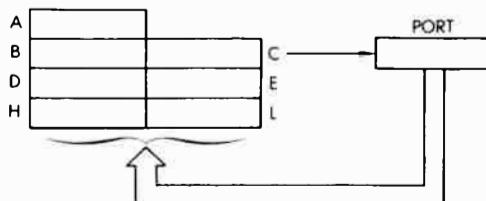

| Abb. 4.21:  | Die Eingabebefehle . . . . .                                                    | 176 |

| Abb. 4.22:  | Verschiedene CPU Steuerbefehle . . . . .                                        | 177 |

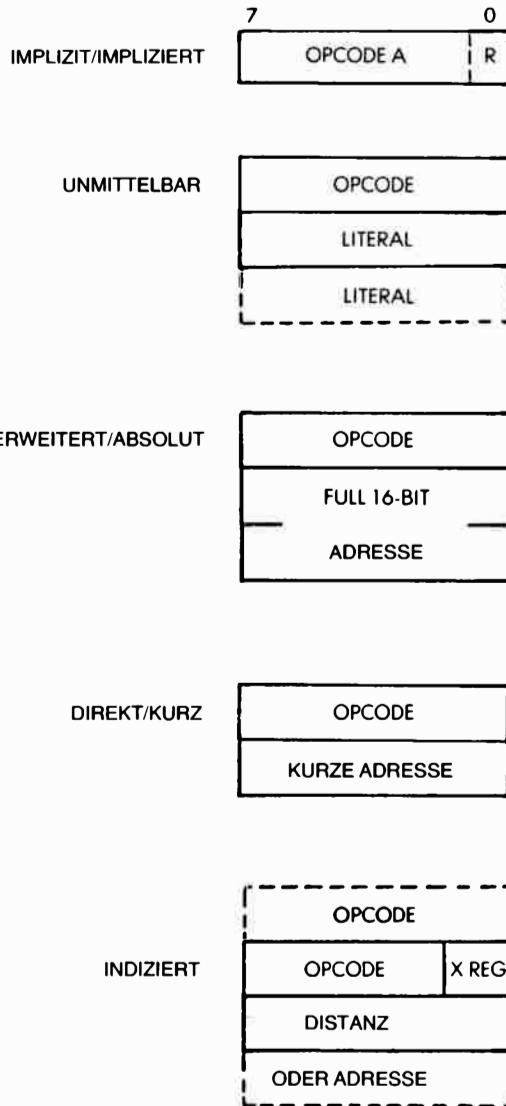

| Abb. 5.1:   | Grundlegende Adressierungsarten . . . . .                                       | 430 |

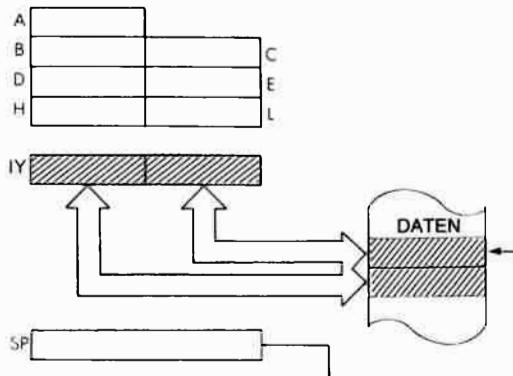

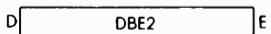

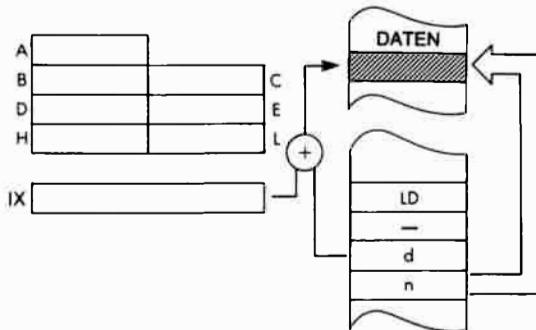

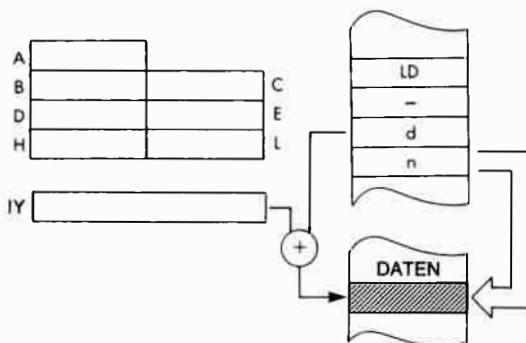

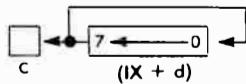

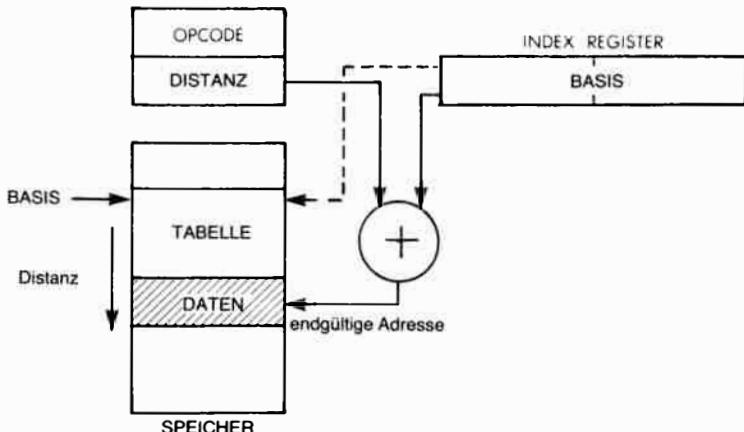

| Abb. 5.2:   | Adressierung (direkt indiziert) . . . . .                                       | 433 |

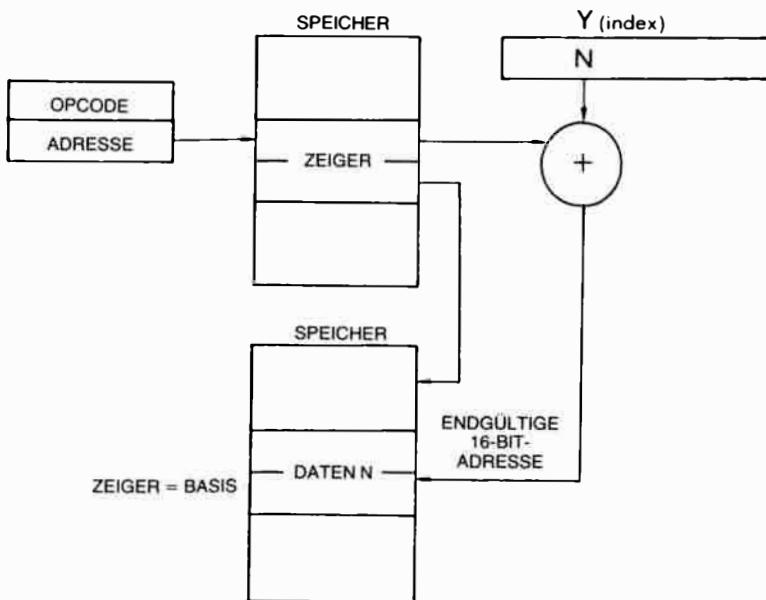

| Abb. 5.3:   | Indirekte indizierte Adressierung . . . . .                                     | 433 |

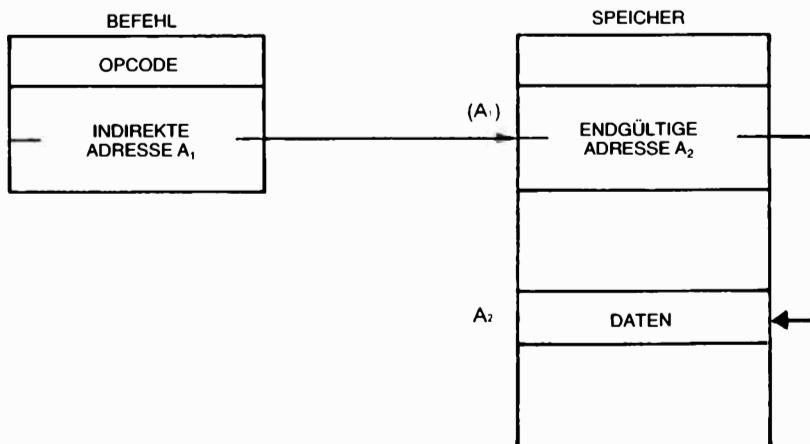

| Abb. 5.4:   | Indirekte Adressierung . . . . .                                                | 434 |

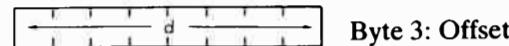

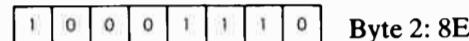

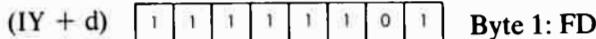

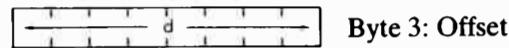

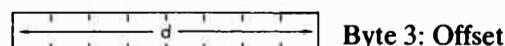

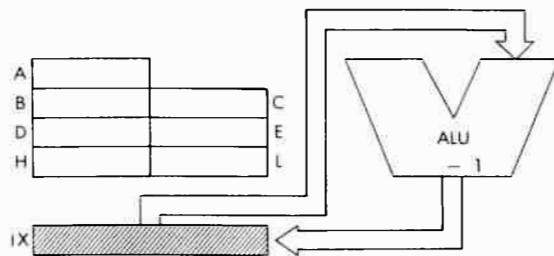

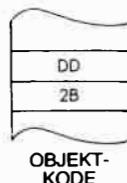

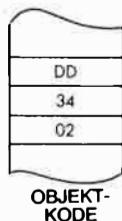

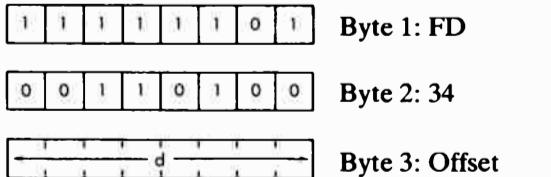

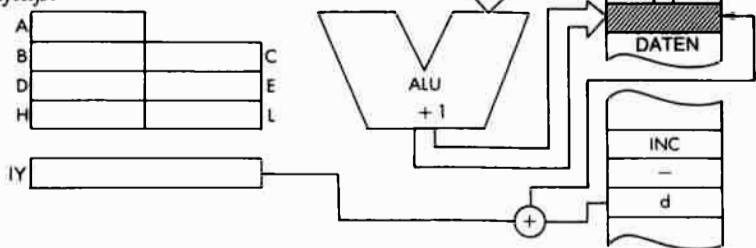

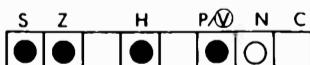

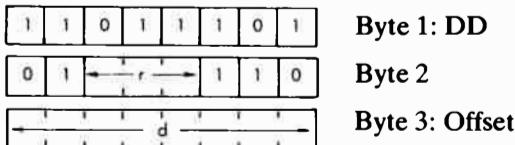

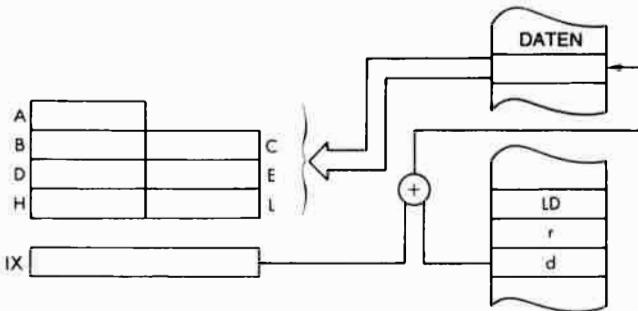

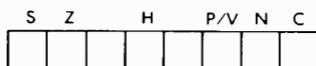

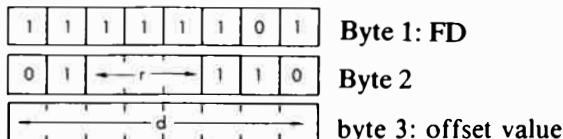

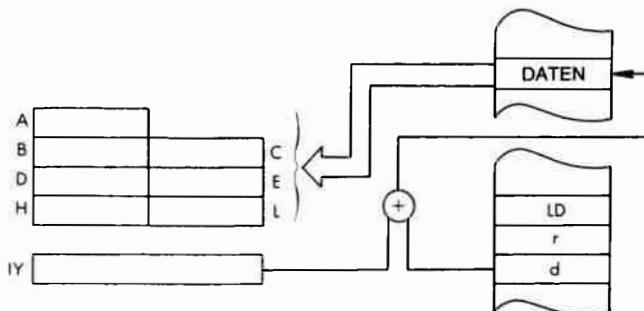

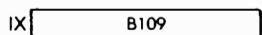

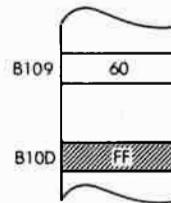

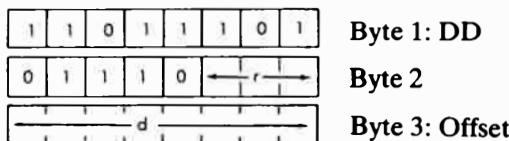

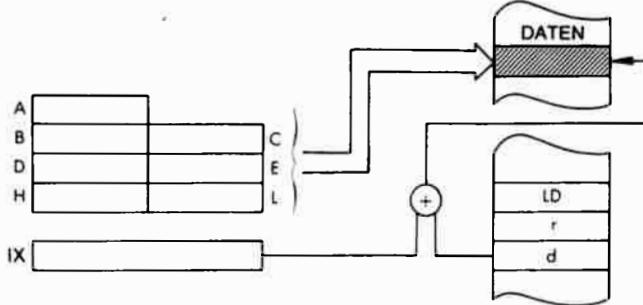

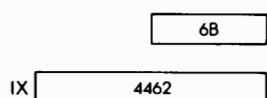

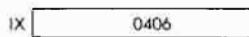

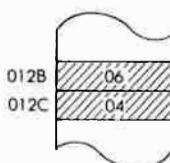

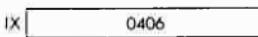

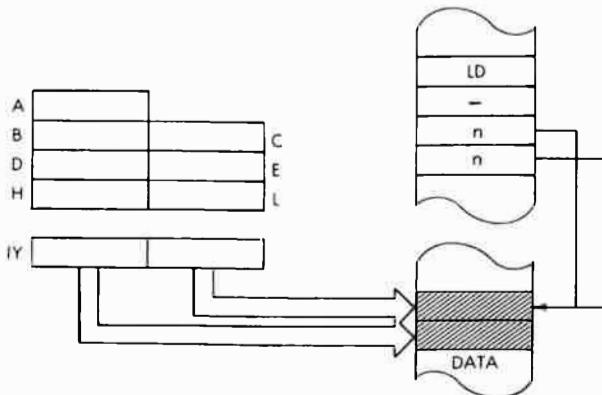

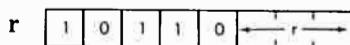

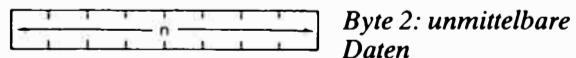

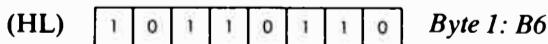

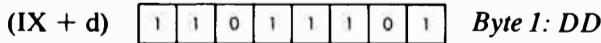

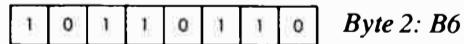

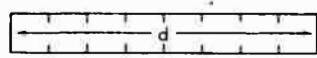

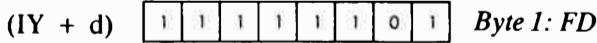

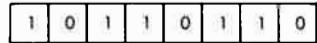

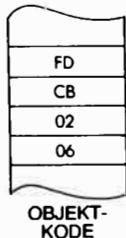

| Abb. 5.5:   | Die indizierte Adressierung hat einen Zweibyte-Opcode . . . . .                 | 438 |

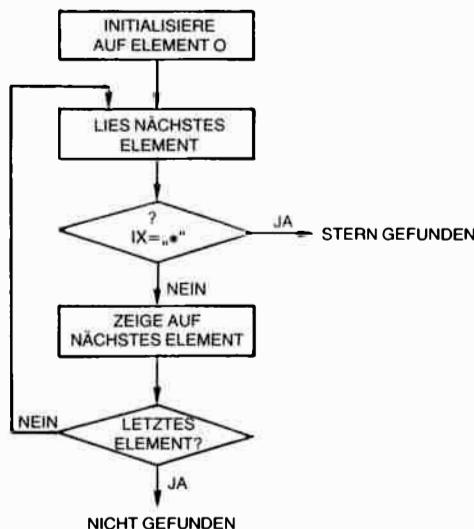

| Abb. 5.6:   | Flußdiagramm zur Zeichensuche . . . . .                                         | 440 |

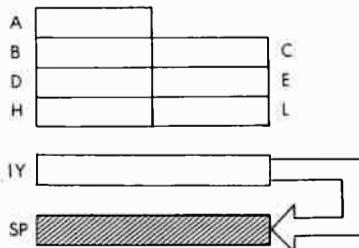

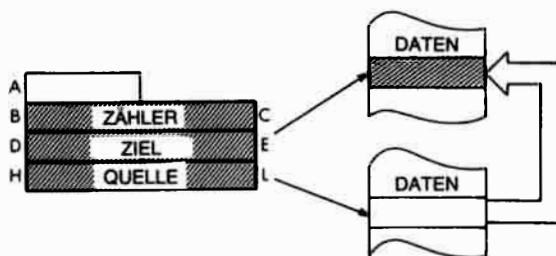

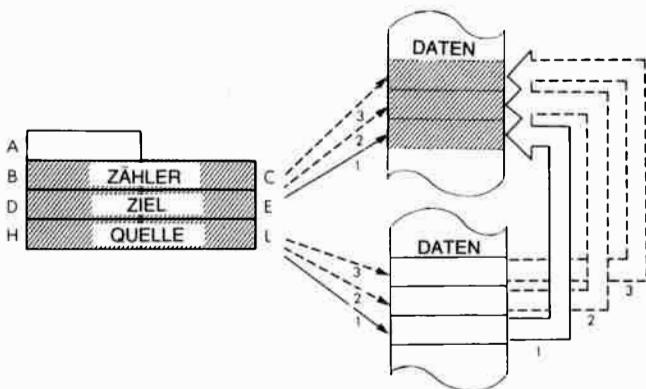

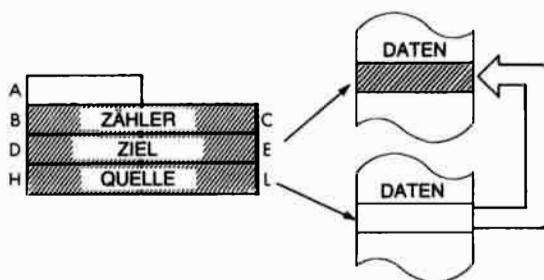

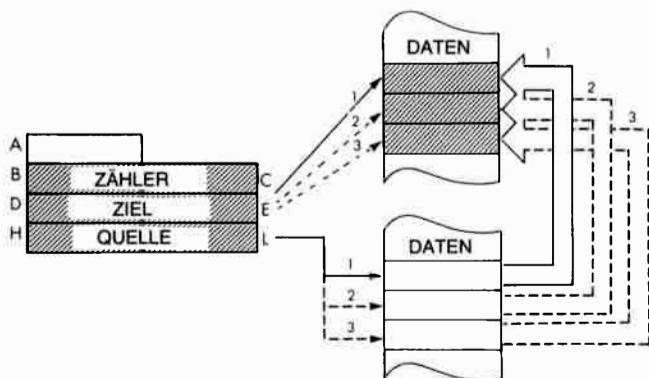

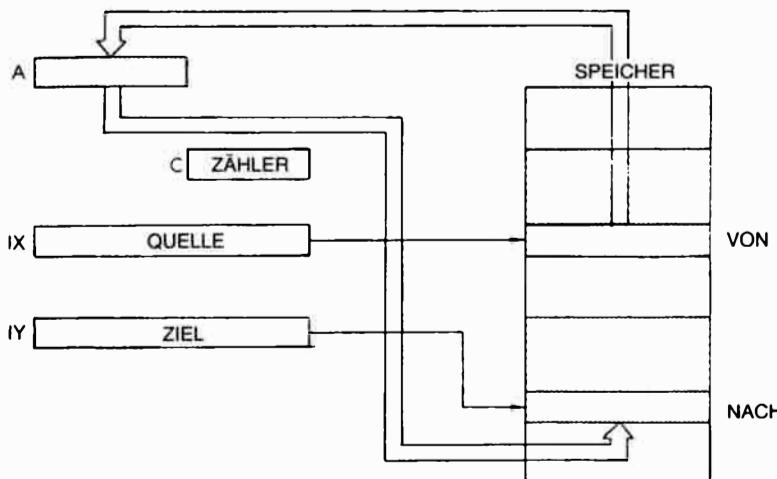

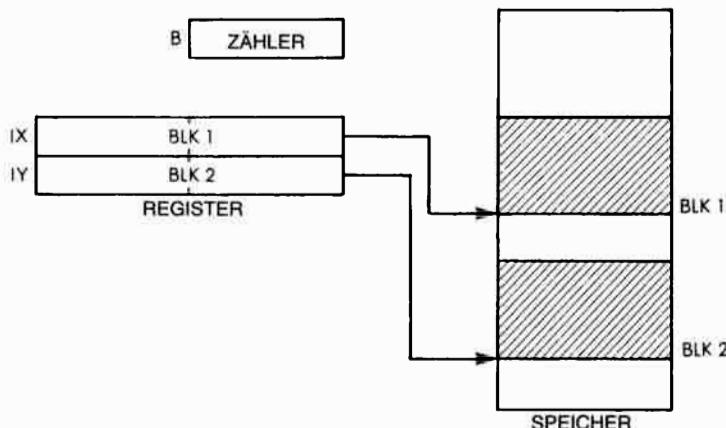

| Abb. 5.7:   | Blocktransfer – Initialisierung der Register . . . . .                          | 441 |

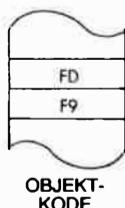

| Abb. 5.8:   | Speicherbelegung beim Blocktransfer . . . . .                                   | 443 |

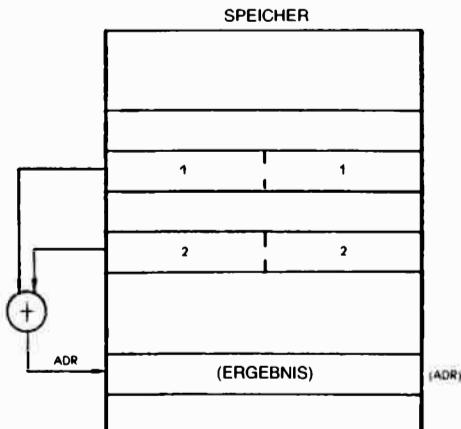

| Abb. 5.9:   | Addition zweier Blöcke: BLK1=BLK1+BLK2 . . . . .                                | 446 |

| Abb. 5.10:  | Speicherorganisation für den Blocktransfer . . . . .                            | 447 |

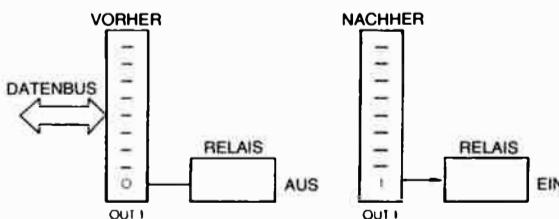

| Abb. 6.1:   | Ein Relais einschalten . . . . .                                                | 451 |

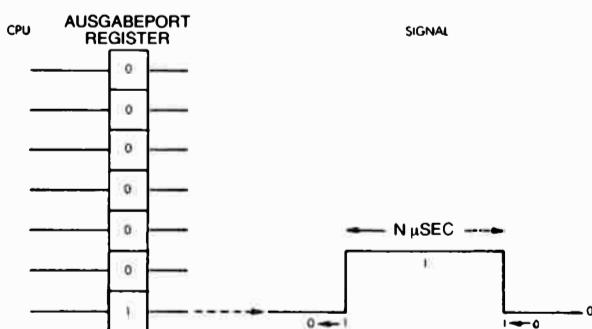

| Abb. 6.2:   | Ein programmierter Impuls . . . . .                                             | 451 |

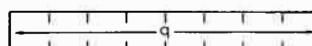

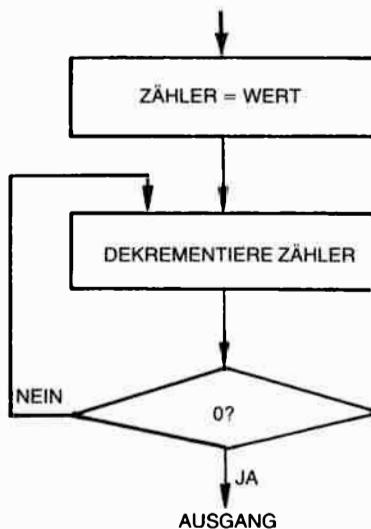

| Abb. 6.3:   | Prinzipielles Flußdiagramm einer Verzögerungsschleife . . . . .                 | 452 |

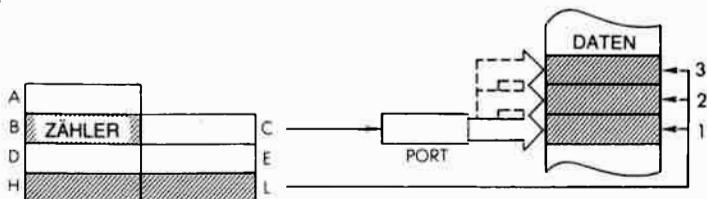

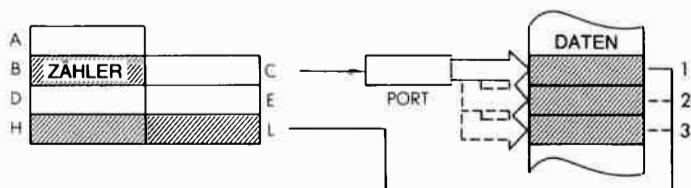

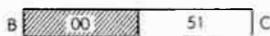

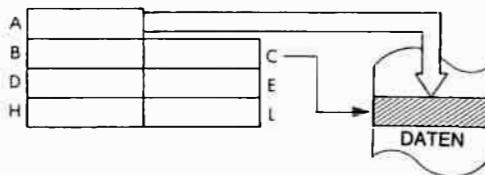

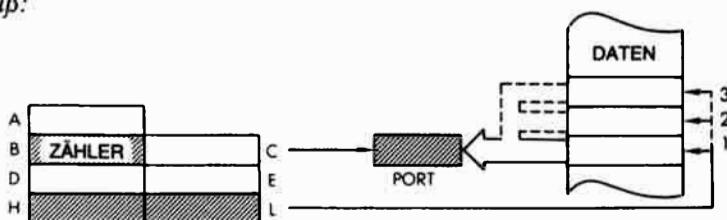

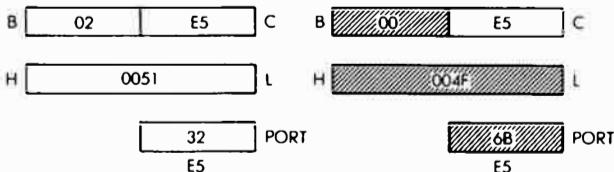

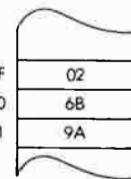

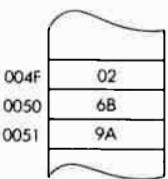

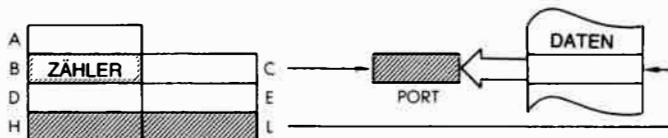

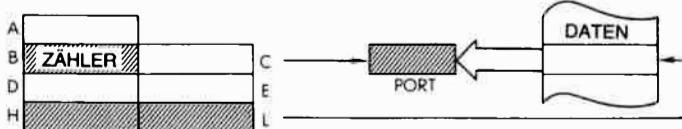

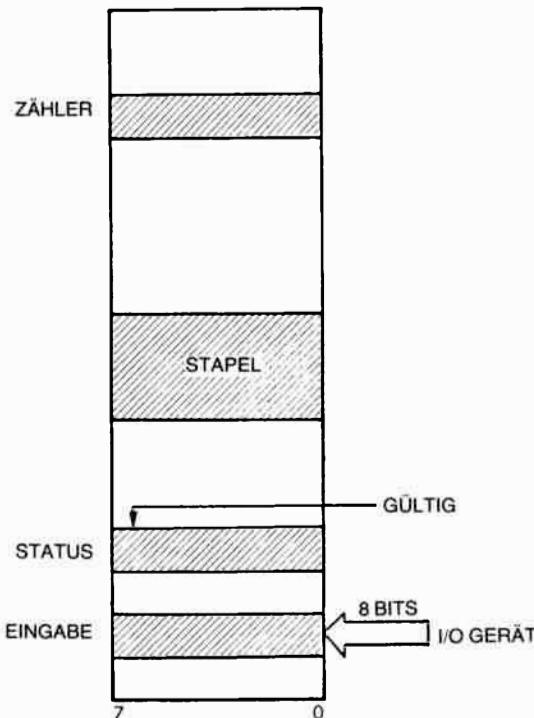

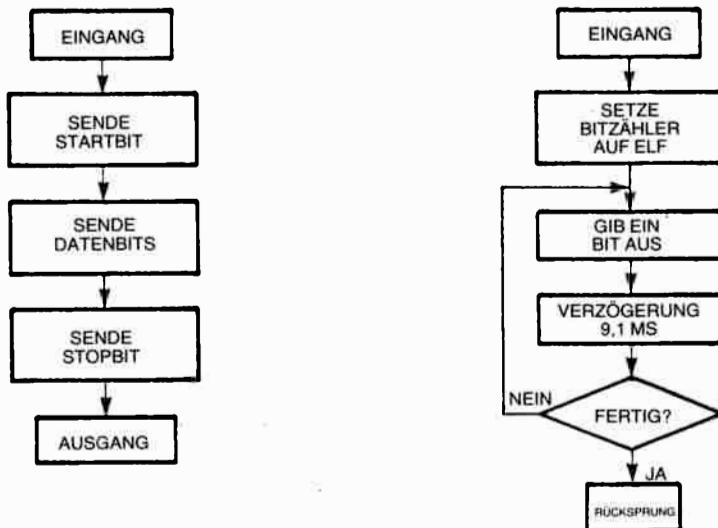

| Abb. 6.4:   | Parallele Übertragung von Worten – der Speicher                                 | 456 |

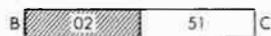

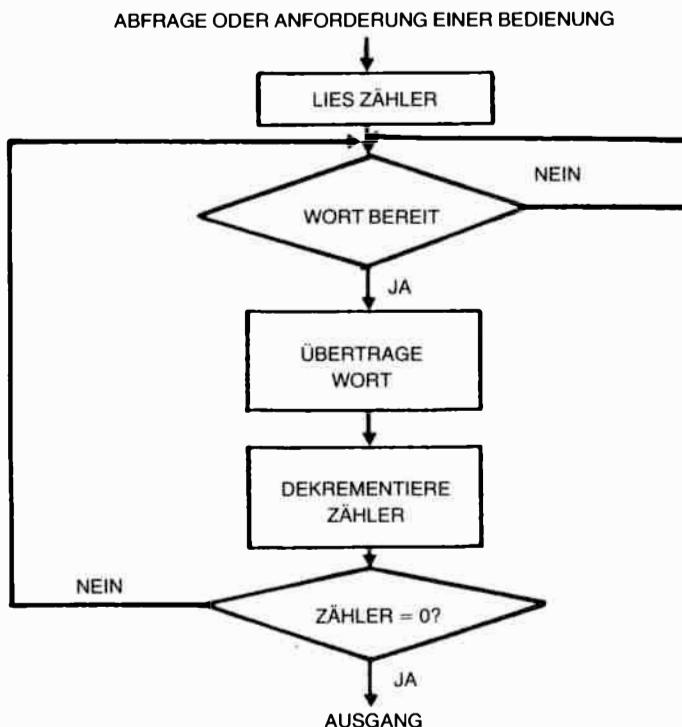

| Abb. 6.5:   | Parallele Übertragung von Worten: Flußdiagramm                                  | 457 |

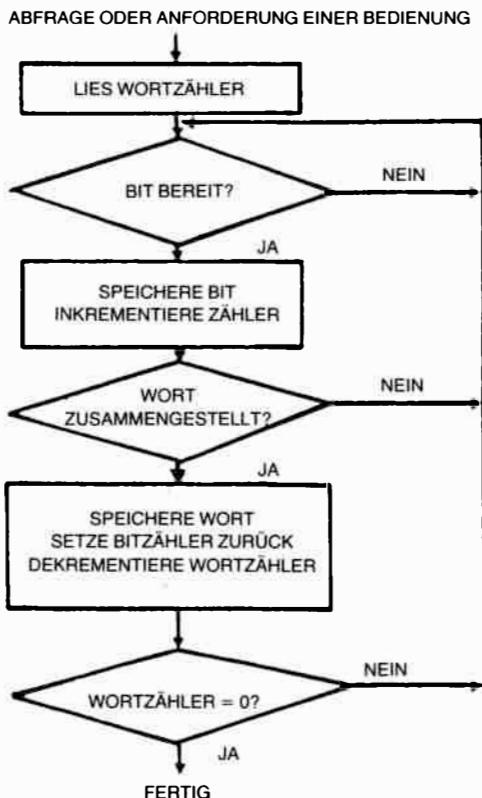

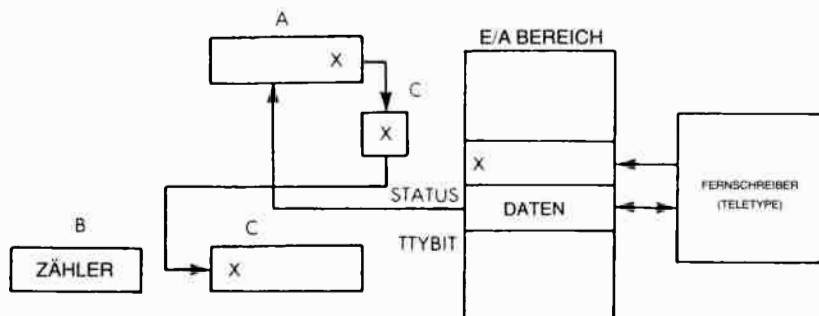

| Abb. 6.6:   | Bitserielle Übertragung . . . . .                                               | 461 |

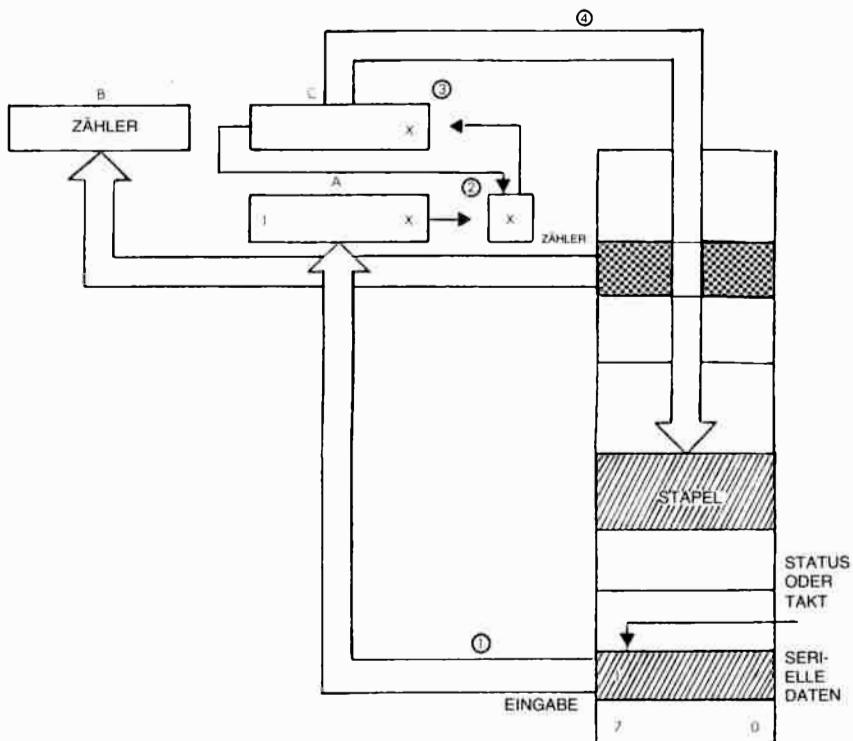

| Abb. 6.7:   | Seriell nach Parallel: die Register . . . . .                                   | 462 |

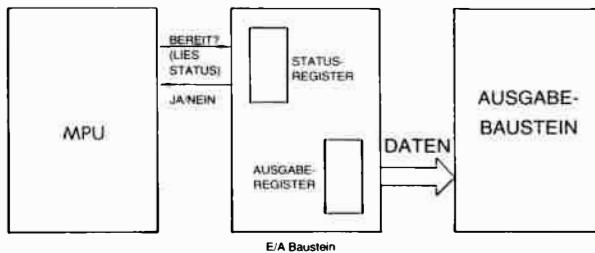

| Abb. 6.8:   | Handshaking (Ausgabe) . . . . .                                                 | 466 |

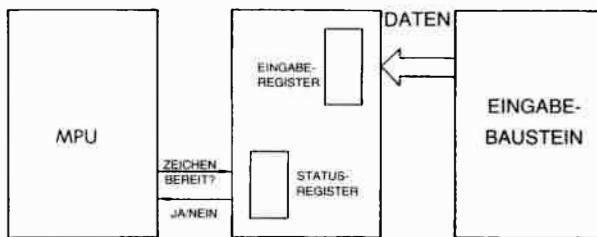

| Abb. 6.8.a: | Handshaking (Eingabe) . . . . .                                                 | 466 |

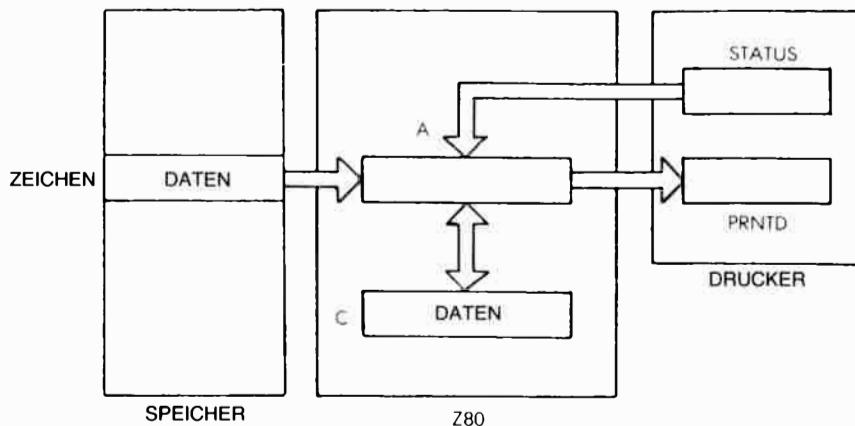

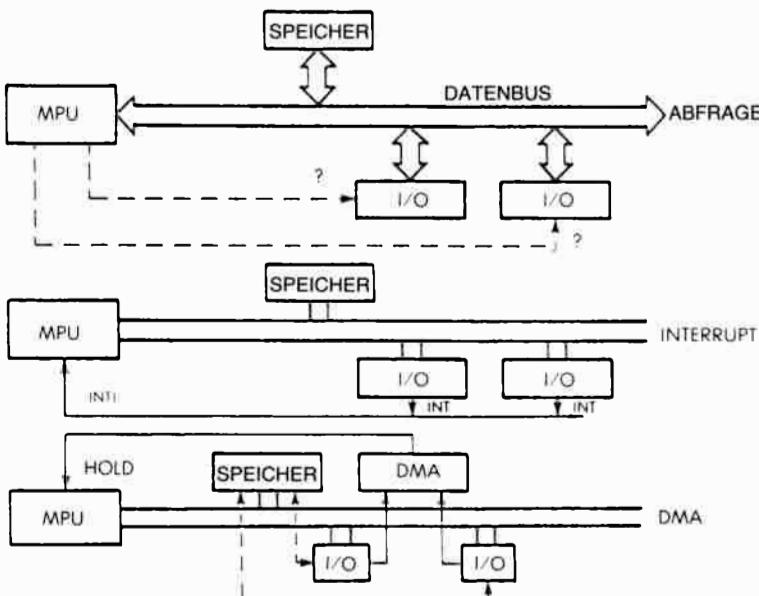

| Abb. 6.9:   | Drucker – Datenwege . . . . .                                                   | 467 |

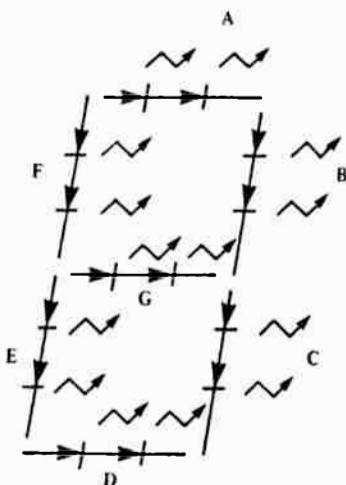

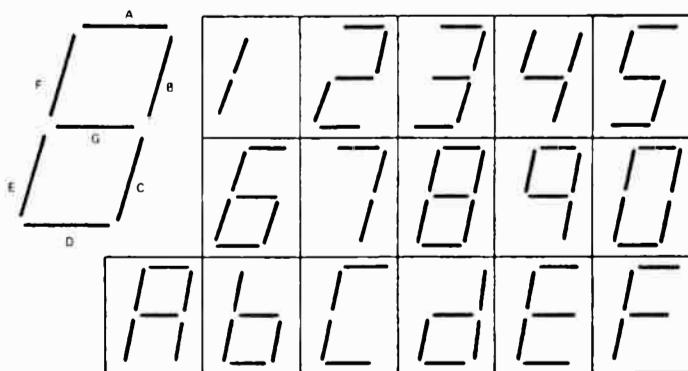

| Abb. 6.10:  | Siebensegmentanzeige LED . . . . .                                              | 469 |

| Abb. 6.11:  | Hexadezimalzeichen, die mit einer Siebensegmentanzeige erzeugt werden . . . . . | 469 |

|            |                                                                        |     |

|------------|------------------------------------------------------------------------|-----|

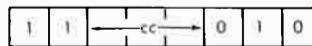

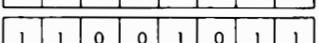

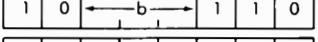

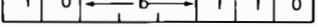

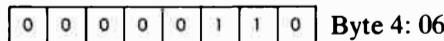

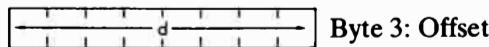

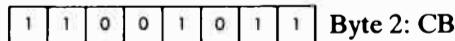

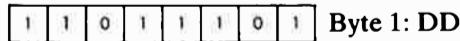

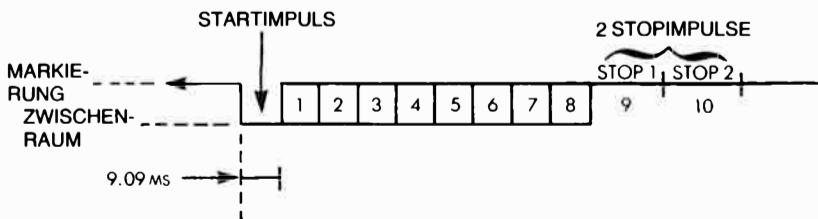

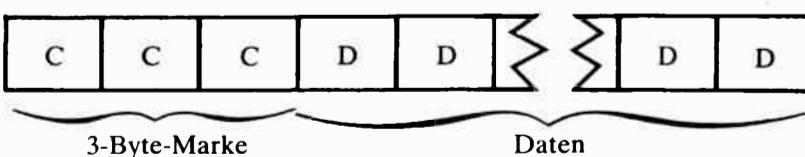

| Abb. 6.12: | Format eines Fernschreiberwortes . . . . .                             | 472 |

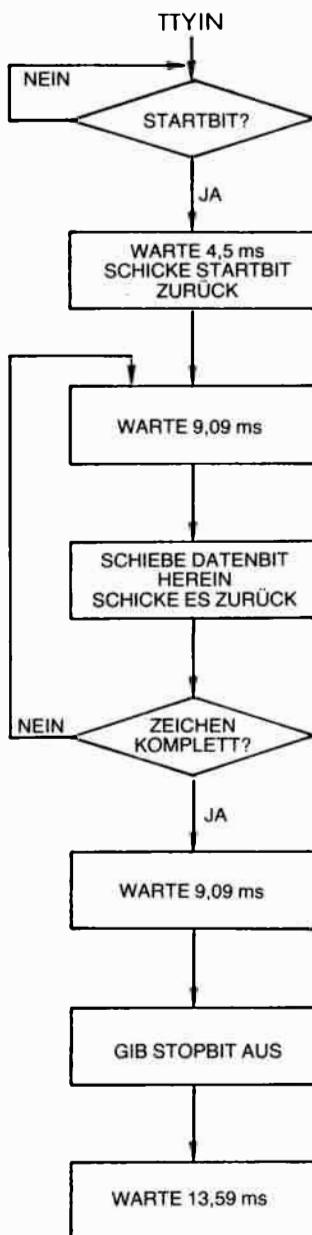

| Abb. 6.13: | TTY-Eingabe mit Echo . . . . .                                         | 473 |

| Abb. 6.14: | Fernschreiberprogramm . . . . .                                        | 474 |

| Abb. 6.15: | Eingabe vom Fernschreiber . . . . .                                    | 475 |

| Abb. 6.16: | Ausgabe auf den Fernschreiber . . . . .                                | 476 |

| Abb. 6.17: | Ausdruck eines Speicherbereichs . . . . .                              | 478 |

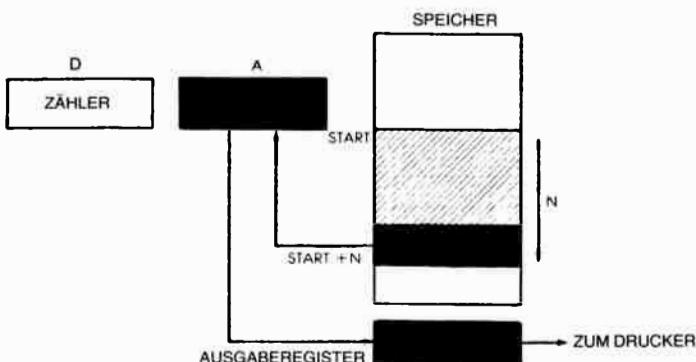

| Abb. 6.18: | Drei Methoden der Ein-/Ausgabesteuerung . . . . .                      | 479 |

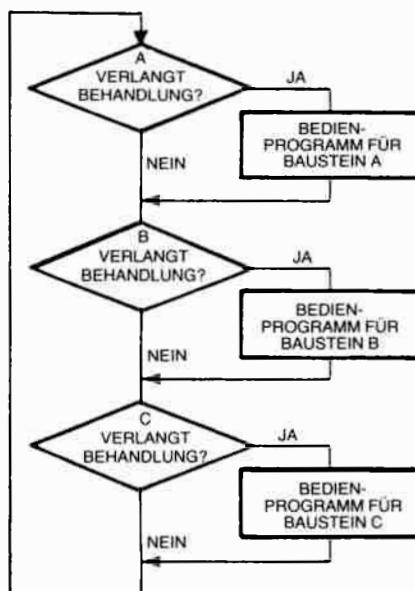

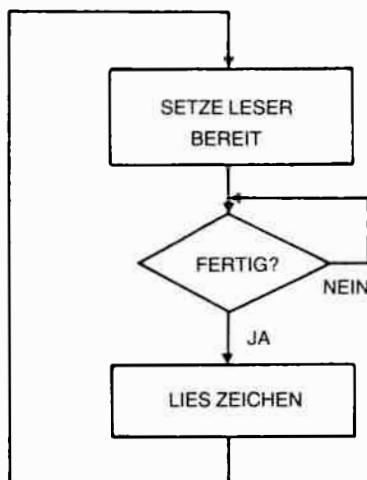

| Abb. 6.19: | Flußdiagramm einer Pollingschleife . . . . .                           | 481 |

| Abb. 6.20: | Eingabe von einem Lochstreifenleser . . . . .                          | 481 |

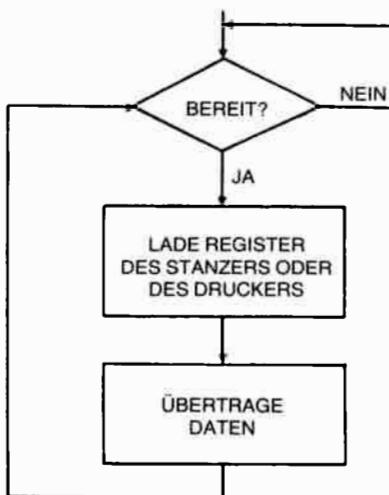

| Abb. 6.21: | Ausgabe auf einen Stanzer oder Drucker . . . . .                       | 482 |

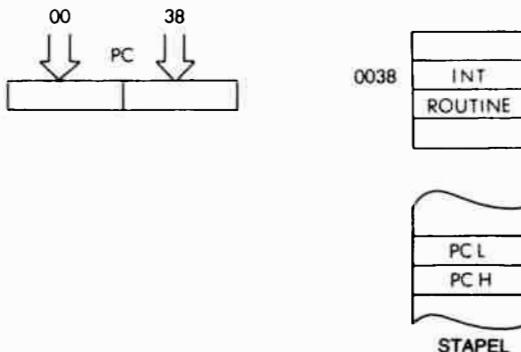

| Abb. 6.22: | Der Stapel des Z80 nach einem Interrupt . . . . .                      | 482 |

| Abb. 6.23: | Sicherstellen einiger Arbeitsregister . . . . .                        | 483 |

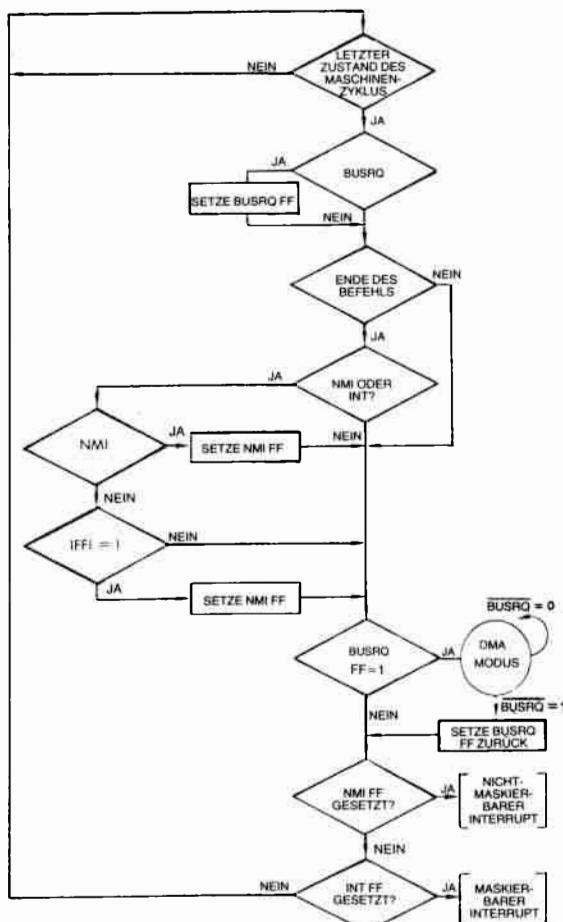

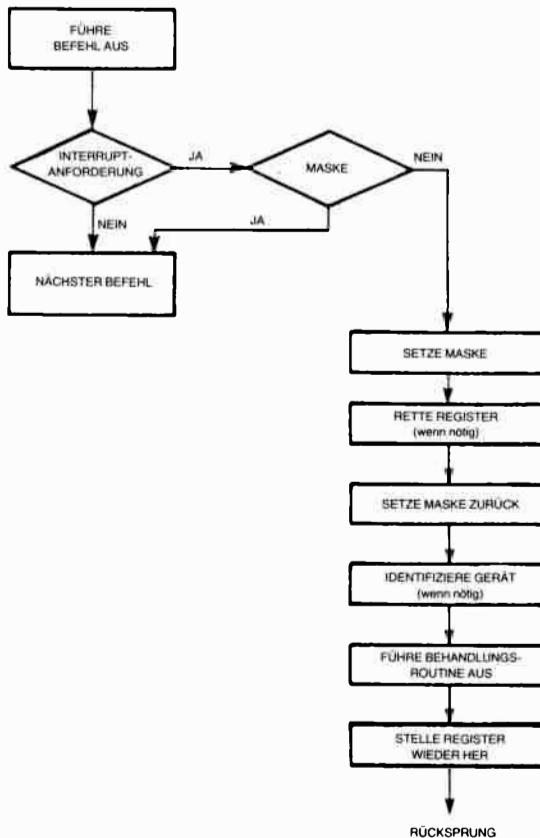

| Abb. 6.24: | Interrupt Folge . . . . .                                              | 484 |

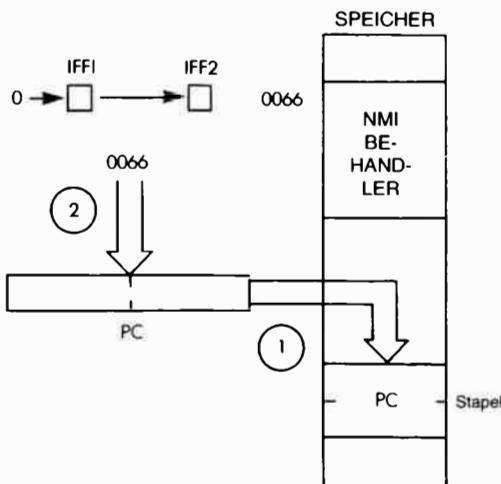

| Abb. 6.25: | Der NMI erzwingt eine automatische Verzweigung                         | 485 |

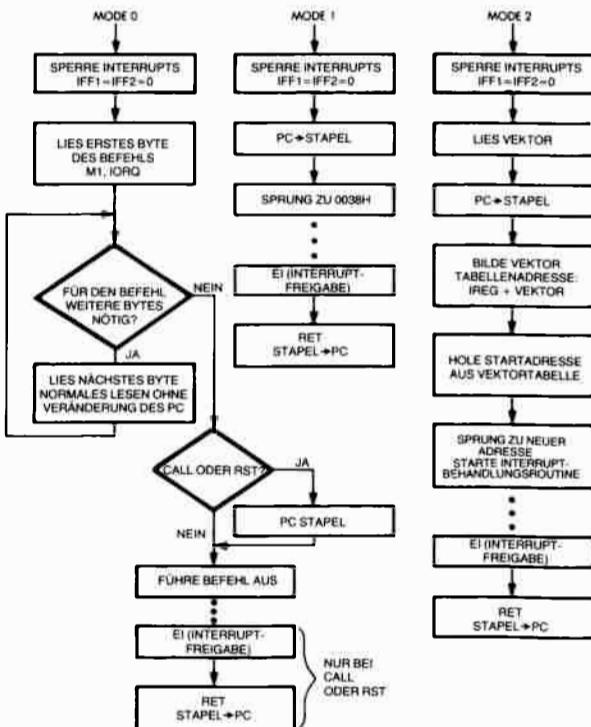

| Abb. 6.26: | Interrupt Modi . . . . .                                               | 487 |

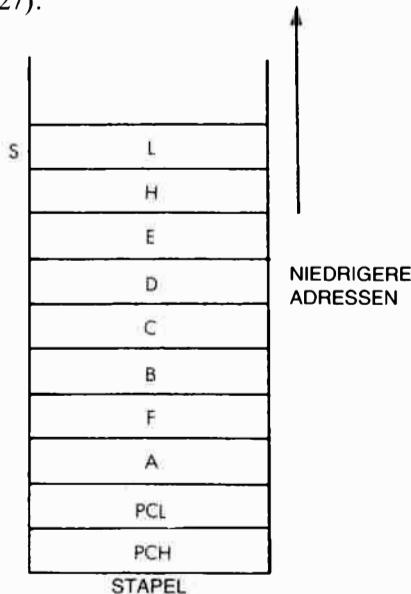

| Abb. 6.27: | Sicherstellen der Register . . . . .                                   | 488 |

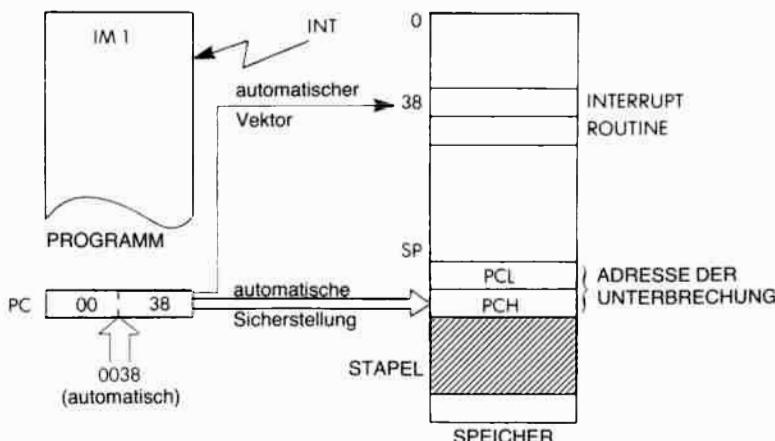

| Abb. 6.28: | Interrupt Modus 1 . . . . .                                            | 489 |

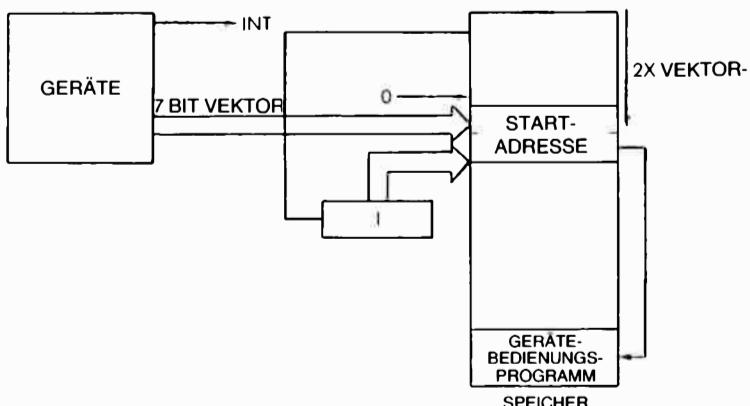

| Abb. 6.29: | Interrupt Modus 2 . . . . .                                            | 490 |

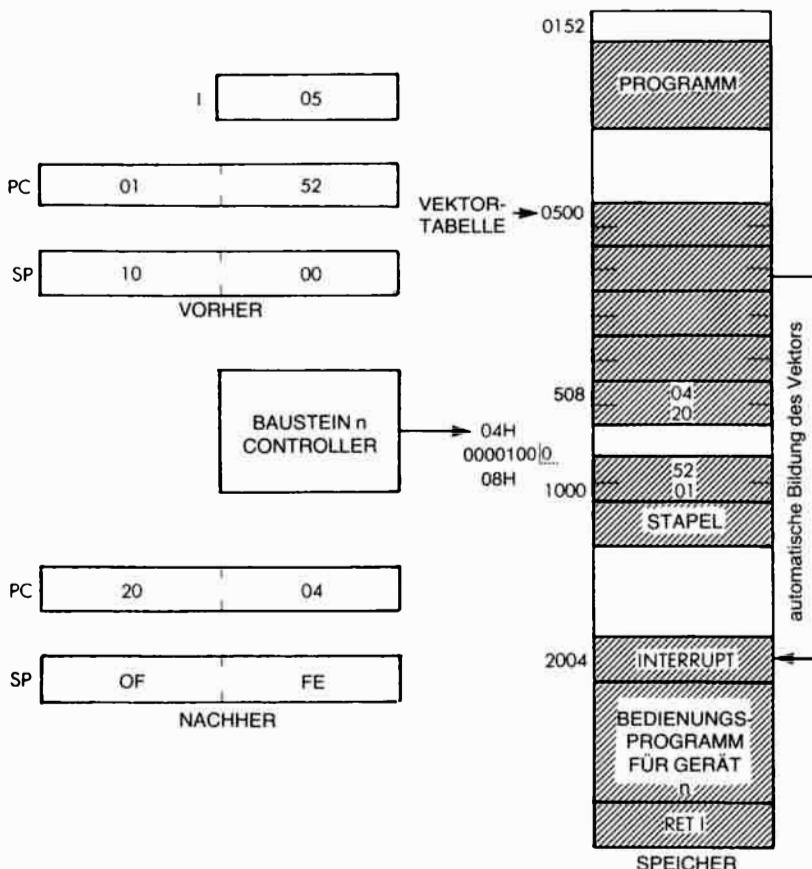

| Abb. 6.30: | Modus 2 – ein praktisches Beispiel . . . . .                           | 491 |

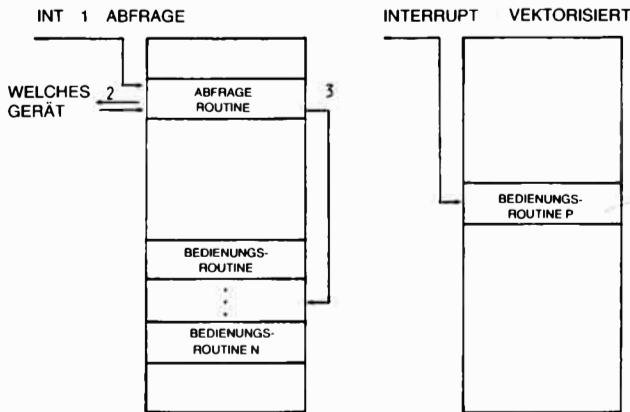

| Abb. 6.31: | Abfrage und vektorisierter Interrupt . . . . .                         | 493 |

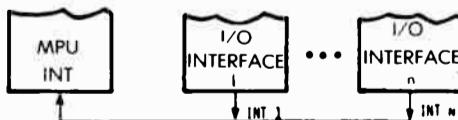

| Abb. 6.32: | Mehrere Geräte können die gleiche Interruptleitung verwenden . . . . . | 494 |

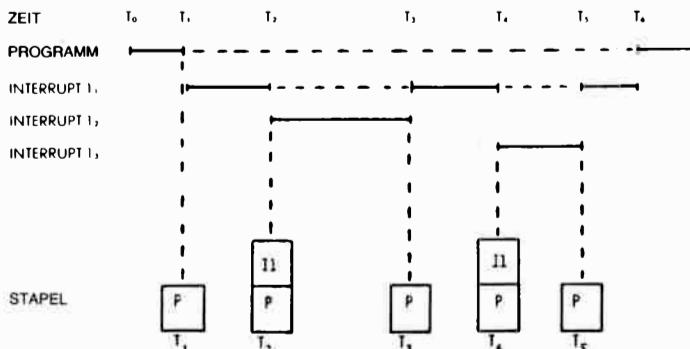

| Abb. 6.33: | Inhalt des Stapels während mehrerer Interrupts . . .                   | 494 |

| Abb. 6.34: | Interruptlogik . . . . .                                               | 496 |

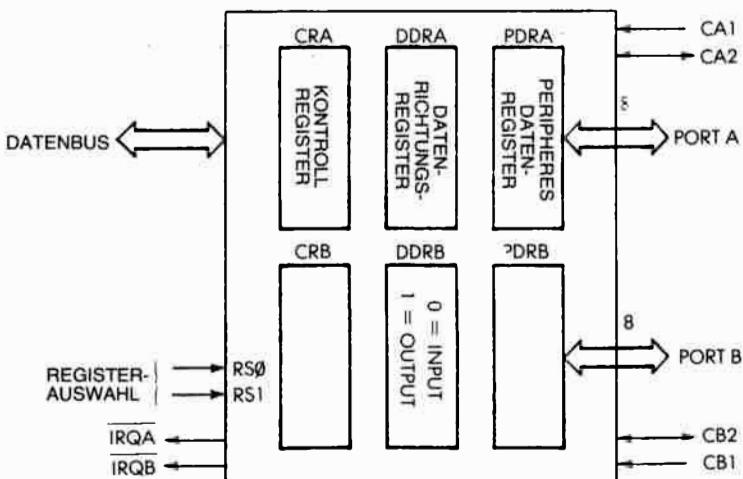

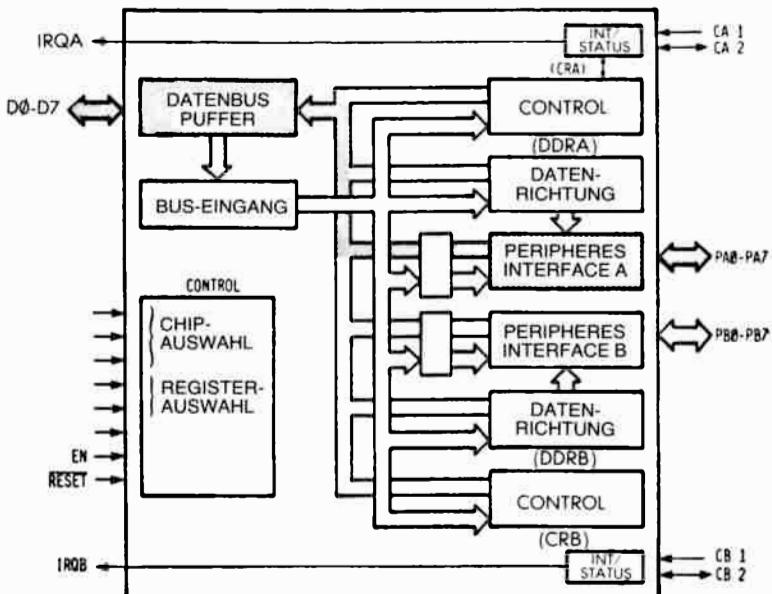

| Abb. 7.1:  | Typische PIO . . . . .                                                 | 498 |

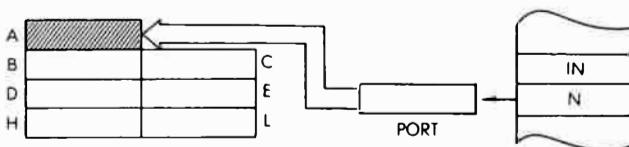

| Abb. 7.2:  | Der Gebrauch einer PIO – Laden des Kontrollregisters . . . . .         | 499 |

| Abb. 7.3:  | Der Gebrauch einer PIO – Laden der Datenrichtung                       | 500 |

| Abb. 7.4:  | Der Gebrauch einer PIO – Lesen des Status . . . .                      | 500 |

| Abb. 7.5:  | Der Gebrauch einer PIO – Lesen einer Eingabe                           | 501 |

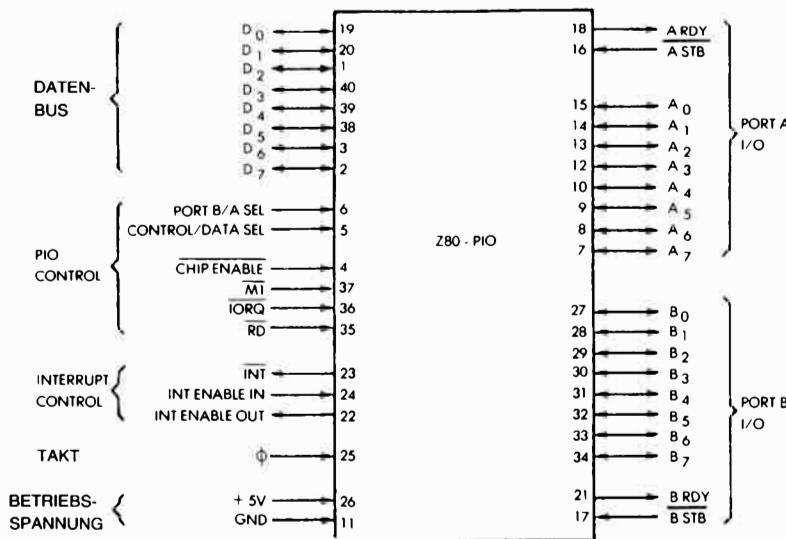

| Abb. 7.6:  | Die Anschlußbelegung der Z80 PIO . . . . .                             | 502 |

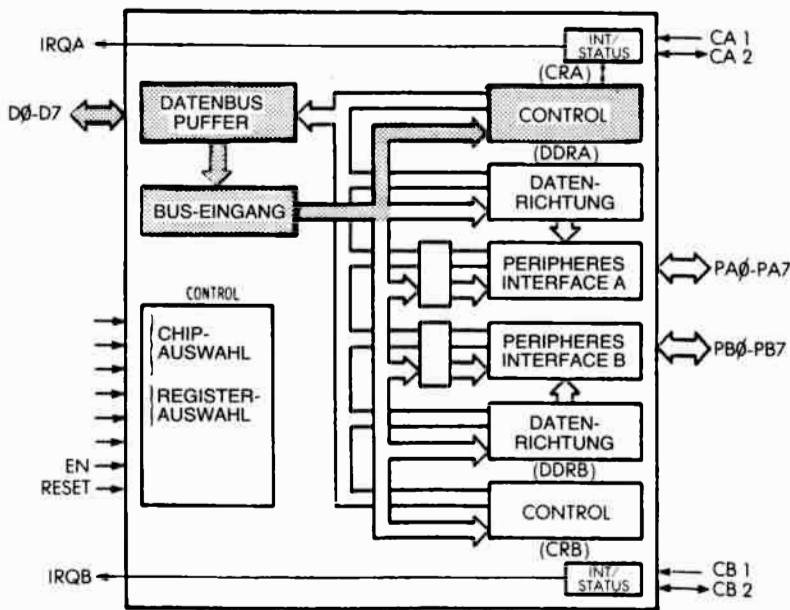

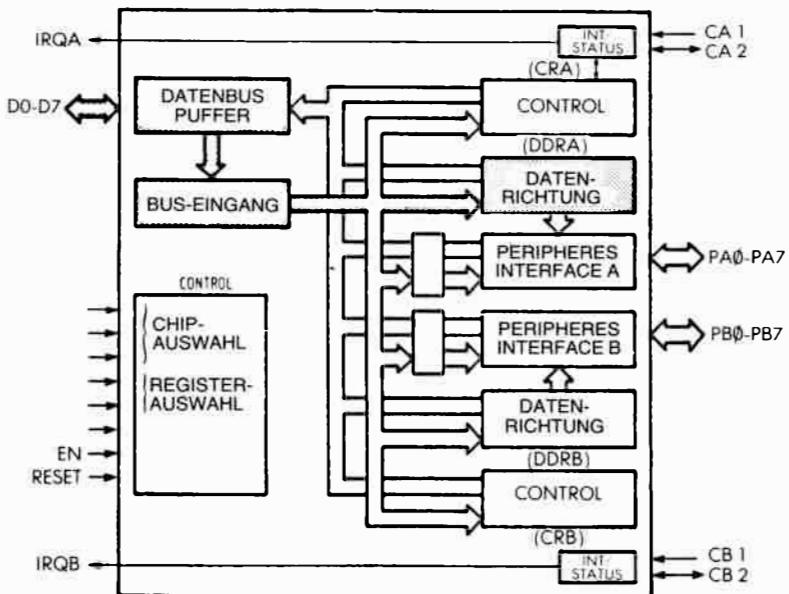

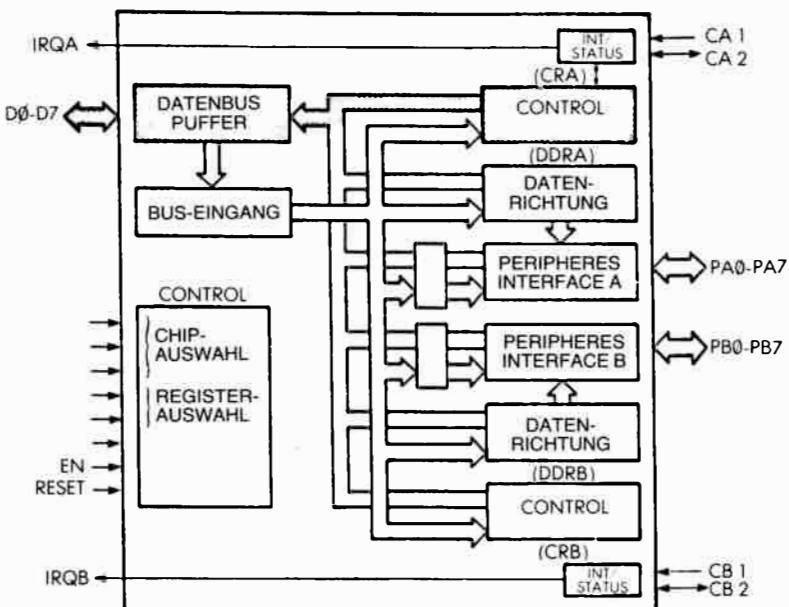

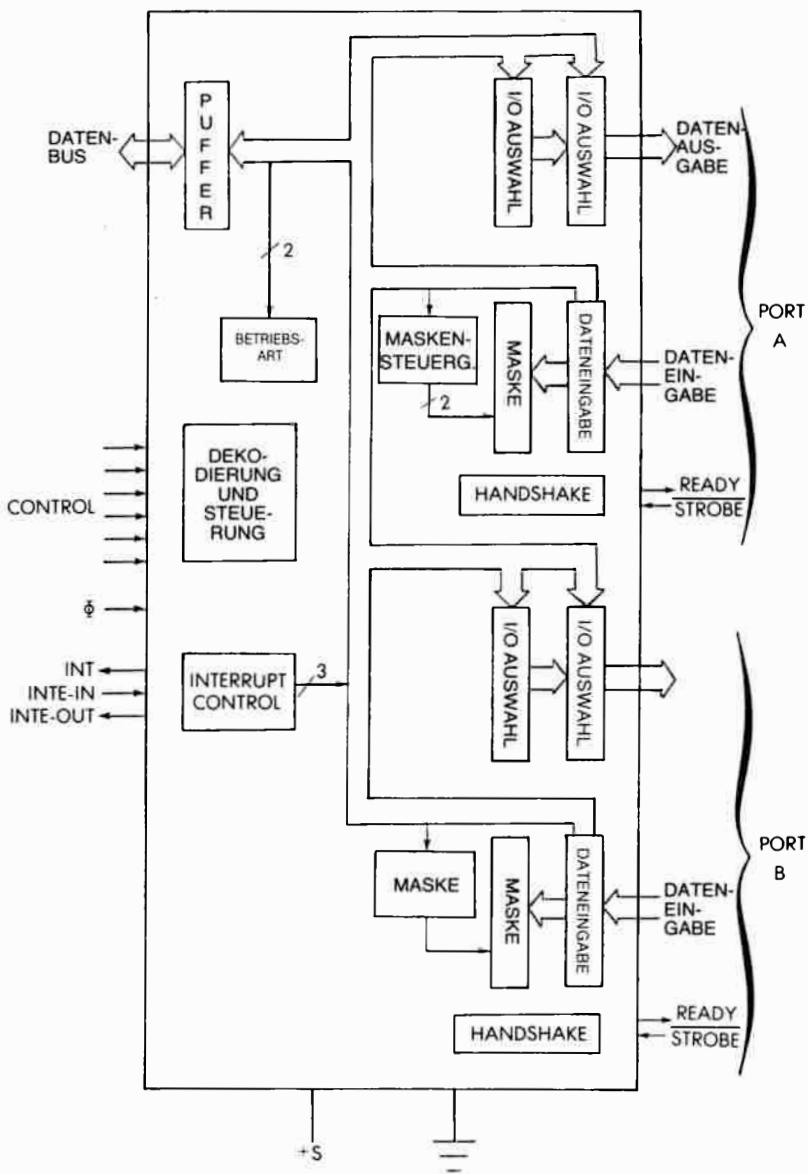

| Abb. 7.7:  | Blockdiagramm der Z80 PIO . . . . .                                    | 503 |

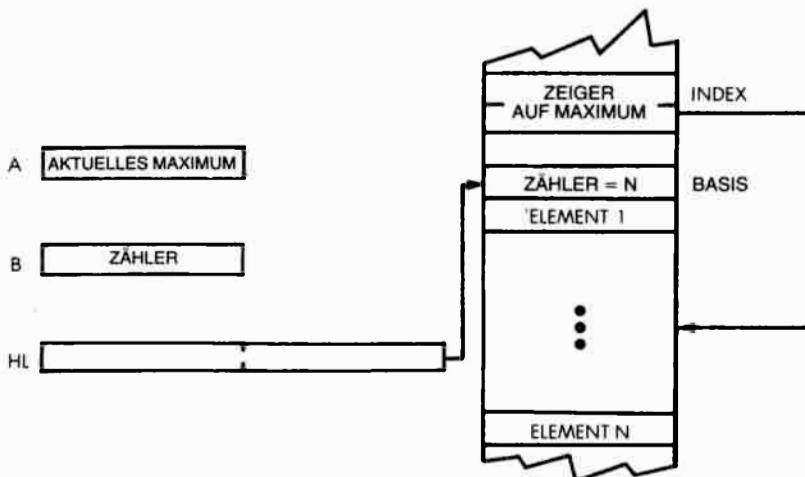

| Abb. 8.1:  | Größtes Element in einer Tabelle . . . . .                             | 513 |

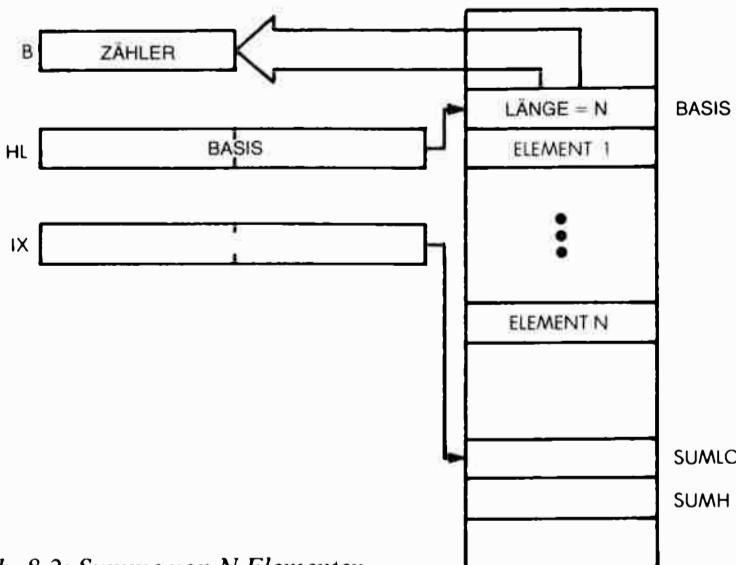

| Abb. 8.2:  | Summe von N Elementen . . . . .                                        | 514 |

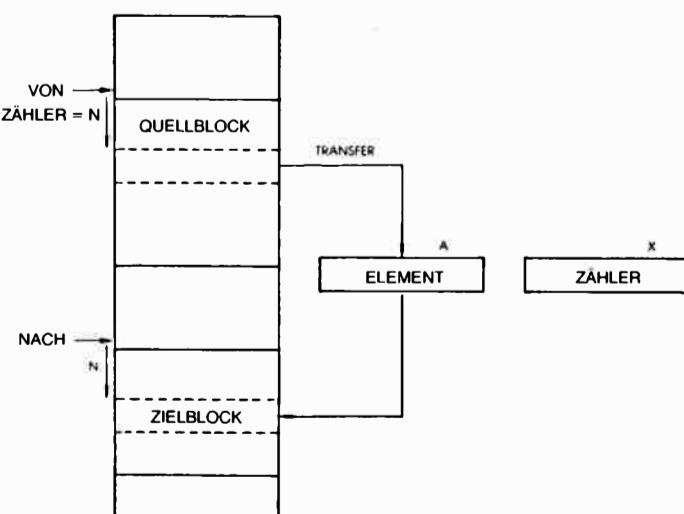

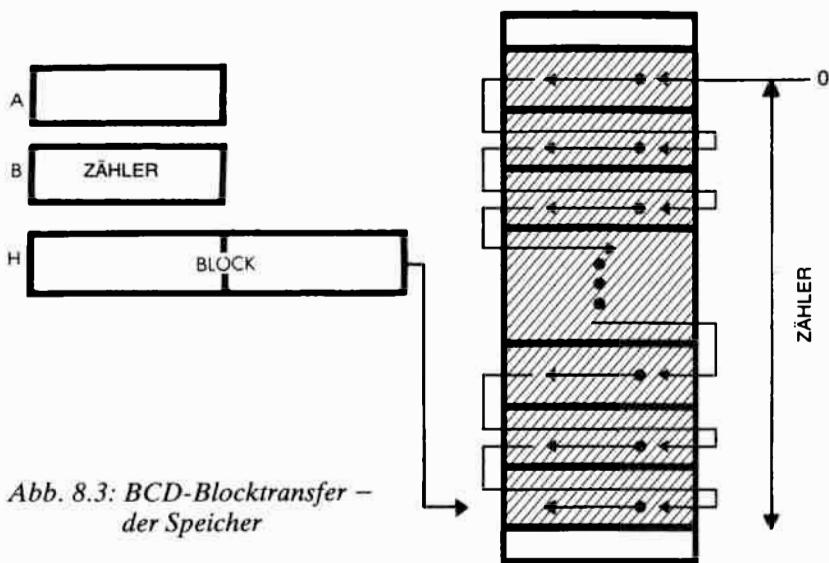

| Abb. 8.3:  | BCD-Blocktransfer – der Speicher . . . . .                             | 517 |

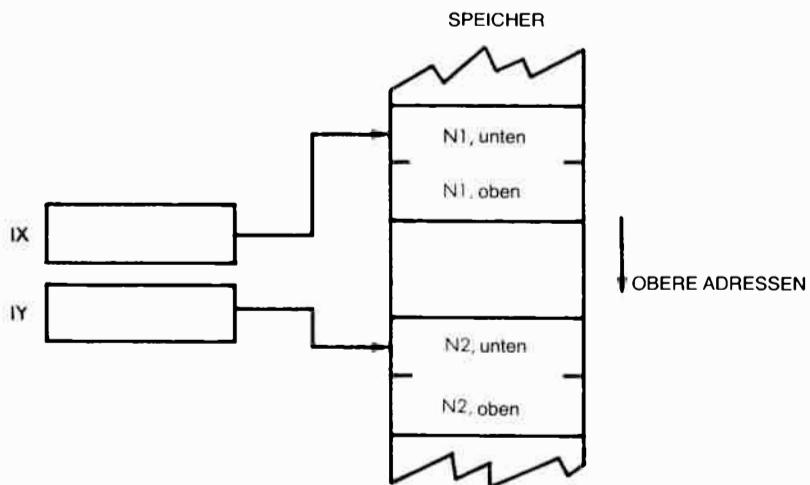

| Abb. 8.4:  | Vergleich zweier vorzeichenbehafteter Zahlen . . .                     | 518 |

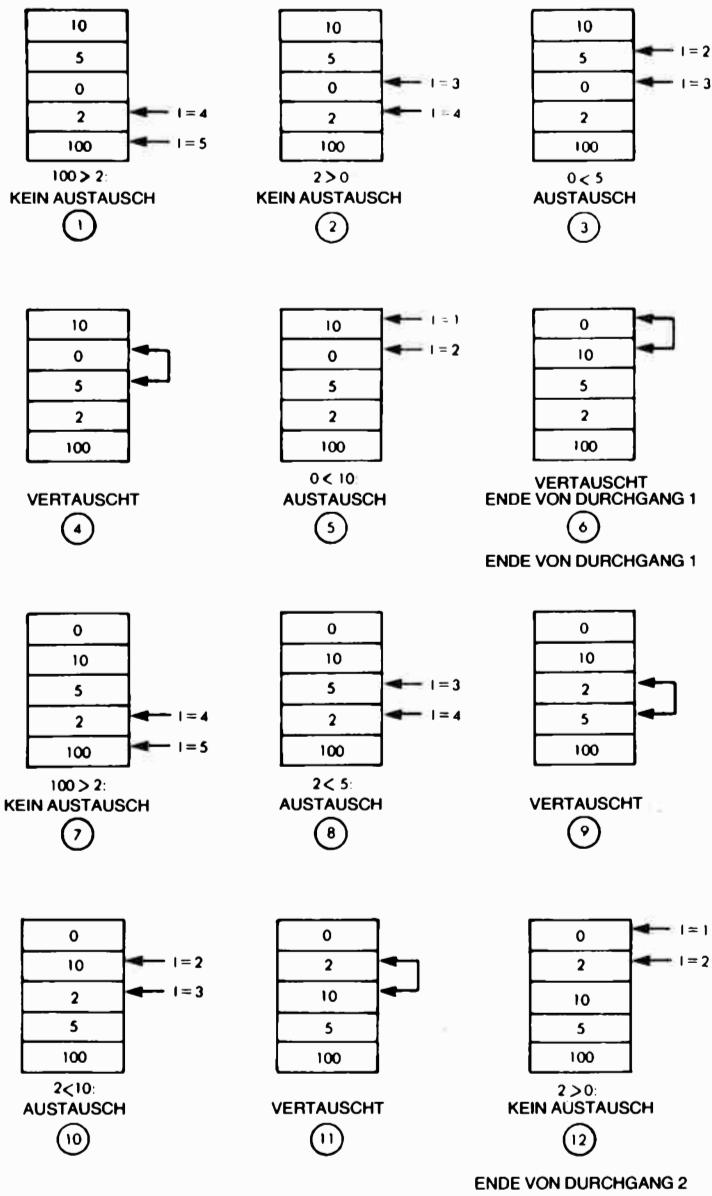

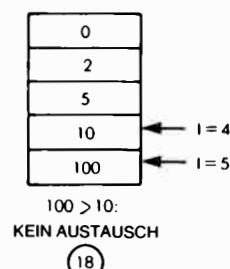

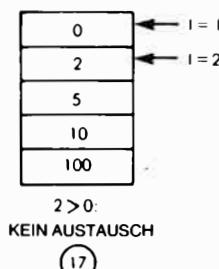

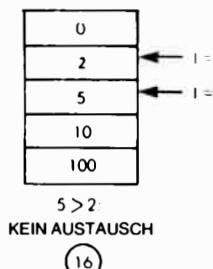

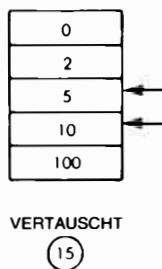

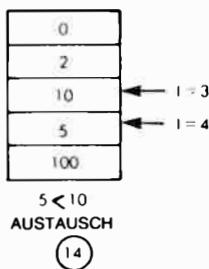

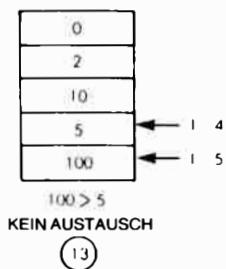

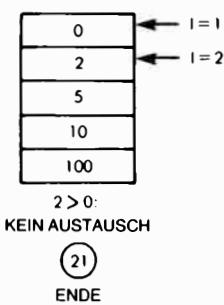

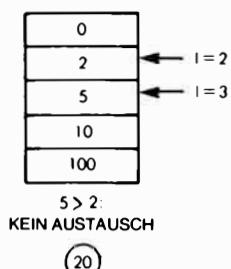

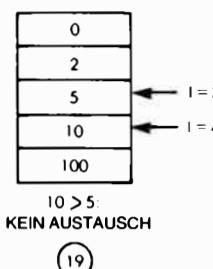

| Abb. 8.5:  | Bubble-Sort Beispiel: Schritte 1 bis 12 . . . . .                      | 520 |

| Abb. 8.6:  | Bubble-Sort Beispiel: Schritte 13 bis 21 . . . . .                     | 521 |

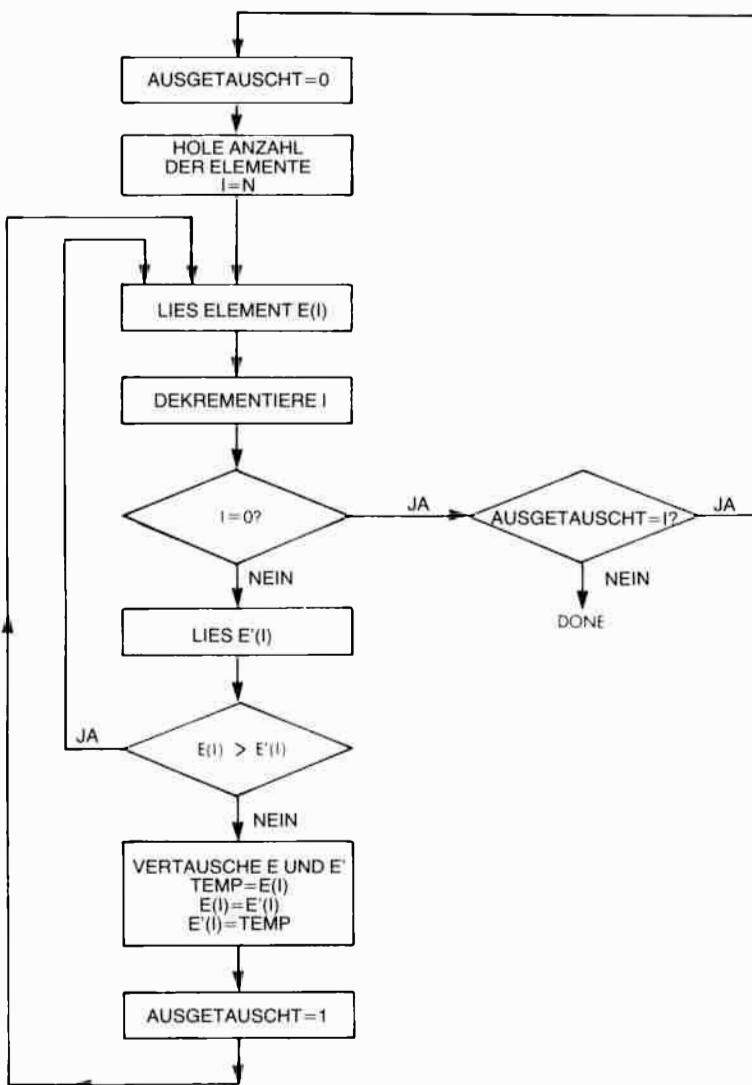

| Abb. 8.7:  | Bubble-Sort Flußdiagramm . . . . .                                     | 522 |

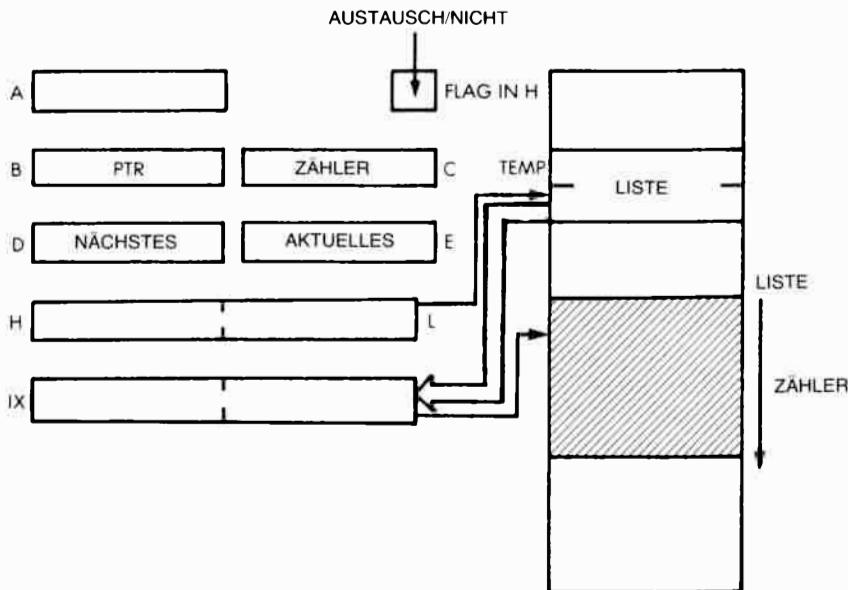

| Abb. 8.8:  | Bubble-Sort . . . . .                                                  | 523 |

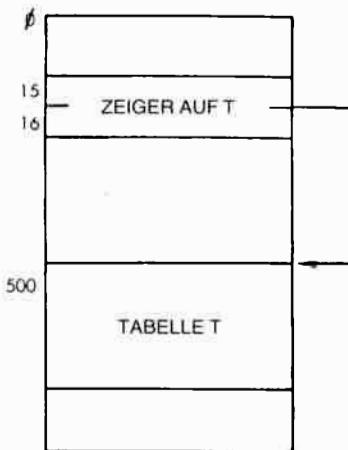

| Abb. 9.1:  | Ein indirekter Zeiger . . . . .                                        | 526 |

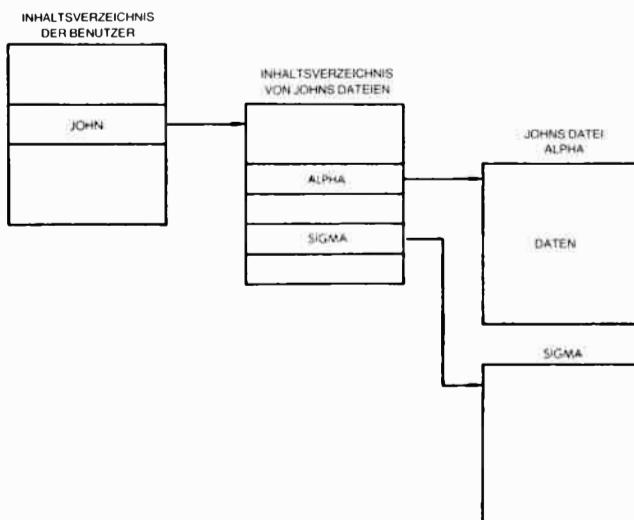

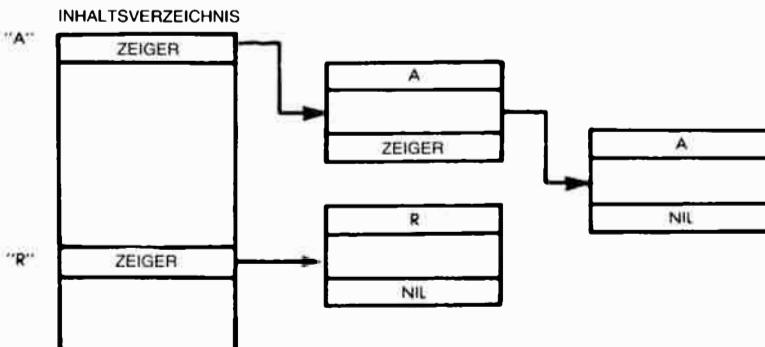

| Abb. 9.2:  | Struktur eines Inhaltsverzeichnisses . . . . .                         | 527 |

| Abb. 9.3:  | Eine verkettete Liste . . . . .                                        | 528 |

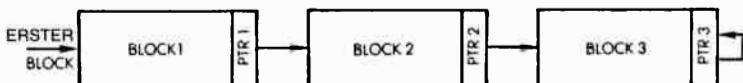

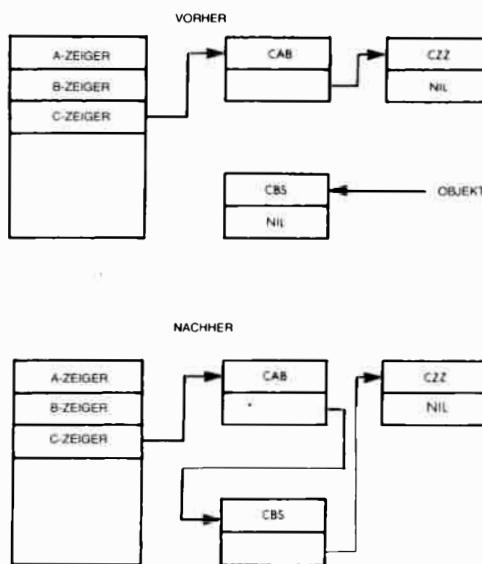

| Abb. 9.4:  | Einfügen eines Blocks . . . . .                                        | 528 |

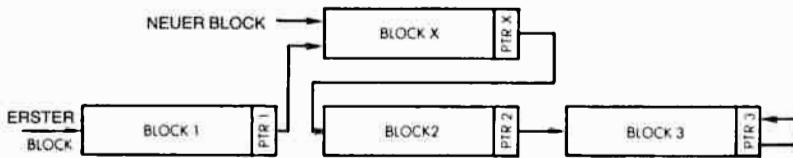

| Abb. 9.5:  | Eine Schlange . . . . .                                                | 529 |

| Abb. 9.6:  | Ringliste . . . . .                                                    | 530 |

---

|            |                                                |     |

|------------|------------------------------------------------|-----|

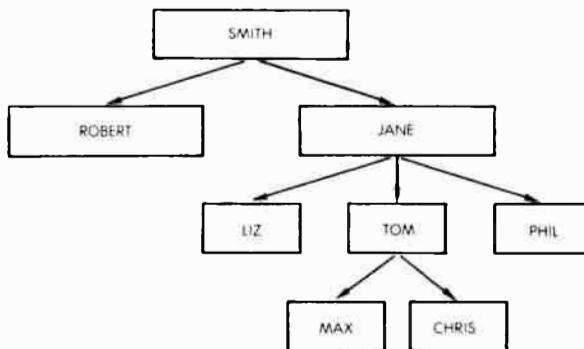

| Abb. 9.7:  | Stammbaum                                      | 531 |

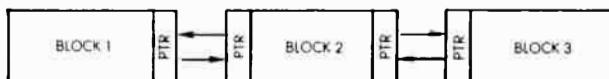

| Abb. 9.8:  | Doppelt verkettete Liste                       | 531 |

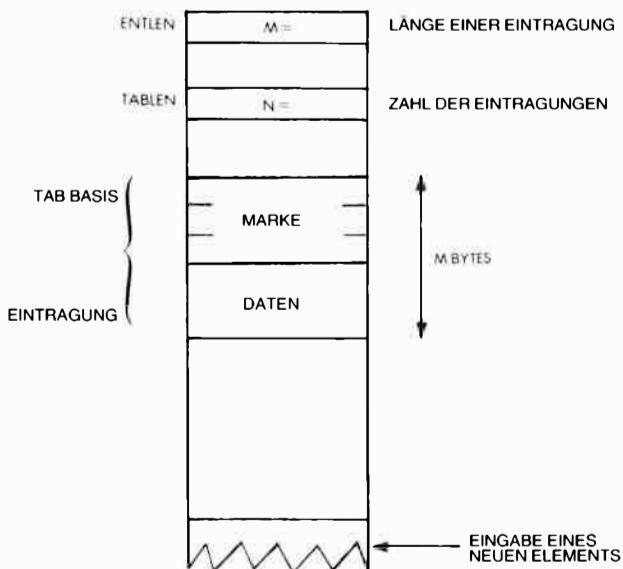

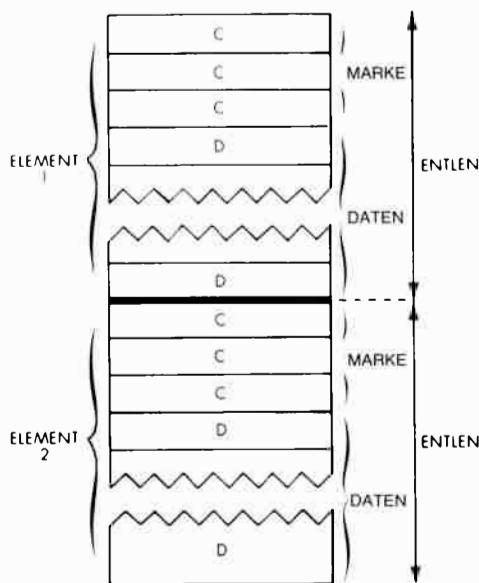

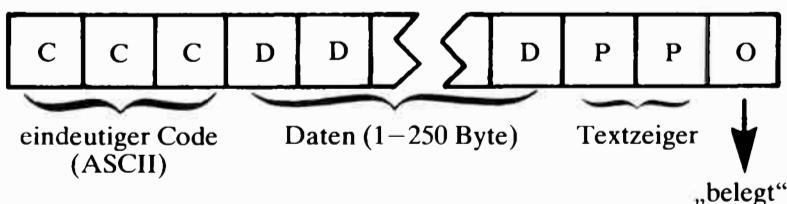

| Abb. 9.9:  | Die Tabellenstruktur                           | 534 |

| Abb. 9.10: | Typische Eintragungen in die Liste             | 534 |

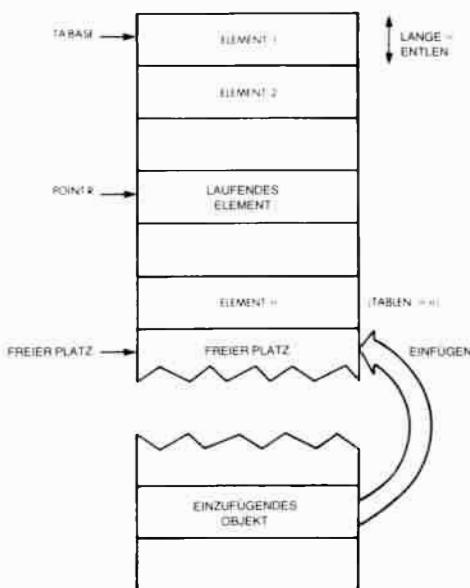

| Abb. 9.11: | Die einfache Liste                             | 535 |

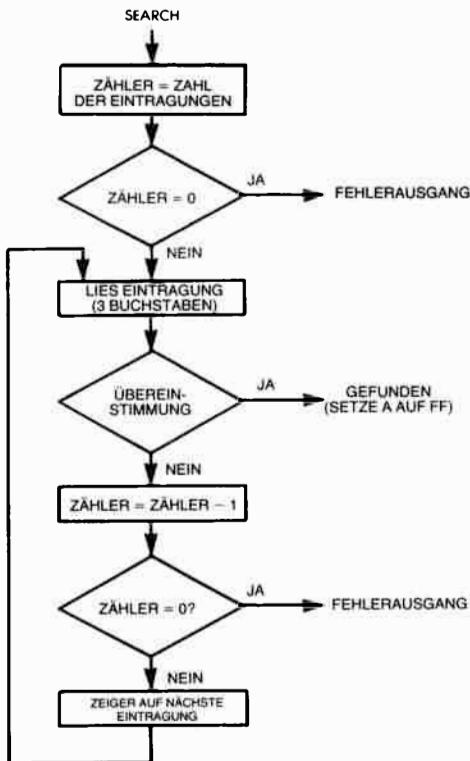

| Abb. 9.12: | Flußdiagramm zur Suche in der Tabelle          | 536 |

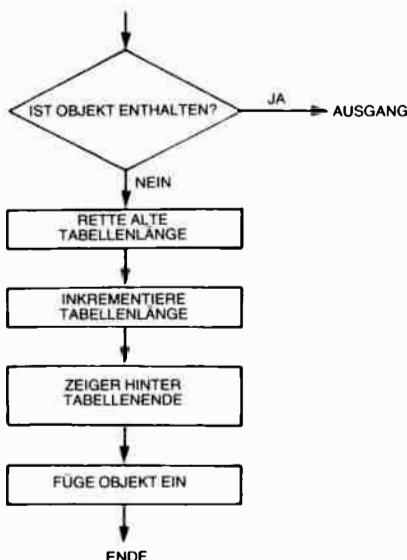

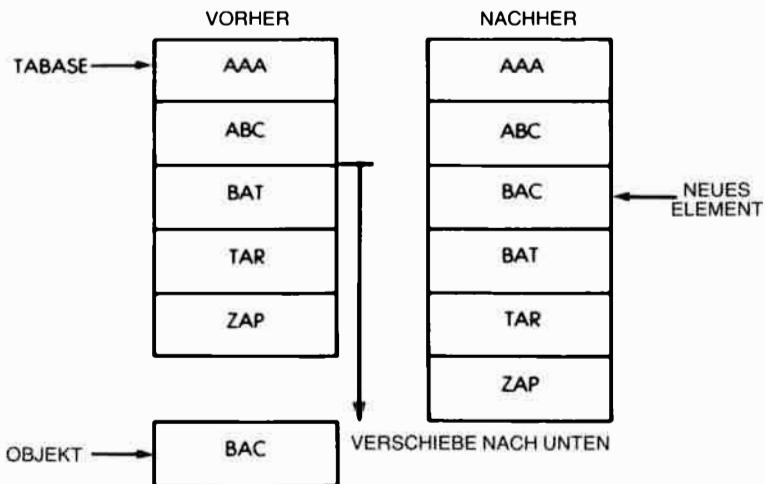

| Abb. 9.13: | Flußdiagramm zum Einfügen in die Tabelle       | 537 |

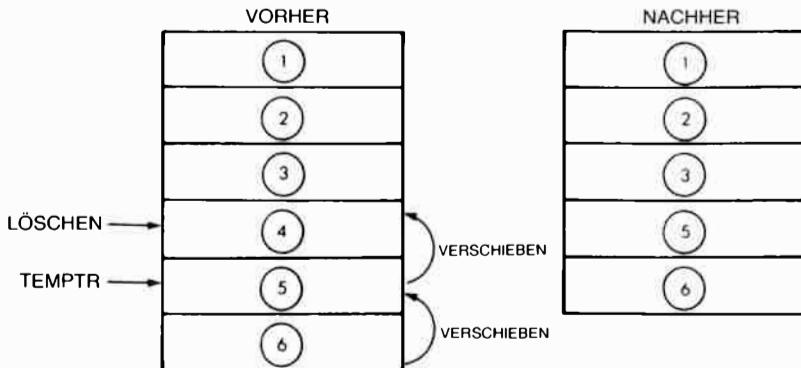

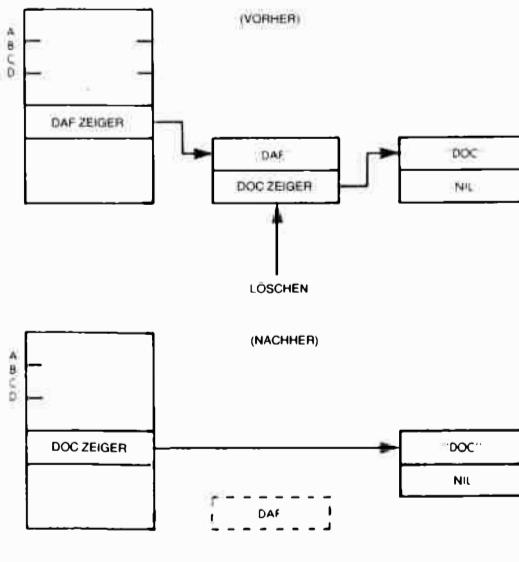

| Abb. 9.14: | Löschen einer Eintragung (einfache Liste)      | 538 |

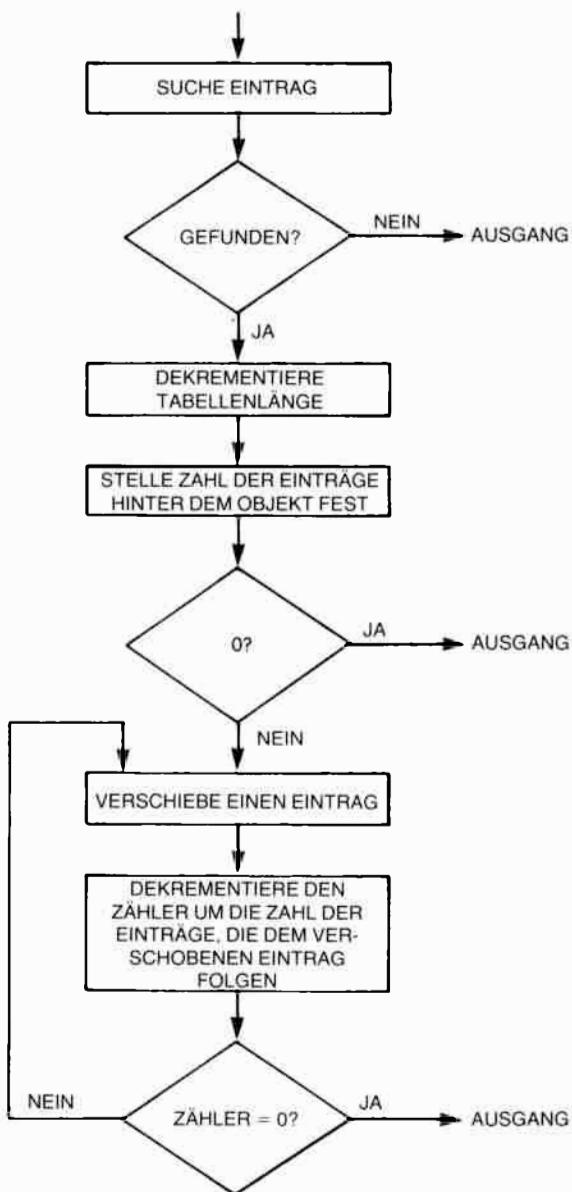

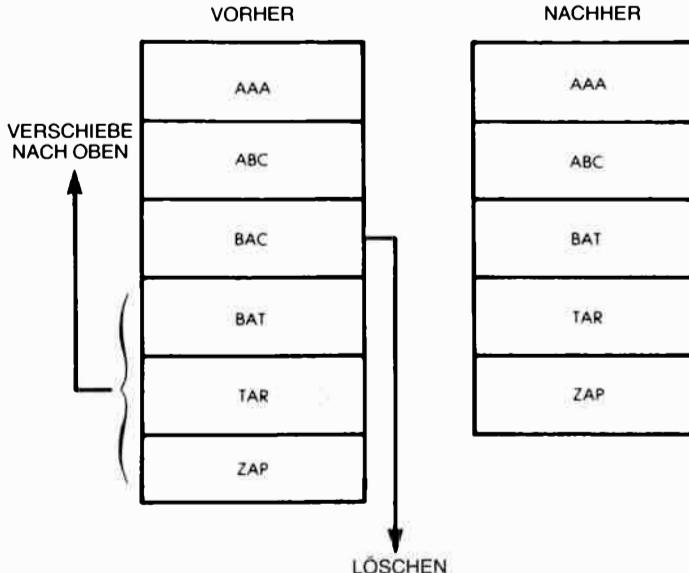

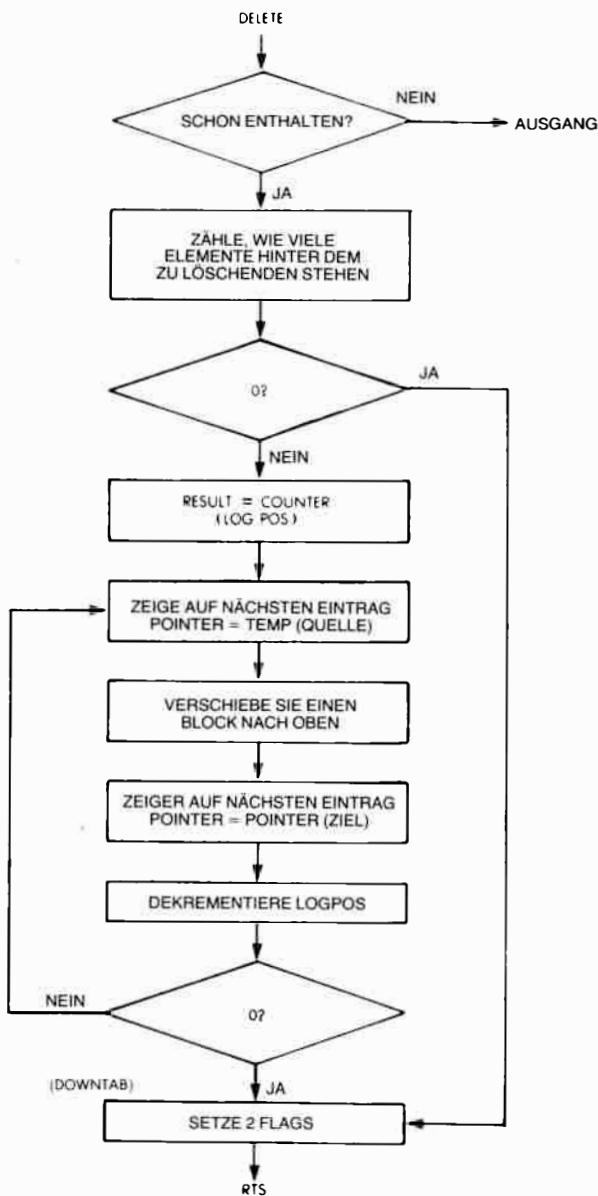

| Abb. 9.15: | Löschen in der Tabelle – Flußdiagramm          | 539 |

| Abb. 9.16: | Einfache Liste – die Programme                 | 540 |

| Abb. 9.17: | Einfache Liste – ein Durchlauf als Beispiel    | 541 |

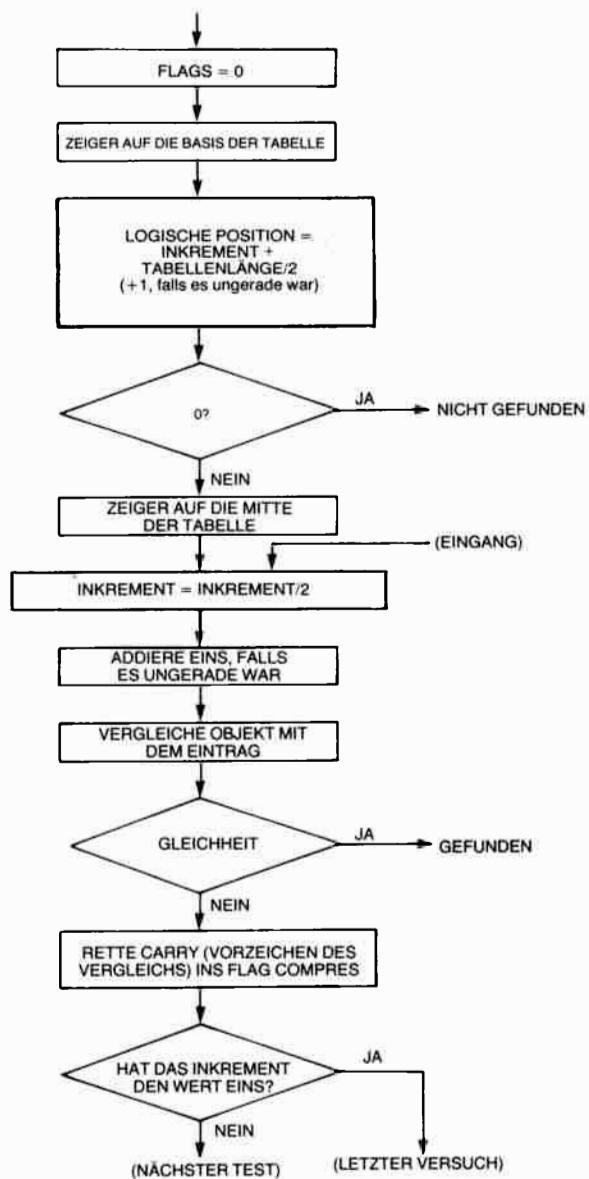

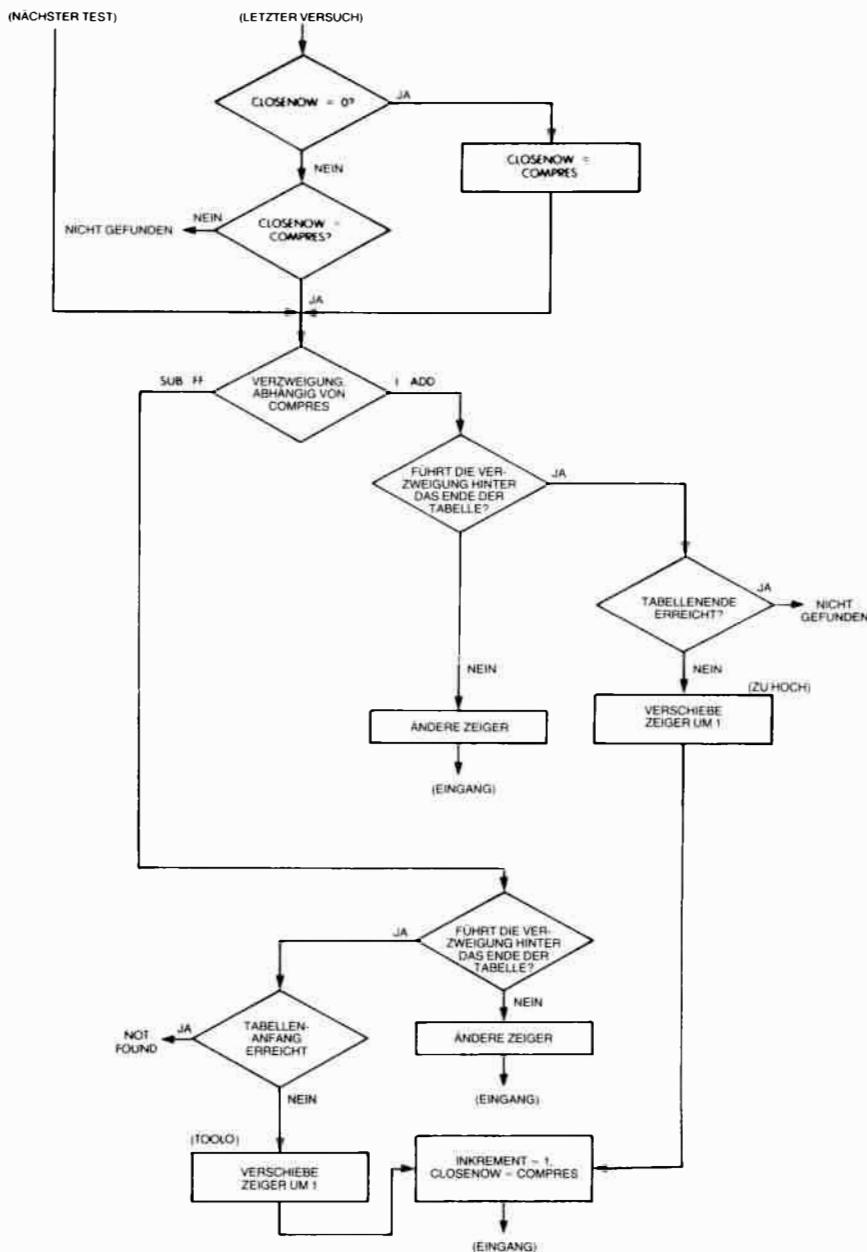

| Abb. 9.18: | Binäres Suchen – Flußdiagramm                  | 544 |

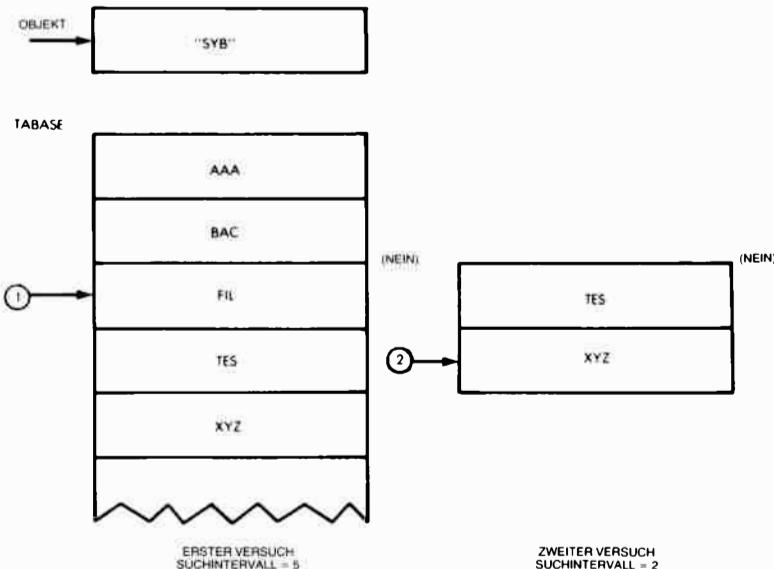

| Abb. 9.19: | Eine binäre Suche                              | 546 |

| Abb. 9.20: | Füge „BAC“ ein                                 | 548 |

| Abb. 9.21: | Lösche „BAC“                                   | 548 |

| Abb. 9.22: | Flußdiagramm zum Löschen (alphabetische Liste) | 549 |

| Abb. 9.23: | Binäres Suchprogramm                           | 550 |

| Abb. 9.24: | Alphabetische Liste – Ein Lauf als Beispiel    | 553 |

| Abb. 9.25: | Struktur der verketteten Liste                 | 555 |

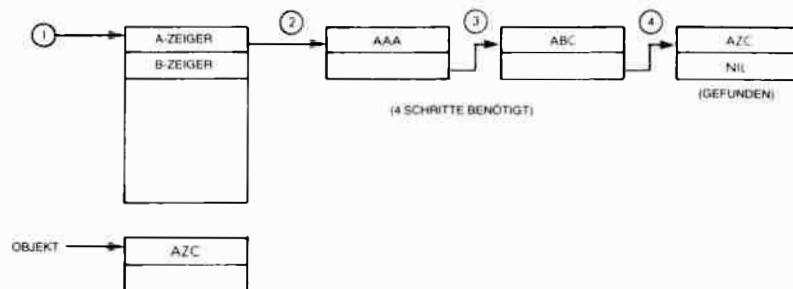

| Abb. 9.26: | Verkettete Liste – Eine Suche                  | 557 |

| Abb. 9.27: | Verkettete Liste: Beispiel des Einfügens       | 557 |

| Abb. 9.28: | Beispiel des Löschens (Verkettete Liste)       | 558 |

| Abb. 9.29: | Verkettete Liste – die Programme               | 559 |

| Abb. 9.30: | Verkettete Liste – ein Durchlauf               | 561 |

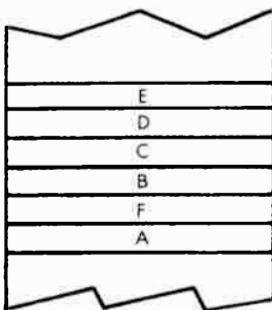

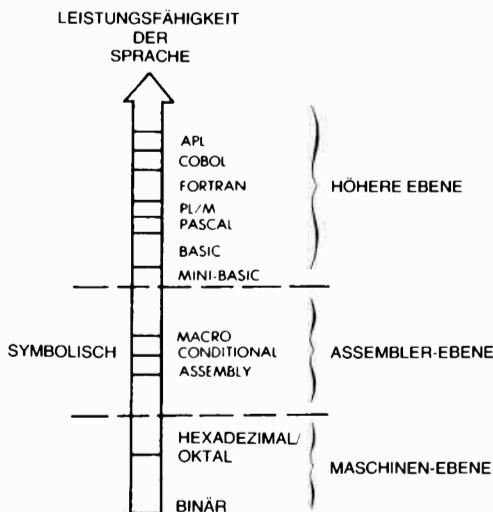

| Abb. 10.1: | Programmierebenen                              | 565 |

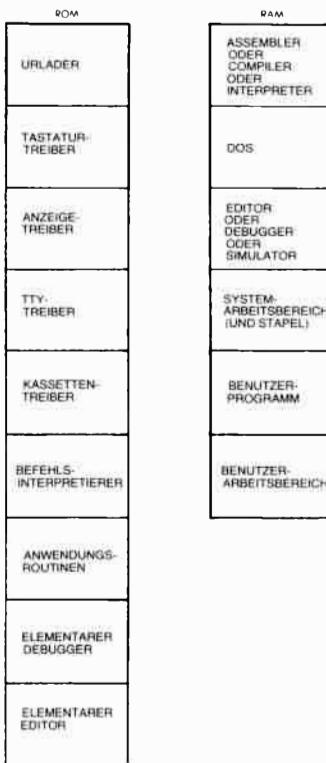

| Abb. 10.2: | Ein typischer Speicherbelegungsplan            | 570 |

| Abb. 10.3: | Programmierformular für einen Mikroprozessor   | 575 |

| Abb. 10.4: | Assemblerliste – ein Beispiel                  | 576 |

| Abb. 10.5: | Priorität der Operatoren                       | 580 |

# Vorwort

Dieses Buch wurde konzipiert als ein vollständiger in sich abgeschlossener Text zum Erlernen des Programmierens unter Verwendung des Z80. Es kann von allen gelesen werden, die auch bisher noch nicht programmiert haben. Von besonderem Wert sollte es für alle diejenigen sein, die den Z80 verwenden.

Für alle Leser, die schon programmiert haben, lehrt dieses Buch spezielle Programmiertechniken unter Verwendung der besonderen Eigenarten des Z80. Dieser Text deckt die Methoden elementarer bis mittlerer Schwierigkeit ab, die man braucht, um effektiv zu programmieren. Ziel dieses Textes ist es, demjenigen, der diesen Mikroprozessor verwenden will, fundierte Grundlagen zu liefern. Natürlich lehrt kein Buch wirklich zu programmieren, solange man es nicht tatsächlich tut. Es ist jedoch zu hoffen, daß dieses Buch den Leser zu einem Punkt führt, an dem er sich in der Lage fühlt, mit dem Programmieren selbst zu beginnen, und an dem er einfache oder auch etwas anspruchsvollere Probleme mit einem Mikroprozessor lösen kann.

Dieses Buch basiert auf der Erfahrung des Autors, der mehr als 1000 Personen gelehrt hat, wie man Mikrocomputer programmiert. Deshalb ist es konsequent strukturiert. Jedes Kapitel führt normalerweise von einfachen zu komplexeren Problemen. Leser, die die elementare Programmierung schon erlernt haben, können den Anfang eines Kapitels überspringen. Andere, die noch nie programmiert haben, müssen vielleicht die hinteren Abschnitte jedes Kapitels ein zweites Mal durcharbeiten. Das Buch wurde dazu entworfen, den Leser durch sämtliche grundlegende Konzepte und Techniken zu führen, die man für Programme wachsender Komplexität braucht. Deshalb sei es dringend empfohlen, die Reihenfolge der Kapitel einzuhalten. Um wirkliche Erfolge zu erzielen, ist es zusätzlich wichtig, daß der Leser versucht, so viele Aufgaben wie möglich zu lösen. Die Schwierigkeit der Aufgaben wurde sorgfältig abgestimmt. Sie dienen der Überprüfung, daß der behandelte Stoff auch wirklich verstanden wurde. Wenn man die Aufgaben nicht bearbeitet, dann kann man den Wert dieses Buchs als Lehrmittel nicht voll nutzen. Mehrere der Aufgaben können z. T. erhebliche Zeit beanspruchen, wie z. B. die Multiplikationsübung. Löst man jedoch auch diese Aufgaben, so lernt man Programmieren wirklich. Dies ist unerlässlich.

Für diejenigen, die am Ende dieses Buchs am Programmieren Geschmack gefunden haben, sei das Buch „Z80 Anwendungen“ von James W. Coffron (Ref.-Nr. 3037, August 1984) empfohlen.

Andere Bücher in dieser Serie behandeln die Programmierung anderer weit verbreiteter Mikroprozessoren.

Für diejenigen, die ihre Hardwarekenntnisse erweitern wollen, seien die Bücher „Chip und System: Einführung in die Mikroprozessoren-Technik“ (Ref.-Nr.: 3017) und „Mikroprozessor Interface Techniken“ (Ref.-Nr.: 3012) empfohlen.

Der Inhalt dieses Buchs wurde sorgfältig geprüft und sollte korrekt sein. Jedoch können trotzdem einige unvermeidliche Schreibfehler oder andere Irrtümer enthalten sein. Der Autor ist für alle Hinweise aufmerksamer Leser dankbar, so daß zukünftige Ausgaben von Ihren Erfahrungen profitieren können. Auch für andere Verbesserungsvorschläge (z. B. Programme, die von Lesern gewünscht, entwickelt oder für wichtig befunden werden) ist der Autor dankbar.

---

# 1

# Grundbegriffe

---

## Einführung

Dieses Kapitel soll in die Grundbegriffe und Bezeichnungen der Computerprogrammierung einführen. Der Leser, der mit diesen Begriffen schon vertaut ist, wird vielleicht den Inhalt dieses Kapitels nur flüchtig durchsehen und sich dann Kapitel 2 zuwenden. Es sei jedoch auch dem erfahrenen Leser empfohlen, den Inhalt dieses einführenden Kapitels genau anzusehen. Viele wichtige Begriffe werden hier erläutert, z. B. Zweierkomplement, BCD und andere Darstellungen. Einige dieser Begriffe sind für den Leser vielleicht neu, andere erweitern die Kenntnisse und Fähigkeiten auch des erfahrenen Programmierers.

## Was ist Programmierung?

Ist ein Problem gegeben, muß man zuerst eine Lösung finden. Diese Lösung in Form eines schrittweisen Verfahrens nennt man einen *Algorithmus*. Ein Algorithmus ist eine Vorschrift, nach der ein gegebenes Problem Schritt für Schritt gelöst wird. Er muß nach einer endlichen Zahl von Schritten zum Abschluß gebracht werden. Den Algorithmus kann man in einer beliebigen Sprache oder Symbolik darstellen. Ein einfaches Beispiel für einen Algorithmus ist:

1. Stecke den Schlüssel in das Schlüsselloch

2. Drehe den Schlüssel eine Umdrehung links herum

3. Fasse den Türdrücker an

4. Bewege den Türdrücker nach unten und drücke gegen die Tür.

Stimmt der Algorithmus für den vorliegenden Typ von Türschloß, wird sich die Tür jetzt öffnen. Diese Vorschrift aus vier Schritten beschreiben einen Algorithmus zum Öffnen einer Tür.

Sobald die Lösung für ein Problem in Form eines Algorithmus dargestellt ist, kann der Algorithmus von dem Computer abgearbeitet werden. Leider ist es eine feststehende Tatsache, daß Computer normales gesprochenes Deutsch (oder jede andere natürliche Sprache) weder verstehen noch ausführen können. Der Grund ist die *syntaktische Mehrdeutigkeit* aller natürlicher Sprachen. Nur eine wohldefinierte Teilmenge einer natürlichen Sprache kann von einem Computer „verstanden“ werden. Diese nennt man dann eine *Programmiersprache*.

Einen Algorithmus in eine Folge von Befehlen in einer Programmiersprache zu übersetzen, nennt man *Programmierung*. Genauer ausgedrückt heißt die Übersetzung des Algorithmus in die Programmiersprache *Kodierung*. Programmierung bezieht sich in Wirklichkeit nicht nur auf die Kodierung, sondern auf den gesamten Entwurf der Programme und der „Datenstrukturen“, die von dem Algorithmus benutzt werden. Effektive Programmierung setzt nicht nur voraus, daß man verschiedene Techniken zur Ausführung von Standardalgorithmen versteht, sondern auch daß man alle Hardwarehilfsmittel des Computers, wie interne Register, Speicher und peripherie Geräte, geschickt nutzt und die passenden Datenstrukturen kreativ einsetzt. Diese Techniken werden in den nächsten Kapiteln behandelt.

Programmierung verlangt auch eine konsequente Disziplin bei der Dokumentation, so daß die Programme für andere wie auch für den Autor verständlich sind. Zu einem Programm gehört sowohl eine interne als auch eine externe Dokumentation.

Interne Dokumentation bezieht sich auf Kommentare innerhalb des Programms, die sein Funktionieren erklären. Externe Dokumentation sind Unterlagen zum Entwurf, die vom Programm getrennt sind, wie schriftliche Erklärungen, Handbücher und Flußdiagramme.

### **Flußdiagramme**

Fast immer wird zwischen *Algorithmus* und *Programm* ein Zwischenschritt eingeschaltet, das *Flußdiagramm*. In einem Flußdiagramm wird der Algorithmus einfach als Folge von Rechtecken und Rauten, die die einzelnen Schritte des Algorithmus enthalten, symbolisch dargestellt. Rechtecke verwendet man für *Befehle* oder „ausführbare Anweisungen“, Rauten für *Verzweigungen* wie: Ist die Aussage X wahr, dann gehe nach A, sonst nach B. Statt jetzt eine formale Beschreibung von Flußdiagrammen zu bringen, werden wir Flußdiagramme später in diesem Buch einführen und diskutieren, wenn wir Programme erläutern.

Flußdiagramme werden dringend empfohlen als Zwischenschritt zwischen der Spezifikation des Algorithmus und der Kodierung der Lösung! Bemerkenswerterweise hat man herausgefunden, daß etwa 10% der Programmierer ein Programm erfolgreich schreiben können, ohne ein Flußdiagramm zu haben. Man hat aber auch herausgefunden, daß unglücklicherweise 90% der Programmierer meinen, sie gehörten zu diesen 10%! Das Ergebnis: Durchschnittlich 80% der Programme versagen, wenn sie zum ersten Mal auf einen Computer laufen sollen. (Die Prozentangaben sind natürlich nicht exakt.) Kurz gesagt, die meisten Programmiererneulinge sehen die Notwendigkeit, ein Flußdiagramm zu zeichnen, nur selten ein. Dies führt üblicherweise zu „unsauberer“ oder fehlerhaften Programmen. Sie verbrauchen dann viel Zeit beim Testen und Korrigieren ihrer Programme (das nennt man dann *Debugging*). Flußdiagramme zu zeichnen, sei deshalb in allen Fällen dringend emp-

fohlen. Dazu braucht man vor der Kodierung nur wenig zusätzliche Zeit, erhält aber normalerweise ein klares Programm, das richtig und schnell funktioniert. Sind die Flußdiagramme einmal gut verstanden, dann wird ein kleiner Prozentsatz der Programmierer in der Lage sein, diesen Schritt im Geiste auszuführen, ohne ihn zu Papier zu bringen. Leider sind dann die Programme, die sie schreiben, für andere meist nur schwer zu verstehen, weil die Dokumentation durch die Flußdiagramme fehlt. Deshalb wird allgemein empfohlen, das Verfahren der Flußdiagramme bei allen wichtigen Programmen konsequent anzuwenden. Viele Beispiele werden das ganze Buch hindurch vorgestellt werden.

Abb. 1.1: Flußdiagramm zur Konstanthaltung der Raumtemperatur

## Darstellung von Information

Alle Computer handhaben Informationen in Form von Zahlen oder in Form von Zeichen. Wir wollen hier die externe und die interne Darstellung von Information in einem Computer untersuchen.

### Interne Darstellung von Information

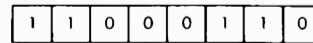

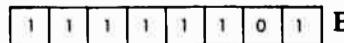

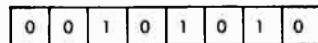

In einem Computer wird jede Information als Gruppe von Bits dargestellt. Bit ist die Abkürzung von binary digit, d. h. *Binärziffer* („0“ oder „1“). Eingeschränkt durch die Eigenschaften der üblichen Elektronik, verwendet die einzige praktikable Darstellung von Information eine Logik aus zwei Zuständen (die Darstellung der Zustände „0“ und „1“). Die zwei Zustände der Schaltungen, die in der digitalen Elektronik verwendet werden, sind allgemein „ein“ und „aus“, und diese werden durch die

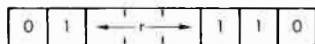

Symbole „0“ und „1“ logisch dargestellt. Weil diese Schaltungen verwendet werden, um „logische“ Funktionen auszuführen, nennt man sie „binäre Logik“. Als Ergebnis davon wird heute tatsächlich die gesamte Informationsverarbeitung in binärem Format ausgeführt. Bei den Mikroprozessoren im allgemeinen und beim Z80 im besonderen sind diese Bits in Achtergruppen strukturiert. Eine Gruppe von acht Bit nennt man ein *Byte*, eine Gruppe von vier Bit nennt man ein *Nibble*.

Wir wollen jetzt untersuchen, wie Information intern im Binärformat dargestellt wird. Zwei Bereiche müssen dabei innerhalb des Rechners unterschieden werden. Der erste ist das Programm, d. h. eine Folge von Befehlen. Der Zweite sind die Daten, mit denen das Programm arbeitet, und die Zahlen oder alphanumerischen Text enthalten können. Wir werden jetzt folgende drei Darstellungen von Information diskutieren: Programme, Zahlen und alphanumerische Daten.

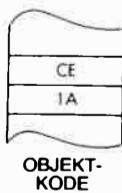

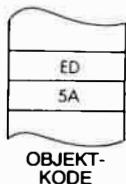

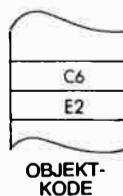

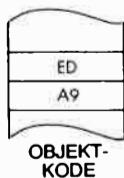

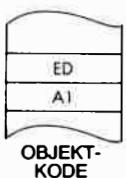

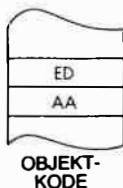

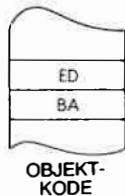

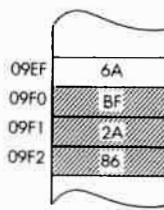

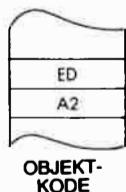

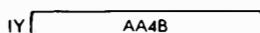

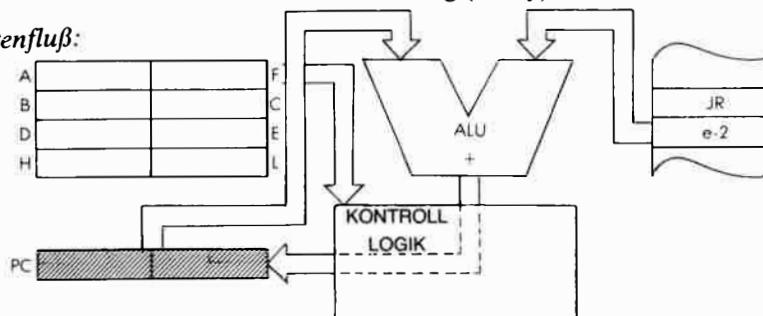

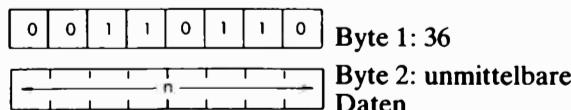

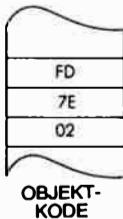

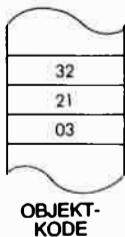

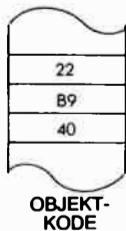

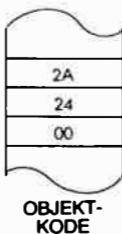

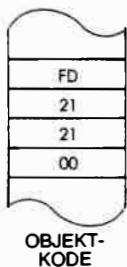

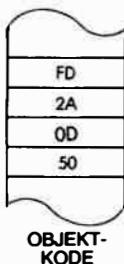

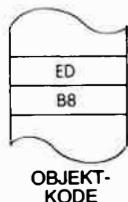

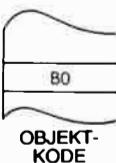

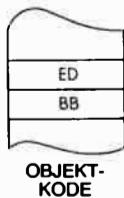

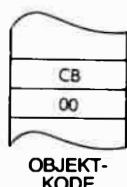

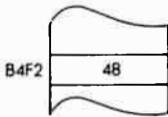

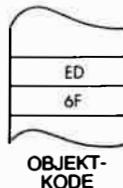

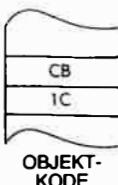

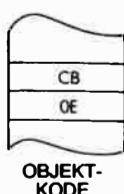

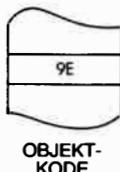

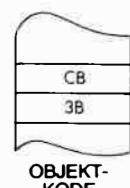

### *Darstellung von Programmen*

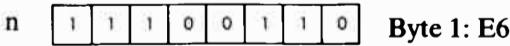

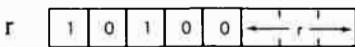

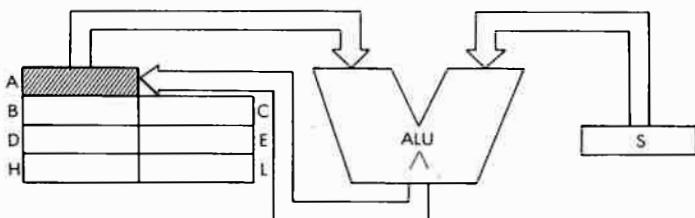

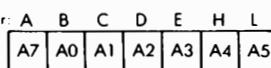

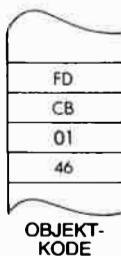

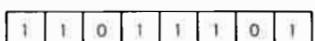

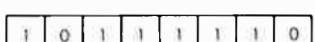

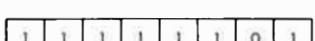

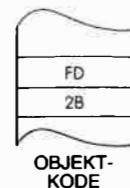

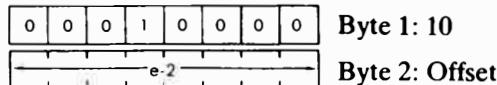

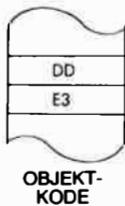

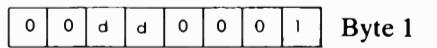

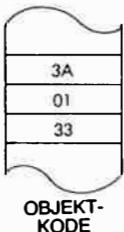

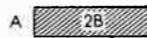

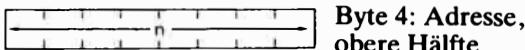

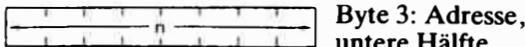

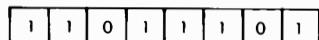

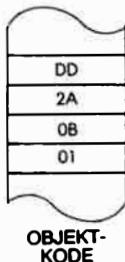

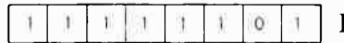

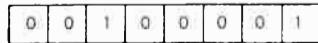

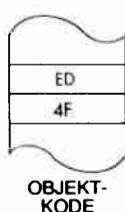

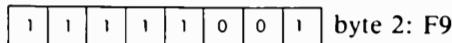

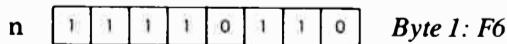

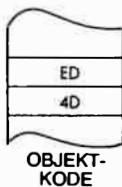

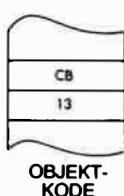

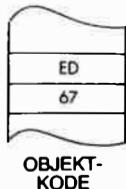

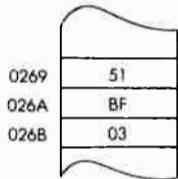

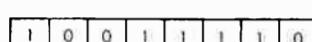

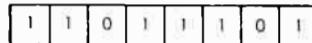

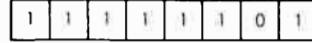

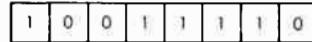

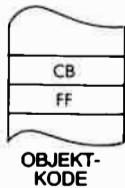

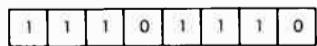

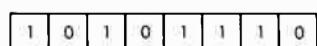

Alle Befehle werden intern durch ein oder mehrere Byte dargestellt. Ein sogenannter „Kurzbefehl“ besteht aus einem einzelnen Byte. Ein langerer Befehl besteht aus zwei oder mehr Bytes. Da der Z80 ein Acht-Bit-Mikroprozessor ist, holt er Byte für Byte nacheinander aus dem Speicher. Deshalb kann ein Ein-Byte-Befehl immer schneller ausgeführt werden, als ein Zwei- oder Drei-Byte-Befehl. Wir werden später sehen, daß dies ein entscheidendes Merkmal für den Befehlssatz jedes Mikroprozessors und damit auch des Z80 ist, bei dem besonderer Aufwand getrieben wurde, möglichst viele Ein-Byte-Befehle zur Verfügung zu stellen, um die Leistungsfähigkeit bei der Programmausführung zu verbessern. Die Begrenzung auf eine Länge von acht Bit hat jedoch zu wichtigen Einschränkungen geführt, die später herausgestellt werden sollen. Dies ist ein klassisches Beispiel für den Kompromiß zwischen Geschwindigkeit und Flexibilität bei der Programmierung. Der binäre Code zur Darstellung der Befehle ist vom Hersteller vorgeschrieben. Wie jeder andere Mikroprozessor wird der Z80 mit einem festen Befehlssatz geliefert. Diese Befehle sind vom Hersteller definiert und werden am Ende des Buches mit dem zugehörigen Code aufgelistet. Jedes Programm wird durch eine Folge dieser binären Befehle gebildet. Die Z80-Befehle werden in Kapitel 4 vorgestellt.

### *Darstellung numerischer Daten*

Die Darstellung von Zahlen ist nicht ganz einfach und man muß verschiedene Fälle unterscheiden. Zuerst müssen wir ganze, dann vorzeichenbehaftete, d. h. positive und negative Zahlen, und schließlich Dezimalzahlen darstellen können. Jetzt wollen wir diese Bedingungen und mögliche Lösungen ansprechen.

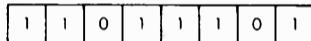

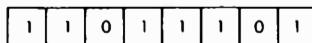

Ganze Zahlen kann man dual darstellen. Die duale Form ist einfach die Darstellung des Zahlenwertes im Dualsystem. Im Dualsystem repräsent-

tiert das Bit ganz rechts 2 hoch 0. Das nächste Bit links repräsentiert 2 hoch 1, das nächste 2 hoch 2 und das Bit ganz links 2 hoch 7 = 128.

$b_7 b_6 b_5 b_4 b_3 b_2 b_1 b_0$  bedeutet

$$b_7 \cdot 2^7 + b_6 \cdot 2^6 + b_5 \cdot 2^5 + b_4 \cdot 2^4 + b_3 \cdot 2^3 + b_2 \cdot 2^2 + b_1 \cdot 2^1 + b_0 \cdot 2^0$$

Die Potenzen von 2 sind:

$$2^7 = 128, 2^6 = 64, 2^5 = 32, 2^4 = 16, 2^3 = 8, 2^2 = 4, 2^1 = 2, 2^0 = 1$$

Die duale Darstellung entspricht der dezimalen Zahlendarstellung, in der z. B. „123“ bedeutet:

$$\begin{array}{r} 1 \times 100 = 100 \\ + 2 \times 10 = 20 \\ + 3 \times 1 = 3 \\ \hline = 123 \end{array}$$

Beachten Sie, daß  $100 = 10^2$ ,  $10 = 10^1$  und  $1 = 10^0$ .

In diesem „Stellenwertsystem“ bedeutet jede Ziffer eine Zehnerpotenz. Im Dualsystem repräsentiert jede Binärziffer oder jedes „Bit“ eine Zweierpotenz statt einer Zehnerpotenz im Dezimalsystem.

Beispiel: „00001001“ dual bedeutet:

$$\begin{array}{r} 1 \times 1 = 1 \quad (2^0) \\ 0 \times 2 = 0 \quad (2^1) \\ 0 \times 4 = 0 \quad (2^2) \\ 1 \times 8 = 8 \quad (2^3) \\ 0 \times 16 = 0 \quad (2^4) \\ 0 \times 32 = 0 \quad (2^5) \\ 0 \times 64 = 0 \quad (2^6) \\ 0 \times 128 = 0 \quad (2^7) \\ \hline \end{array}$$

dezimal 9

Wir wollen einige weitere Beispiele untersuchen:

„10000001“ bedeutet:

$$\begin{array}{r} 1 \times 1 = 1 \\ 0 \times 2 = 0 \\ 0 \times 4 = 0 \\ 0 \times 8 = 0 \\ 0 \times 16 = 0 \\ 0 \times 32 = 0 \\ 0 \times 64 = 0 \\ 1 \times 128 = 128 \\ \hline \end{array}$$

dezimal 129

„10000001“ bedeutet also dezimal 129.

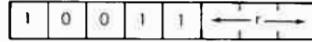

Wenn Sie die duale Zahlendarstellung untersuchen, dann werden Sie verstehen, warum die Bits von rechts nach links von 0 bis 7 durchnummieriert sind. Bit 0 ist „ $b_0$ “ und entspricht  $2^0$ . Bit 1 ist „ $b_1$ “ und entspricht  $2^1$  usw.

| Dezimal | Dual     | Dezimal | Dual     |

|---------|----------|---------|----------|

| 0       | 00000000 | 32      | 00100000 |

| 1       | 00000001 | 33      | 00100001 |

| 2       | 00000010 | .       |          |

| 3       | 00000011 | .       |          |

| 4       | 00000100 | .       |          |

| 5       | 00000101 | 63      | 00111111 |

| 6       | 00000110 | 64      | 01000000 |

| 7       | 00000111 | 65      | 01000001 |

| 8       | 00001000 | .       |          |

| 9       | 00001001 | .       |          |

| 10      | 00001010 | 127     | 01111111 |

| 11      | 00001011 | 128     | 10000000 |

| 12      | 00001100 | 129     | 10000001 |

| 13      | 00001101 | .       |          |

| 14      | 00001110 | .       |          |

| 15      | 00001111 | .       |          |

| 16      | 00010000 | .       |          |

| 17      | 00010001 | .       |          |

| .       |          |         |          |

| .       |          |         |          |

| .       |          |         |          |

| 31      | 00011111 | 254     | 11111110 |

|         |          | 255     | 11111111 |

Abb. 1.2: Dezimal-Dual Tabelle

Die dualen Äquivalente der Dezimalzahlen 0 bis 255 sind in Abb. 1–2 aufgelistet.

*Aufgabe 1.1:* Welchen Wert hat „11111100“ in dezimaler Darstellung?

### Dezimal nach Dual

Umgekehrt wollen wir jetzt das duale Äquivalent von dezimal „11“ berechnen:

$$11 : 2 = 5 \text{ Rest } 1 \downarrow 1 \text{ (niederwertigstes Bit)}$$

$$5 : 2 = 2 \text{ Rest } 1 \downarrow 1$$

$$2 : 2 = 1 \text{ Rest } 0 \downarrow 0$$

$$1 : 2 = 0 \text{ Rest } 1 \downarrow 1 \text{ (höchstwertiges Bit)}$$

Das duale Äquivalent ist 1011 (dazu wird die Spalte ganz rechts von unten nach oben gelesen).

Das duale Äquivalent einer Dezimalzahl ergibt sich, indem man wiederholt durch 2 dividiert, bis man den Quotienten 0 erhält.

*Aufgabe 1.2:* Was ist 257 dual?

*Aufgabe 1.3:* Wandle 19 nach dual, dann zurück nach dezimal.

### Rechnen mit Dualzahlen

Die Rechenregeln für Dualzahlen sind einfach. Die Regeln für die Addition sind:

$$\begin{array}{rcl} 0 + 0 & = & 0 \\ 0 + 1 & = & 1 \\ 1 + 0 & = & 1 \\ 1 + 1 & = & (1)0 \end{array}$$

Hierbei bedeutet (1) einen Übertrag (carry) von 1 (beachten Sie, daß „10“ das duale Äquivalent von dezimal „2“ ist). Duale Subtraktion führt man aus durch „Addition des Komplements“. Sie wird später erklärt, wenn wir die Darstellung negativer Zahlen lernen.

Beispiel:

$$\begin{array}{rcl} & (2) & 10 \\ & + (1) & + 01 \\ \hline & (3) & 11 \end{array}$$

Wie im Dezimalsystem addiert man auch Dualzahlen, indem man rechts beginnend spaltenweise addiert.

Addition der rechten Spalte:

$$\begin{array}{rcl} & 10 \\ & + 01 \\ \hline (0+1=1 & \text{kein Übertrag}) \end{array}$$

Addition der nächsten Spalte:

$$\begin{array}{rcl} & 10 \\ & + 01 \\ \hline 11 & (1+0=1, \text{kein Übertrag}) \end{array}$$

*Aufgabe 1.4:* Berechne 5 + 10 dual. Überprüfe, daß das Ergebnis 15 ist.

Einige weitere Beispiele dualer Addition:

$$\begin{array}{rcl} 0010 & (2) & 0011 & (3) \\ + 0001 & (1) & + 0001 & (1) \\ \hline = 0011 & (3) & = 0100 & (4) \end{array}$$

Das letzte Beispiel veranschaulicht die Rolle des Übertrags.

Wenn wir die Bits ganz rechts betrachten:

$$1 + 1 = (1)0$$

Es tritt ein Übertrag von 1 auf, der zu den nächsten Bits addiert werden muß:

$$\begin{array}{r} 001 \quad - \text{ Spalte 0 wurde schon addiert} \\ + 000 \quad - \\ + \quad 1 \quad - \text{ Übertrag} \\ \hline \end{array}$$

$= (1)0 \quad - (1)$  zeigt einen neuen Übertrag in Spalte 2 an.

Das Endergebnis: 0100

Ein anderes Beispiel:

$$\begin{array}{r} 0111 \quad (7) \\ + 0011 \quad (3) \\ = 1010 \quad (10) \end{array}$$

In diesem Beispiel tritt wieder ein Übertrag auf, bis hin zur Spalte ganz links.

*Aufgabe 1.5:* Berechne das Ergebnis von

$$\begin{array}{r} 1111 \\ + 0001 \\ \hline = \quad ? \end{array}$$

Paßt das Ergebnis in vier Bit?

Mit acht Bit ist es demnach möglich, die Zahlen „00000000“ bis „11111111“, d. h. „0“ bis „255“, direkt darzustellen. Zwei Einschränkungen sollten wir uns dabei sofort verdeutlichen. Erstens stellen wir nur positive Zahlen dar, und zweitens ist die Größe der Zahlen auf 255 begrenzt, wenn wir nur acht Bit verwenden. Wir wollen jetzt diese beiden Probleme nacheinander ansprechen.

### Vorzeichenbehaftete Dualdarstellung

In der vorzeichenbehafteten Dualdarstellung verwendet man das Bit ganz links, um das Vorzeichen der Zahl zu kennzeichnen. Üblicherweise kennzeichnet man eine *positive* Zahl mit „0“, eine *negative* mit „1“. Jetzt bedeutet „11111111“ – 127, während „01111111“ +127 bedeutet. Wir können jetzt positive und negative Zahlen darstellen, der Betrag der Zahlen ist aber auf maximal 127 begrenzt.

Beispiel: „0000 0001“ bedeutet +1 (die führende „0“ ist „+“, gefolgt von „000 0001“ = 1). „1000 0001“ ist –1 (die führende „1“ ist „–“).

*Aufgabe 1.6:* Was ist –5 in vorzeichenbehafteter Dualdarstellung?

Jetzt wollen wir über das Problem der Größe sprechen: Um größere Zahlen darzustellen, wird es nötig sein, eine größere Anzahl Bits zu verwenden. Wenn wir zum Beispiel sechzehn Bit (zwei Byte) verwenden, können wir Zahlen von –32k bis +32k in dualer Form mit Vorzeichen darstellen (im Computerjargon bedeutet 1k 1024). Bit 15 wird für das Vorzeichen verwendet und die restlichen 15 Bit (Bit 14 bis Bit 0) für den

Betrag der Zahl:  $2^{15} = 32k$ . Ist dieser Betrag immer noch zu klein, wird man drei oder mehr Byte verwenden. Wenn wir große ganze Zahlen darstellen wollen, dann ist es nötig, intern eine größere Zahl von Bytes zu verwenden. Deshalb stellen die meisten einfachen BASIC-Versionen und andere Sprachen für ganze Zahlen nur eine beschränkte Genauigkeit zur Verfügung. So können sie für die Zahlen, mit denen sie arbeiten, ein kürzeres internes Format verwenden. Bessere Versionen von BASIC oder von anderen Sprachen rechnen mit zusätzlichen signifikanten Dezimalstellen auf Kosten einer größeren Anzahl Bytes für jede Zahl.

Jetzt wollen wir uns um ein anderes Problem kümmern, nämlich das der möglichst effektiven Verarbeitungsgeschwindigkeit. Wir versuchen, eine Addition in der vorzeichenbehafteten Dualdarstellung, die wir dargestellt haben, auszuführen. Wir wollen „-5“ und „+7“ addieren.

$$\begin{array}{rcl} +7 \text{ wird dargestellt durch} & 00000111 \\ -5 \text{ wird dargestellt durch} & 10000101 \end{array}$$

---

Die duale Summe ist: 10001100 oder -12.

Dies ist jedoch nicht das richtige Ergebnis. Das richtige Ergebnis wäre +2. Um diese Darstellung richtig zu gebrauchen, muß man spezielle Maßnahmen ergreifen, die vom Vorzeichen abhängen. Dies führt zu größeren Schwierigkeiten und zu geringerer Effektivität. Mit anderen Worten: Die duale Addition vorzeichenbehafteter Zahlen funktioniert nicht richtig. Dies ist natürlich sehr ärgerlich, denn der Computer soll Information ja nicht nur darstellen, sondern auch damit rechnen.

Die Lösung dieses Problems ist die Darstellung als Zweierkomplement, die man statt der vorzeichenbehafteten Dualdarstellung verwendet. Vor Einführung des *Zweierkomplements* wollen wir erst einen Zwischen- schritt betrachten, das *Einerkomplement*.

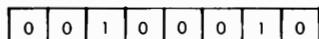

### *Einerkomplement*

In der Darstellung als Einerkomplement erscheinen alle positiven ganzen Zahlen in ihrer korrekten dualen Form. Beispielsweise wird „+3“ wie üblich als 00000011 dargestellt. Das Komplement „-3“ erhält man jedoch dadurch, daß man jedes einzelne Bit invertiert. Jede 0 wird in eine 1 und jede 1 in eine 0 geändert. In unserem Beispiel ist „-3“ dargestellt als Einerkomplement 11111100.

Ein anderes Beispiel:

$$\begin{array}{l} +2 \text{ ist } 00000010 \\ -2 \text{ ist } 11111101 \end{array}$$

Beachten Sie, daß positive Zahlen in dieser Darstellung links mit einer „0“, negative links mit einer „1“ beginnen.

*Aufgabe 1.7:* Die Darstellung von „+6“ ist „00000110“. Was ist die Darstellung von „-6“ als Einerkomplement?

Als Test wollen wir minus 4 und plus 6 addieren:

$$\begin{array}{r} -4 \text{ ist } 11111011 \\ +6 \text{ ist } 00000110 \end{array}$$

---

Die Summe ist: (1) 00000001, wobei (1) einen Übertrag anzeigt.

Das richtige Ergebnis wäre „2“ oder „00000010“.

Ein weiterer Versuch:

$$\begin{array}{r} -3 \text{ ist } 11111100 \\ -2 \text{ ist } 11111101 \end{array}$$

---

Die Summe ist: (1)11111001

oder „1“ und ein Übertrag. Das richtige Ergebnis wäre „–5“. Die Darstellung von „–5“ ist 11111010. Es funktionierte also nicht.

In der beschriebenen Form sind positive und negative Zahlen darstellbar. Das Ergebnis einer normalen Addition kommt jedoch nicht immer „richtig“ heraus. Deshalb werden wir noch eine andere Darstellung verwenden. Sie entsteht aus dem Einerkomplement und wird Zweierkomplement genannt.

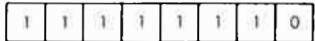

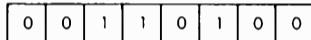

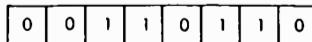

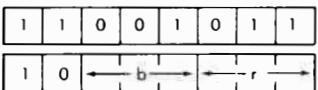

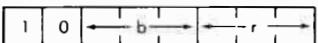

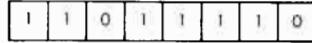

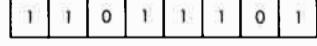

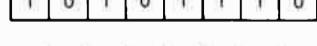

### Zweierkomplement

Beim Zweierkomplement werden positive Zahlen immer noch wie üblich vorzeichenbehaftet dual dargestellt, genau wie beim Einerkomplement. Der Unterschied liegt in der Darstellung *negativer Zahlen*. Eine negative Zahl im Zweierkomplement erhält man, indem man zuerst das Einerkomplement berechnet und dann *eins addiert*. Wir wollen dies an einem Beispiel illustrieren:

+3 ist in vorzeichenbehafteter Dualdarstellung 00000011. Das Einerkomplement davon ist 11111100. Durch Addition von Eins erhält man das Zweierkomplement 11111101.

Wir wollen eine Addition ausprobieren:

$$\begin{array}{r} (3) \quad 00000011 \\ +(5) \quad +00000101 \\ \hline = (8) \quad = 00001000 \end{array}$$

---

Das Ergebnis stimmt.

Jetzt wollen wir die Subtraktion ausprobieren:

$$\begin{array}{r} (3) \quad 00000011 \\ (-5) \quad +11111011 \\ \hline = 11111100 \end{array}$$

---

Wir prüfen das Ergebnis, indem wir das Zweierkomplement berechnen:

Das Einerkomplement von 1111110 ist 00000001

Addition von 1 + 1

---

Das Zweierkomplement ist also 00000010 oder +2.

Unser Ergebnis oben, „1111110“ stellt „–2“ dar. Es ist richtig!

Wir haben jetzt Addition und Subtraktion ausprobiert und die Ergebnisse waren richtig (wobei wir den Übertrag nicht beachtet haben). Es scheint, als ob das Zweierkomplement funktioniert!

*Aufgabe 1.8:* Was ist die Zweierkomplement-Darstellung von 127?

*Aufgabe 1.9:* Was ist die Zweierkomplement-Darstellung von -128?

Wir wollen jetzt +4 und -3 addieren (die Subtraktion wird ausgeführt, indem man das Zweierkomplement addiert):

$$\begin{array}{r} +4 \text{ ist } 00000100 \\ -3 \text{ ist } 11111101 \end{array}$$

---

Das Ergebnis ist: (1) 00000001

Wenn wir den Übertrag nicht beachten, ist das Ergebnis 00000001, d. h. dezimal „1“. Dies ist das richtige Ergebnis. Ohne einen vollständigen mathematischen Beweis zu geben, wollen wir einfach feststellen, daß diese Darstellung funktioniert. In der Darstellung als Zweierkomplement ist es möglich, vorzeichenbehaftete Zahlen zu addieren oder zu subtrahieren, ohne das Vorzeichen zu beachten. Wenn man die gebräuchlichen Regeln der dualen Addition anwendet, kommt das Ergebnis einschließlich des Vorzeichens richtig heraus. Ein Übertrag wird nicht beachtet. Dies ist ein wesentlicher Vorteil. Wäre das nicht der Fall, müßte man das Vorzeichen des Ergebnisses immer korrigieren, was Addition und Subtraktion wesentlich verlangsamen würde.

Der Vollständigkeit halber wollen wir feststellen, daß das Zweierkomplement die gebäuchlichste Darstellung für einfache Prozessoren wie Mikroprozessoren ist. Für komplexe Prozessoren mag man andere Darstellungen verwenden. Man kann z. B. das Einerkomplement verwenden, benötigt aber spezielle Schaltungen, um das Ergebnis zu „berichten“.

Von jetzt an werden alle vorzeichenbehafteten ganzen Zahlen stillschweigend als Zweierkomplemente dargestellt werden. Abb. 1.3 enthält eine Tabelle von Zweierkomplementen.

*Aufgabe 1.10:* Was sind die kleinste und die größte Zahl, die man als Zweierkomplement darstellen kann, wenn man nur ein Byte verwendet?

*Aufgabe 1.11:* Berechne das Zweierkomplement von 20. Berechne dann das Zweierkomplement des Ergebnisses. Ergibt sich wieder 20?

Das folgende Beispiel dient dazu, die Regeln für das Zweierkomplement verständlich zu machen. Insbesondere kennzeichnet C einen möglichen Übertrag. (C ist Bit 8 des Ergebnisses.)

V kennzeichnet einen Überlauf des Zweierkomplements, z. B. wenn das Vorzeichen „versehentlich“ verändert wird, weil die Zahlen zu groß sind. Es ist ein wichtiger interner Übertrag von Bit 6 nach Bit 7 (dem Vorzeichenbit). Dies wird weiter unten erklärt.

| +<br>2er-Komplement<br>Kode | -<br>2er-Komplement<br>Kode |

|-----------------------------|-----------------------------|

| + 127                       | 01111111                    |

| + 126                       | 01111110                    |

| + 125                       | 01111101                    |

| • • •                       | • • •                       |

| + 65                        | 01000001                    |

| + 64                        | 01000000                    |

| + 63                        | 00111111                    |

| • • •                       | • • •                       |

| + 33                        | 00100001                    |

| + 32                        | 00100000                    |

| + 31                        | 00011111                    |

| • • •                       | • • •                       |

| + 17                        | 00010001                    |

| + 16                        | 00010000                    |

| + 15                        | 00001111                    |

| + 14                        | 00001110                    |

| + 13                        | 00001101                    |

| + 12                        | 00001100                    |

| + 11                        | 00001011                    |

| + 10                        | 00001010                    |

| + 9                         | 00001001                    |

| + 8                         | 00001000                    |

| + 7                         | 00000111                    |

| + 6                         | 00000110                    |

| + 5                         | 00000101                    |

| + 4                         | 00000100                    |

| + 3                         | 00000011                    |

| + 2                         | 00000010                    |

| + 1                         | 00000001                    |

| + 0                         | 00000000                    |

Abb. 1.3: Tabelle der Zweierkomplemente

Wir wollen jetzt die Rolle des Übertrags „C“ und des Überlaufs „V“ demonstrieren.

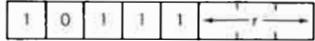

### *Der Übertrag C*

Hier ist ein Beispiel für einen Übertrag:

$$\begin{array}{r}

(128) & 10000000 \\

+(129) & +10000001 \\

\hline

(257) = (1) & 00000001

\end{array}$$

wobei (1) einen Übertrag anzeigt.

Das Ergebnis erfordert ein neuntes Bit (Bit „8“, denn das Bit ganz rechts ist Bit „0“). Es ist das Übertragsbit.

Wenn wir annehmen, daß das Übertragsbit das neunte Bit des Ergebnisses ist, erkennen wir das Ergebnis als  $100000001 = 257$ .

Allerdings muß man das Übertragsbit mit Sorgfalt identifizieren und behandeln. Intern im Mikroprozessor sind die Register, in denen das Ergebnis gespeichert wird, allgemein nur acht Bit lang. Wenn das Ergebnis gespeichert wird, bleiben nur die Bits 0 bis 7 erhalten.

Deshalb bedarf ein Übertrag immer einer besonderen Behandlung: er muß mit speziellen Befehlen erkannt und dann bearbeitet werden. Bearbeitung des Übertrags heißt entweder, ihn irgendwo zu speichern (mit einem speziellen Befehl), ihn nicht zu beachten oder zu entscheiden, daß ein Fehler aufgetreten ist (wenn das größte zulässige Ergebnis „11111111“ ist).

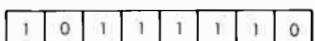

### *Überlauf V*

Hier ist ein Beispiel für einen Überlauf:

$$\begin{array}{r}

\text{Bit 6} \\

\text{Bit 7}

\end{array}

\begin{array}{c}

\downarrow \\

\hline

01000000 & (64) \\

+01000001 & +(65) \\

\hline

=10000001 & =(-127)

\end{array}$$

Es wurde ein interner Übertrag von Bit 6 nach Bit 7 erzeugt. Dies nennt man einen Überlauf.

Das Ergebnis ist jetzt „versehentlich“ negativ. Diese Situation muß erkannt werden, so daß man sie korrigieren kann.

Wir wollen einen anderen Fall überprüfen:

$$\begin{array}{r}

11111111 & (-1) \\

+11111111 & +(-1) \\

\hline

=(1) & 11111110 =(-2)

\end{array}$$

↓

Übertrag

In diesem Fall trat ein interner Übertrag von Bit 6 nach Bit 7 auf und ebenso von Bit 7 nach Bit 8 (der formelle Übertrag C, den wir im vorhergehenden Abschnitt untersucht haben). Die Rechenregeln für Zweierkomplemente sagen, daß dieser Übertrag nicht beachtet werden soll. Dann ist das Ergebnis richtig.

Dies ist der Fall, weil der Übertrag von Bit 6 nach Bit 7 das Vorzeichenbit nicht verändert hat.

Dies ist dann kein *Überlauf*. Wenn man mit negativen Zahlen rechnet, ist ein Überlauf nicht ein einfacher Übertrag von Bit 6 nach Bit 7. Wir wollen ein weiteres Beispiel überprüfen:

$$\begin{array}{r}

11000000 \quad (-64) \\

+10111111 \quad (-65) \\

\hline

=(1) \quad 01111111 \quad (+127)

\end{array}$$

↓

Übertrag

In diesem Fall gab es keinen internen Übertrag von Bit 6 nach Bit 7, aber es trat ein externer Übertrag auf. Das Ergebnis ist falsch, weil sich Bit 7 geändert hat. Es sollte ein Überlauf angezeigt werden.

Ein Überlauf wird in vier Fällen auftreten:

- 1 – bei der Addition großer positiver Zahlen,

- 2 – bei der Addition großer negativer Zahlen,

- 3 – bei der Subtraktion einer großen positiven Zahl von einer großen negativen Zahl,

- 4 – bei der Subtraktion einer großen negativen Zahl von einer großen positiven Zahl.

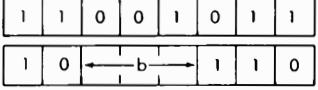

Wir wollen jetzt unsere Definition des Überlaufs verbessern:

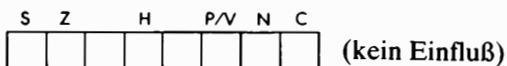

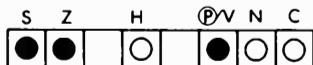

Der Überlaufanzeiger, ein spezielles Bit, das für diesen Zweck reserviert ist und „Flag“ genannt wird, wird gesetzt, wenn ein Übertrag von Bit 6 nach Bit 7 auftritt und kein externer Übertrag vorliegt oder wenn kein Übertrag von Bit 6 nach Bit 7 auftritt, aber ein externer Übertrag vorliegt. Dies zeigt an, daß Bit 7, d. h. das Vorzeichenbit des Ergebnisses, fehlerhaft geändert wurde. Für den technisch erfahrenen Leser: Das Überlauf-Flag wird gesetzt durch eine Exklusiv-Oder-Verknüpfung des Übertragseingangs und des Übertragsausgangs von Bit 7 (dem Vorzeichenbit). Praktisch jeder Mikroprozessor verfügt über ein spezielles Überlauf-Flag, um diesen Fall anzuzeigen, der berichtigt werden muß.

Ein Überlauf zeigt an, daß das Ergebnis einer Addition oder Subtraktion mehr Bits zur Darstellung belegt, als in dem üblichen Acht-Bit-Register zur Verfügung stehen.

### *Der Übertrag und der Überlauf*

Das Übertrags- und das Überlaufbit werden „Flags“ genannt. Sie stehen in jedem Mikroprozessor zur Verfügung, und im nächsten Kapitel werden wir lernen, wie man sie zur effektiven Programmierung benutzt.

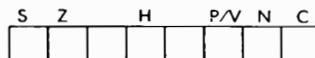

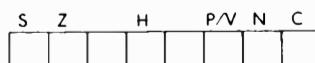

Diese beiden Anzeiger liegen in einem speziellen Register, das man Flag- oder „Statusregister“ nennt. Dieses Register enthält noch weitere Anzeiger, deren Funktion im Kapitel 4 erklärt wird.

### *Beispiele*

Wir wollen jetzt das Arbeiten von Übertrags- und Überlaufbit in konkreten Beispielen veranschaulichen. In jedem Beispiel kennzeichnet V den Überlauf und C den Übertrag.

Trat kein Überlauf auf, ist V = 0. Trat ein Überlauf auf, ist V = 1 (entsprechend auch der Übertrag C). Beachten Sie, daß der Übertrag nach den Regeln für das Zweierkomplement nicht beachtet werden soll. (Ein mathematischer Beweis wird hier nicht angegeben.)

#### *Positiv-positiv*

$$\begin{array}{r}

00000110 \quad (+6) \\

+ 00001000 \quad (+8) \\

\hline

= 00001110 \quad (+14) \quad V:0 \quad C:0

\end{array}$$

(richtig)

#### *Positiv-positiv mit Überlauf*

$$\begin{array}{r}

01111111 \quad (+127) \\

+ 00000001 \quad (+1) \\

\hline

= 10000000 \quad (-128) \quad V:1 \quad C:0

\end{array}$$

Obiges Ergebnis ist falsch, da ein Überlauf auftrat.

(falsch)

#### *Positiv-negativ (Ergebnis positiv)*

$$\begin{array}{r}

0000100 \quad (+4) \\

+ 1111110 \quad (-2) \\

\hline

=(1) 0000010 \quad (+2) \quad V:0 \quad C:1 \text{ (nicht beachten)}

\end{array}$$

(richtig)

#### *Positiv-negativ (Ergebnis negativ)*

$$\begin{array}{r}

00000010 \quad (+2) \\

+ 11111100 \quad (-4) \\

\hline

= 11111110 \quad (-2) \quad V:0 \quad C:0

\end{array}$$

(richtig)

#### *Negativ-negativ*

$$\begin{array}{r}

11111110 \quad (-2) \\

+ 11111100 \quad (-4) \\

\hline

=(1) 11111010 \quad (-6) \quad V:0 \quad C:1 \text{ (nicht beachten)}

\end{array}$$

(richtig)

*Negativ-negativ mit Überlauf*

$$\begin{array}{r}

10000001 \quad (-127) \\

+ \quad 11000010 \quad (-62) \\

\hline

=(1) \quad 01000011 \quad (+67) \quad V:1 \quad C:1

\end{array}$$

(falsch)

Hier trat ein „Unterlauf“ auf, da zwei große negative Zahlen addiert wurden. Das richtige Ergebnis wäre  $-189$ , was zur Darstellung in acht Bit zu groß ist.

*Aufgabe 1.12:* Vervollständige die folgenden Additionen. Gib das Ergebnis an, den Übertrag C, den Überlauf V und ob das Ergebnis richtig ist.

$$\begin{array}{r}

10111111 \quad ( ) \\

+ 11000001 \quad ( ) \\

\hline

= \quad \quad \quad V: \quad C:

\end{array}

\quad

\begin{array}{r}

11111010 \quad ( ) \\

+ 11111001 \quad ( ) \\

\hline

= \quad \quad \quad V: \quad C:

\end{array}$$

richtig  falsch

richtig  falsch

$$\begin{array}{r}

00010000 \quad ( ) \\

+ 01000000 \quad ( ) \\

\hline

= \quad \quad \quad V: \quad C:

\end{array}$$

$$\begin{array}{r}

01111110 \quad ( ) \\

+ 00101010 \quad ( ) \\

\hline

= \quad \quad \quad V: \quad C:

\end{array}$$

richtig  falsch

richtig  falsch

*Aufgabe 1.13:* Kann man ein Beispiel angeben, bei dem bei der Addition einer positiven und einer negativen Zahl ein Überlauf auftritt? Warum?

*Festkomma-Darstellung*

Jetzt wissen wir, wie man vorzeichenbehaftete ganze Zahlen darstellt. Das Problem der Größe haben wir jedoch noch nicht gelöst. Wollen wir größere ganze Zahlen darstellen, benötigen wir mehrere Bytes. Um arithmetische Operationen effektiv auszuführen, ist es notwendig, eine feste Zahl von Bytes zu verwenden, keine variable. Wenn aber die Zahl der Bytes einmal festgelegt ist, ist auch die maximale Größe der Zahlen, die man darstellen kann, festgelegt.

*Aufgabe 1.14:* Was sind die größte und die kleinste Zahl, die man in zwei Byte mit Zweierkomplementen darstellen kann?

*Das Problem der Größe*

Bei der Addition von Zahlen haben wir uns auf acht Bit beschränkt, weil der Prozessor, den wir verwenden wollen, intern jeweils acht Bit gleichzeitig verarbeitet. Dies beschränkt uns jedoch auf Zahlen im Bereich von  $-128$  bis  $+127$ . Für viele Anwendungen reicht das natürlich nicht aus. Mehrfache Genauigkeit wird verwendet, um die Stellenzahl, die dargestellt werden kann, zu erhöhen. Dann kann ein Zwei-, Drei- oder

N-Byte-Format verwendet werden. Wir wollen als Beispiel ein „doppeltgenaues“ 16-Bit Format untersuchen:

|          |          |             |

|----------|----------|-------------|

| 00000000 | 00000000 | ist „0“     |

| 00000000 | 00000001 | ist „1“     |

| 01111111 | 11111111 | ist „32767“ |

| 11111111 | 11111111 | ist „-1“    |

| 11111111 | 11111110 | ist „-2“    |

*Aufgabe 1.15:* Was ist die größte negative ganze Zahl, die in dreifachgenauem Format als Zweierkomplement dargestellt werden kann?

Diese Methode bringt jedoch auch Nachteile mit sich. Wenn man beispielsweise zwei Zahlen addiert, muß man sie generell in Stücken zu acht Bit addieren. Dies wird in Kapitel 3 (Grundlegende Techniken der Programmierung) erklärt werden. Das führt zu langsamere Verarbeitung. Außerdem belegt diese Darstellung für jede Zahl 16 Bit, selbst wenn sie mit nur acht Bit dargestellt werden könnte. Es ist deshalb üblich, 16 oder vielleicht 32 Bit zu verwenden, aber selten mehr.

Wir wollen den folgenden wichtigen Punkt bedenken: Welche Zahl von Bit  $n$  für die Darstellung als Zweierkomplement auch immer gewählt wird, sie ist dann festgelegt. Wenn als Ergebnis oder bei irgendeiner Zwischenrechnung eine Zahl herauskommt, die länger als  $n$  Bit ist, gehen einige Bit verloren. Das Programm rettet normalerweise die  $n$  Bit links (die wichtigsten) und läßt die Bits von niedrigerer Ordnung weg. Dies nennt man Abschneiden des Ergebnisses.

Hier ist ein Beispiel im Dezimalsystem, bei dem eine sechsstellige Darstellung verwendet wird:

$$\begin{array}{r}

12345 \ 6 \\

\times \quad 1,2 \\

\hline

24691 \ 2 \\

123456 \\

\hline

=148147,2

\end{array}$$

Das Ergebnis benötigt sieben Stellen! Die „,2“ nach dem Komma fällt heraus und das Endergebnis ist 148147. Es wurde abgeschnitten. Solange die Position des Kommas nicht verloren geht, wendet man üblicherweise diese Methode an, um den Zahlenbereich für die Rechnungen auf Kosten der Genauigkeit zu erweitern.

Im Dualsystem ist das Problem das gleiche. Die Einzelheiten der dualen Multiplikation werden in Kapitel 4 gezeigt.

Die Darstellung in festem Format kann einen Genauigkeitsverlust verursachen, aber sie wird für übliche Berechnungen und mathematische Operationen ausreichen.

Leider ist bei der Buchhaltung kein Verlust an Genauigkeit tragbar. Wenn zum Beispiel die Registrierkasse einem Kunden eine große Sum-